Making method for low on-resistance power VDMOS transistor

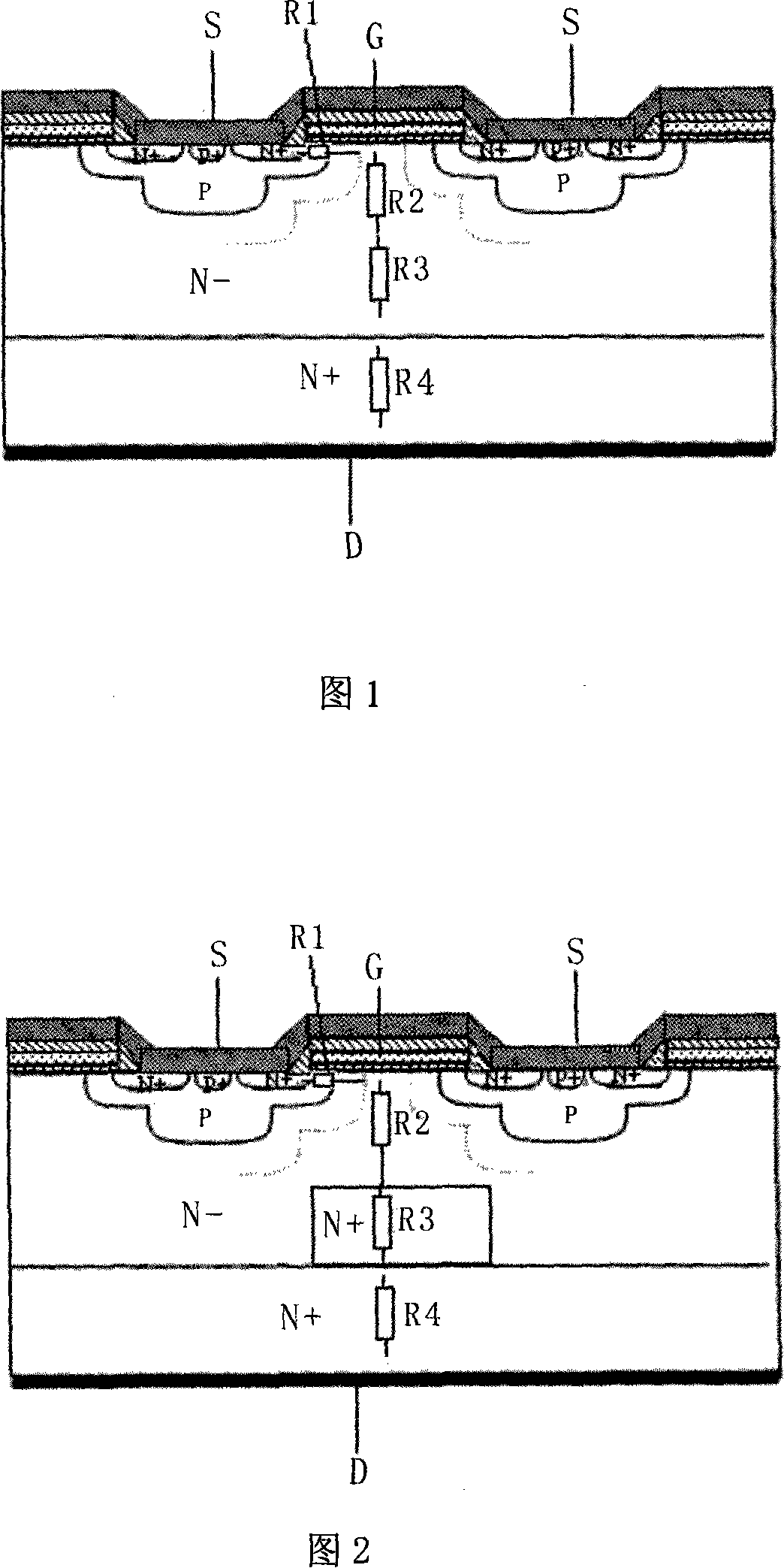

A technology of low on-resistance and manufacturing method, which is applied in the manufacture of low on-resistance power MOS transistors and the manufacture of low on-resistance power VDMOS transistors. R3 and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The specific embodiments of the present invention are not limited to the following description. The method of the present invention will be further described below in conjunction with the accompanying drawings.

[0031] The manufacturing method of the low on-resistance power VDMOS transistor of the present invention includes the following steps:

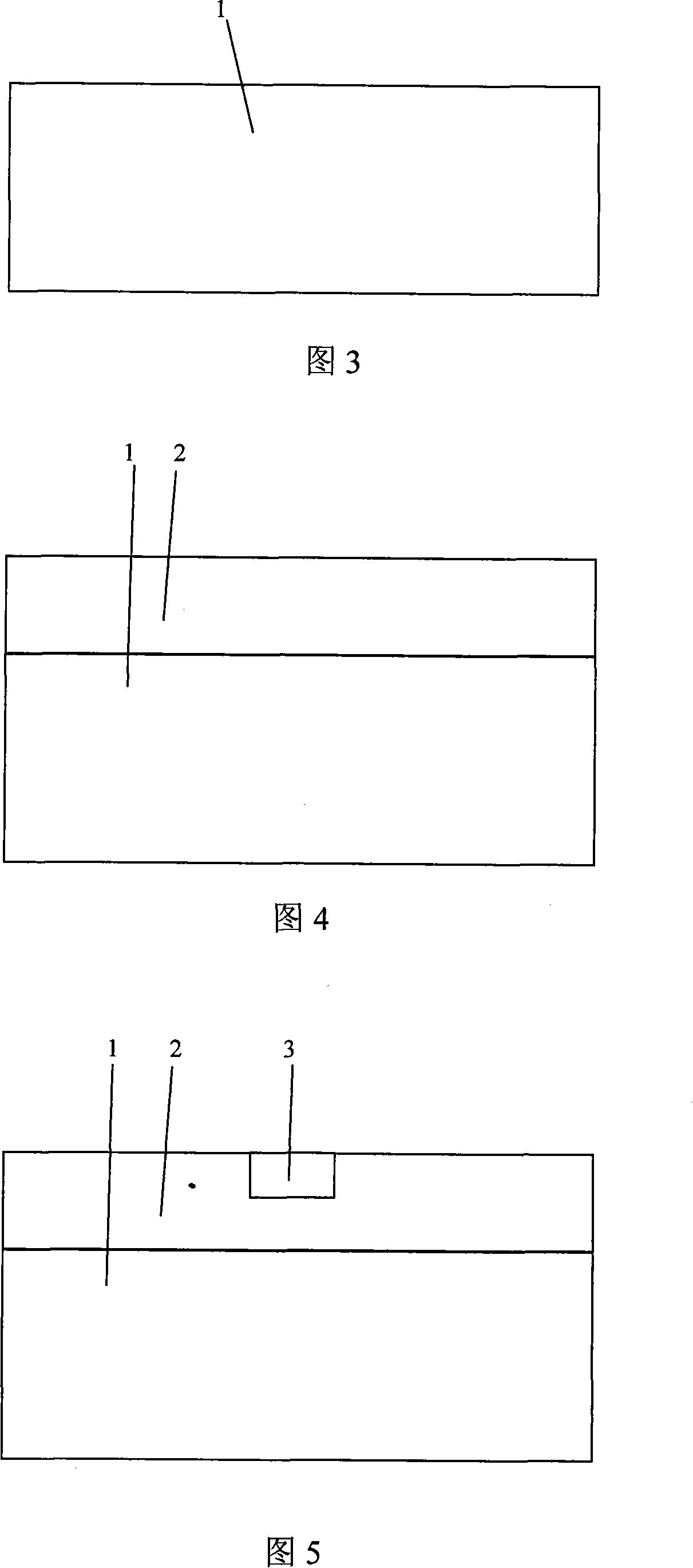

[0032]1. Prepare a 4-inch silicon single crystal with a resistivity of 0.0008-0.002Ω·cm and a thickness of 400-450μm with a P type crystal orientation as N + Silicon substrate sheet 1, as shown in Figure 3. After cleaning, in N + The epitaxial layer 2 with a thickness of 4-5 μm is grown on the silicon wafer, as shown in FIG. 4, and its resistivity is determined according to the breakdown voltage of the specific VDMOS tube. For a 100V breakdown VDMOS tube, the resistivity is usually 5-7Ω·cm.

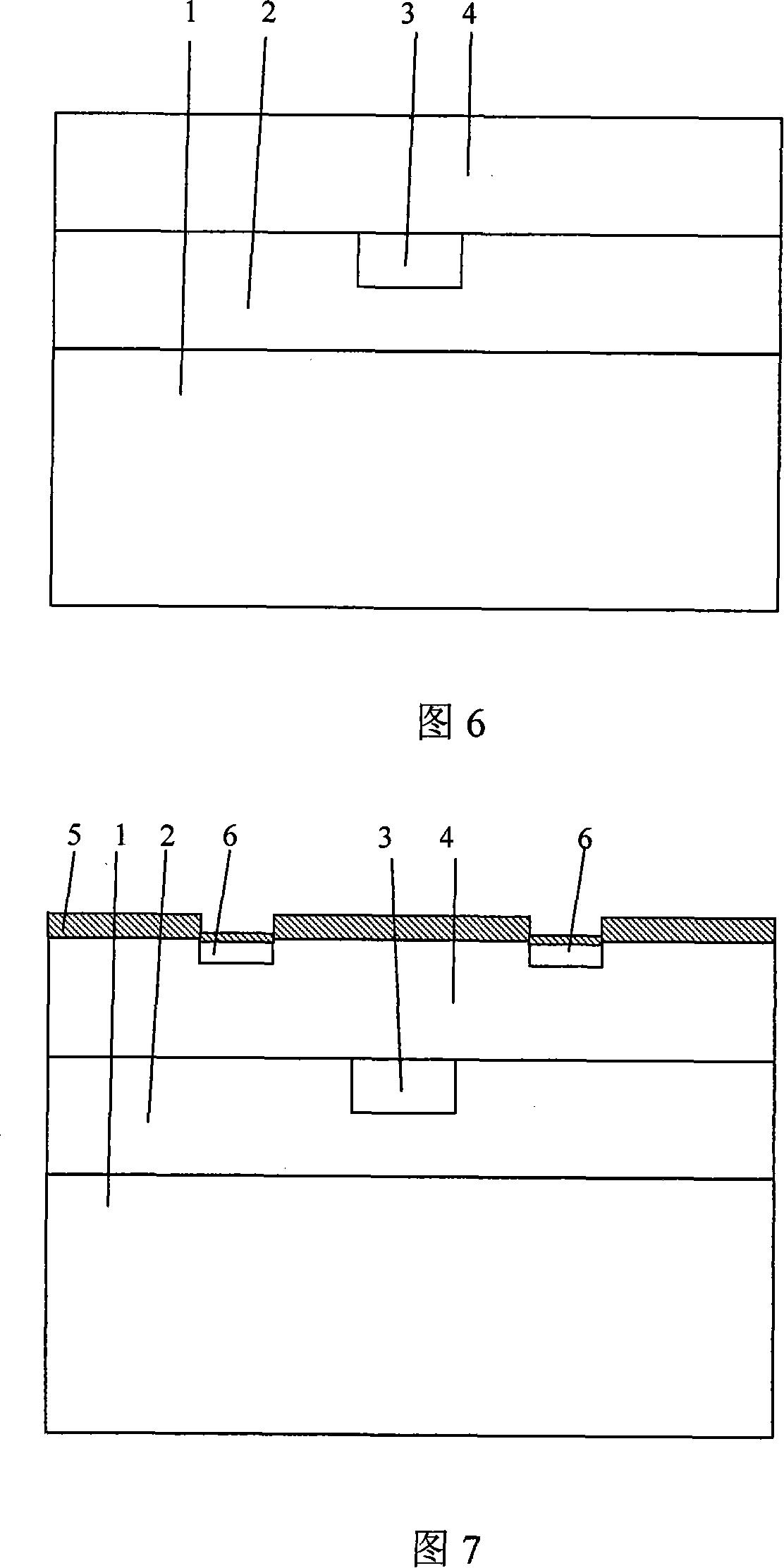

[0033] 2. After cleaning, grow SiO with a thickness of 950-1050nm 2 Layer; N required for photolithography + After cleaning, grow SiO with ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More