MOS transistor radio frequency circuit simulated macro model and its parameter extraction method

A technology of MOS transistors and radio frequency circuits, which is used in electrical digital data processing, special data processing applications, instruments, etc., and can solve problems such as unsatisfactory performance effects.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The MOS transistor radio frequency circuit simulation macro model and its parameter extraction method of the present invention will be further described in detail below.

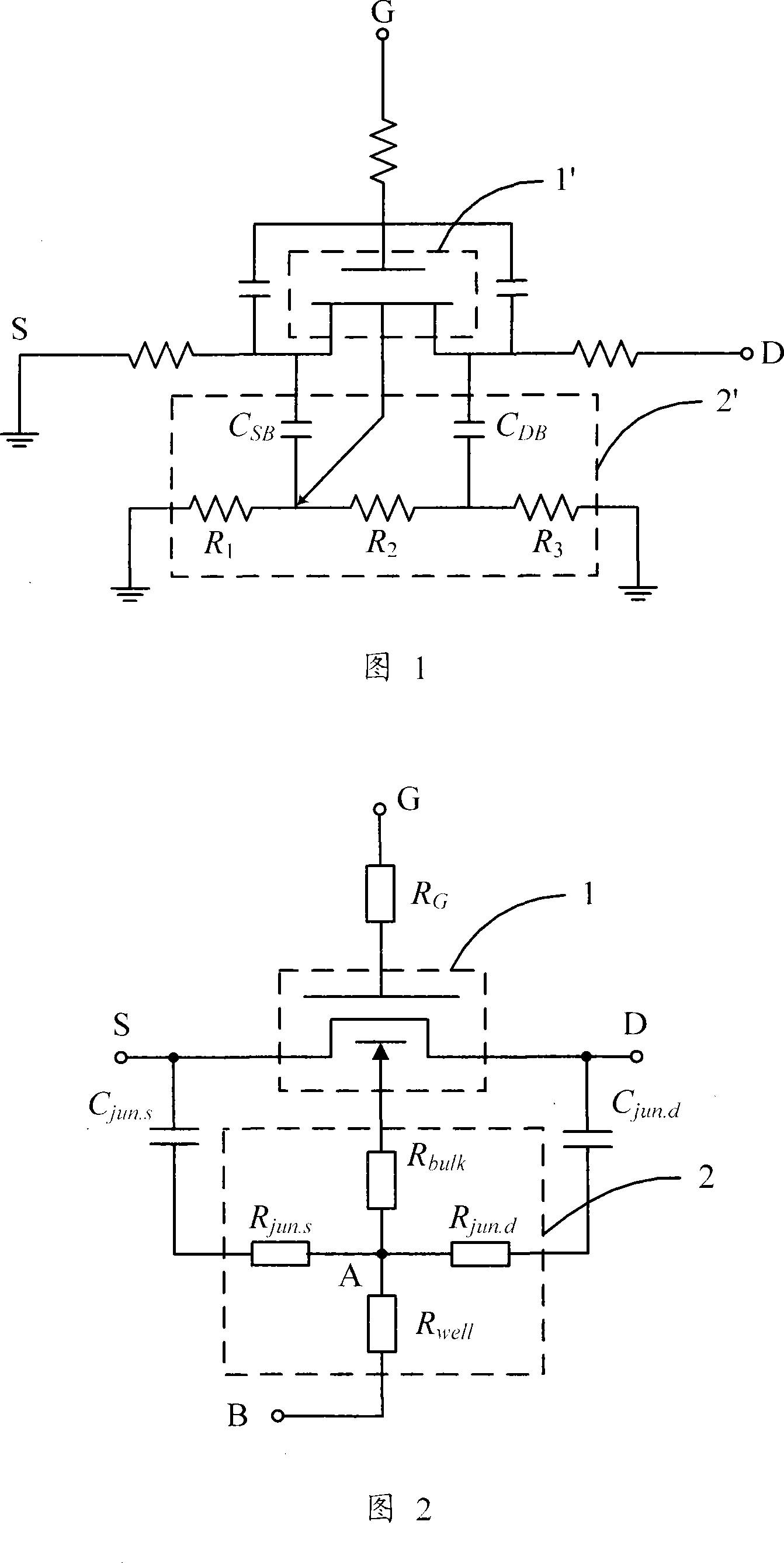

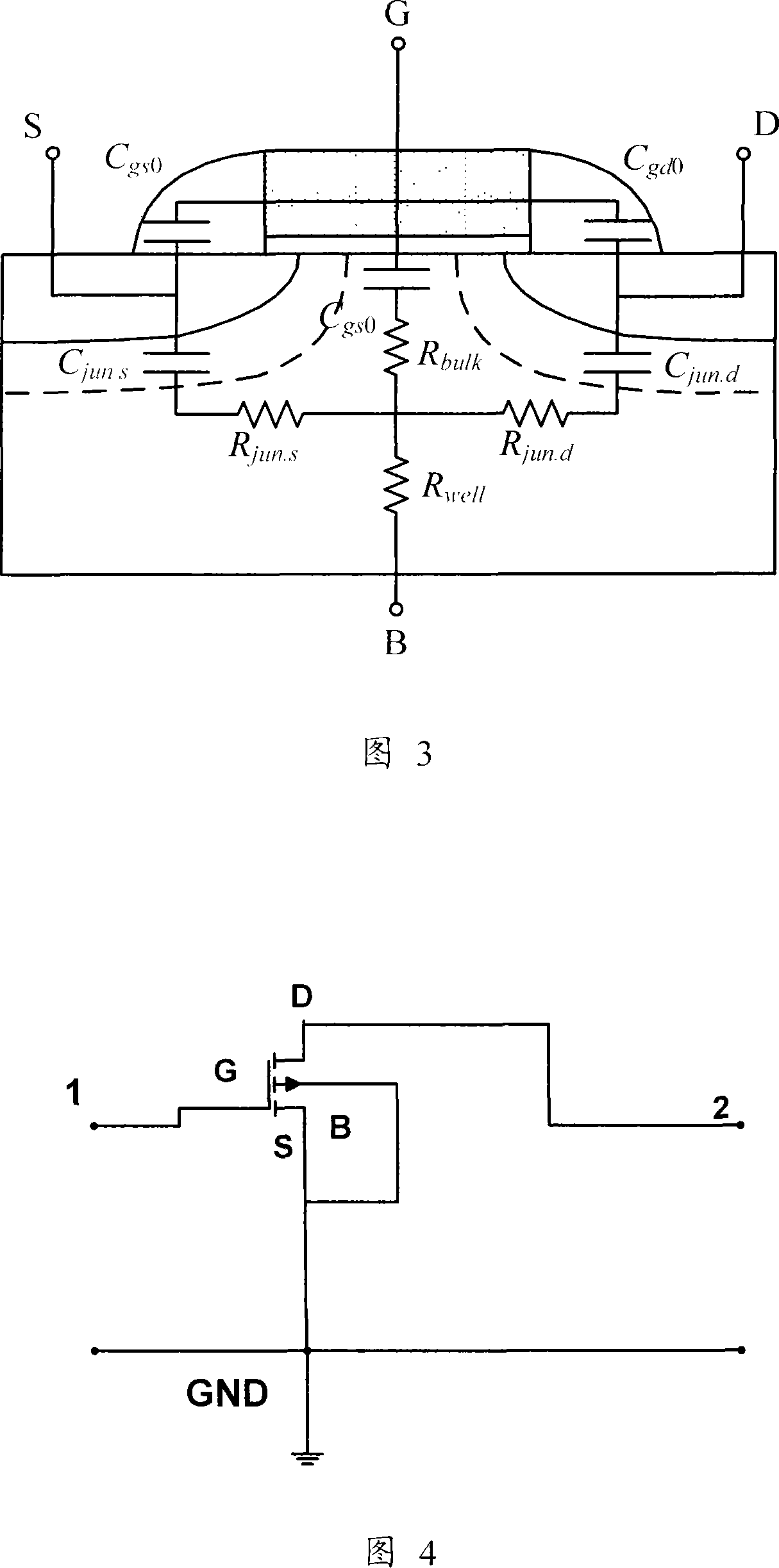

[0032] As shown in FIG. 2 , the present invention utilizes a MOS transistor radio frequency circuit simulation macro model to simulate a MOS transistor radio frequency circuit, and the simulation circuit has a gate node G, a source node S, a drain node D and a substrate node B. The MOS transistor radio frequency circuit simulation macro model includes a MOS transistor simulation model 1, a MOS transistor gate connected in series with the simulation circuit gate node G, used to characterize the gate resistance R between the transistor gate and the contact hole electrode G , the source junction capacitance C used to characterize the junction capacitance and parasitic resistance between the source and substrate jun.s with the first substrate resistance R jun.s , the drain junction capacitance C used to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More