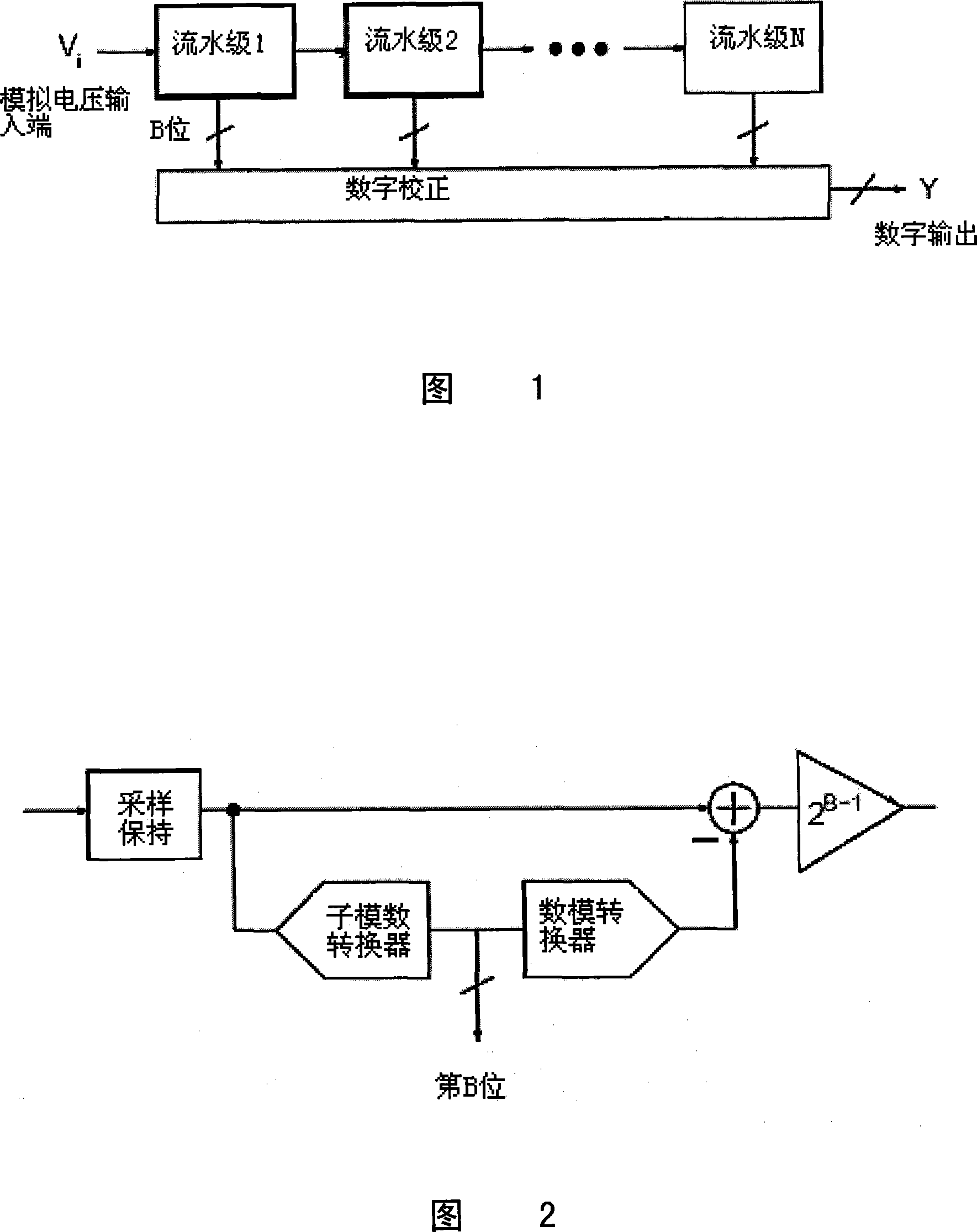

A forward error compensation and correction method and device for streamline analog/digital converter

An analog-to-digital converter and forward error technology, applied in the direction of analog/digital conversion calibration/testing, can solve problems such as limited application prospects, increase sampling frequency, solve bottlenecks in ADC resolution and speed, and be easy to expand Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

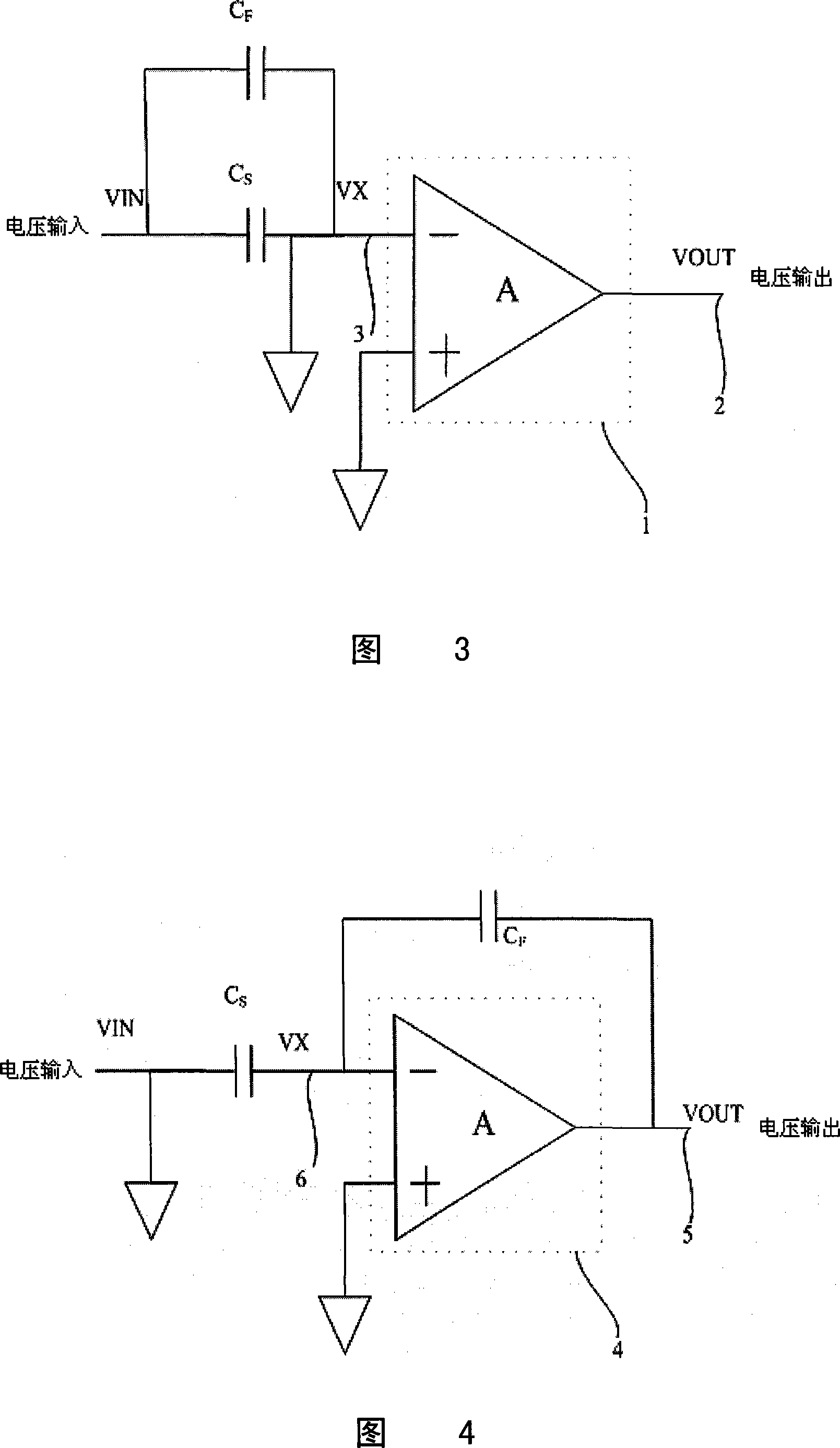

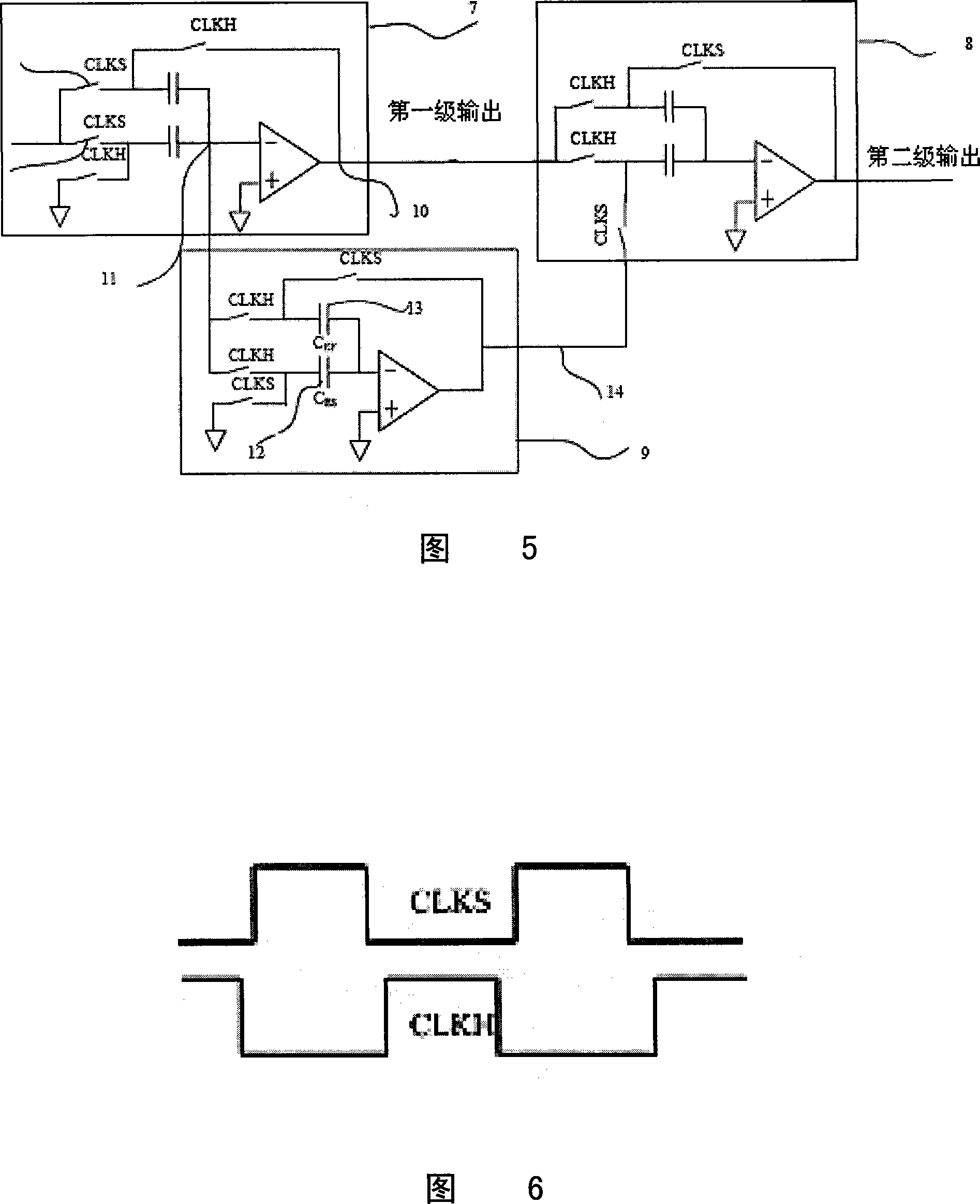

[0034] The present invention will be described in detail below through embodiments and in conjunction with the accompanying drawings.

[0035] As shown in Figures 3 and 4, the present invention proposes a new error correction method for pipelined ADCs—forward error compensation. The basic principle is as follows: when the sample-and-hold circuit in the pipeline stage is in the hold phase, the The voltage error will be reflected on the input virtual point 6 of the operational amplifier 4 .

[0036] The voltage value of the virtual point 6 can be approximated by the following method. During the sampling phase, the total charge on the input is:

[0037] Q S =(C F +C S )×VIN

[0038] C F : Holding capacitor of the sub-pipeline level

[0039] C S : The sampling capacitor of the sub-pipeline level

[0040] In the holding phase, the total charge input is:

[0041] Q h =C F (A×VX+VX)+C S VX

[0042] For 1-bit or 1.5-bit pipeline level, C is preferable S =C F , the volt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com