Method and system for single time slot numerically controlling attenuation

A digitally controlled attenuation and single-slot technology, applied in transmission systems, transmission control/equalization, electrical components, etc., can solve the problem of inability to reduce cell interference, failure to reach signal coverage, and increased power consumption of user terminal equipment, etc. problems, to achieve the effect of protecting normal operation, improving system stability, compatibility and anti-interference ability, and protecting against interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

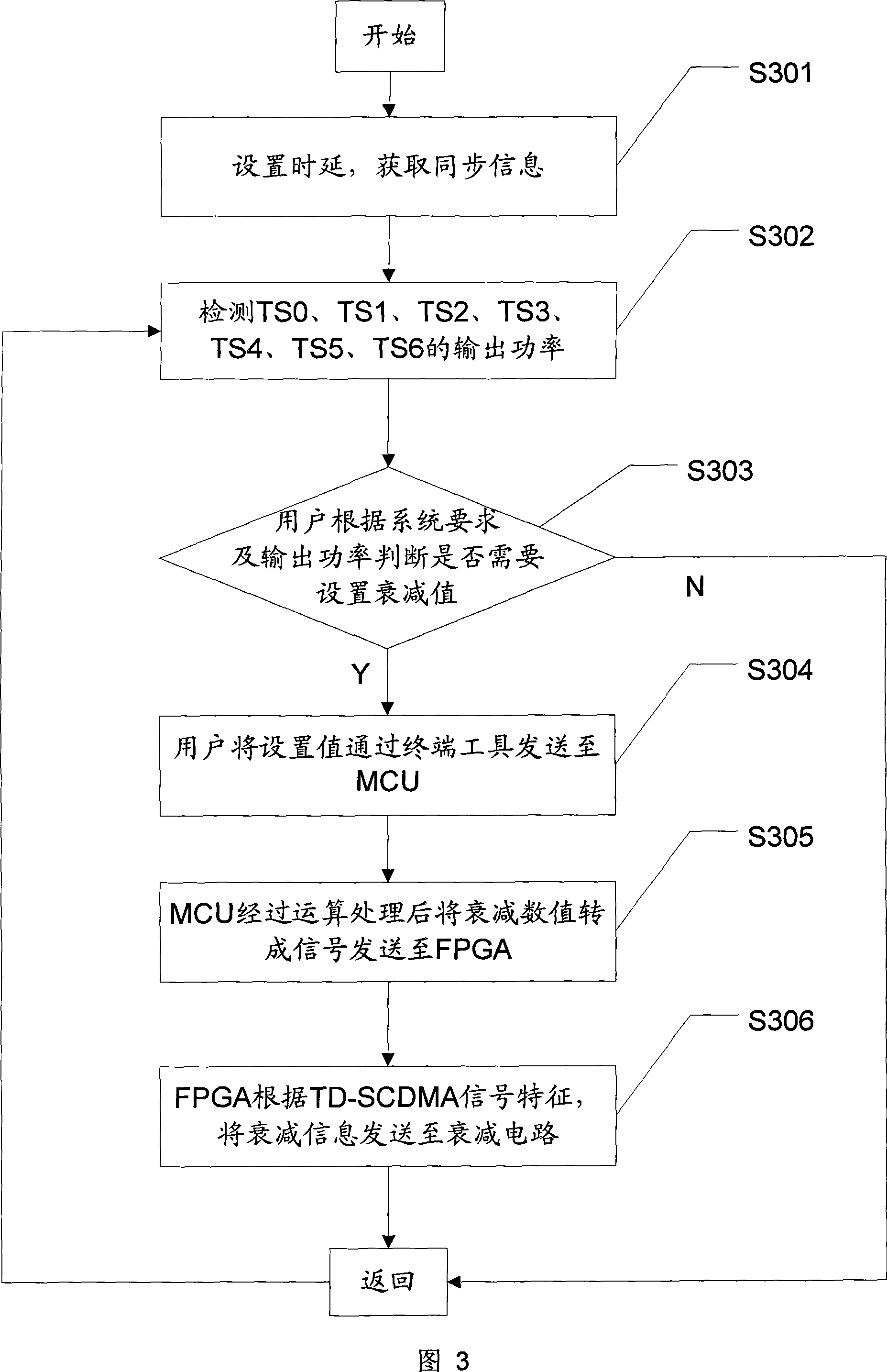

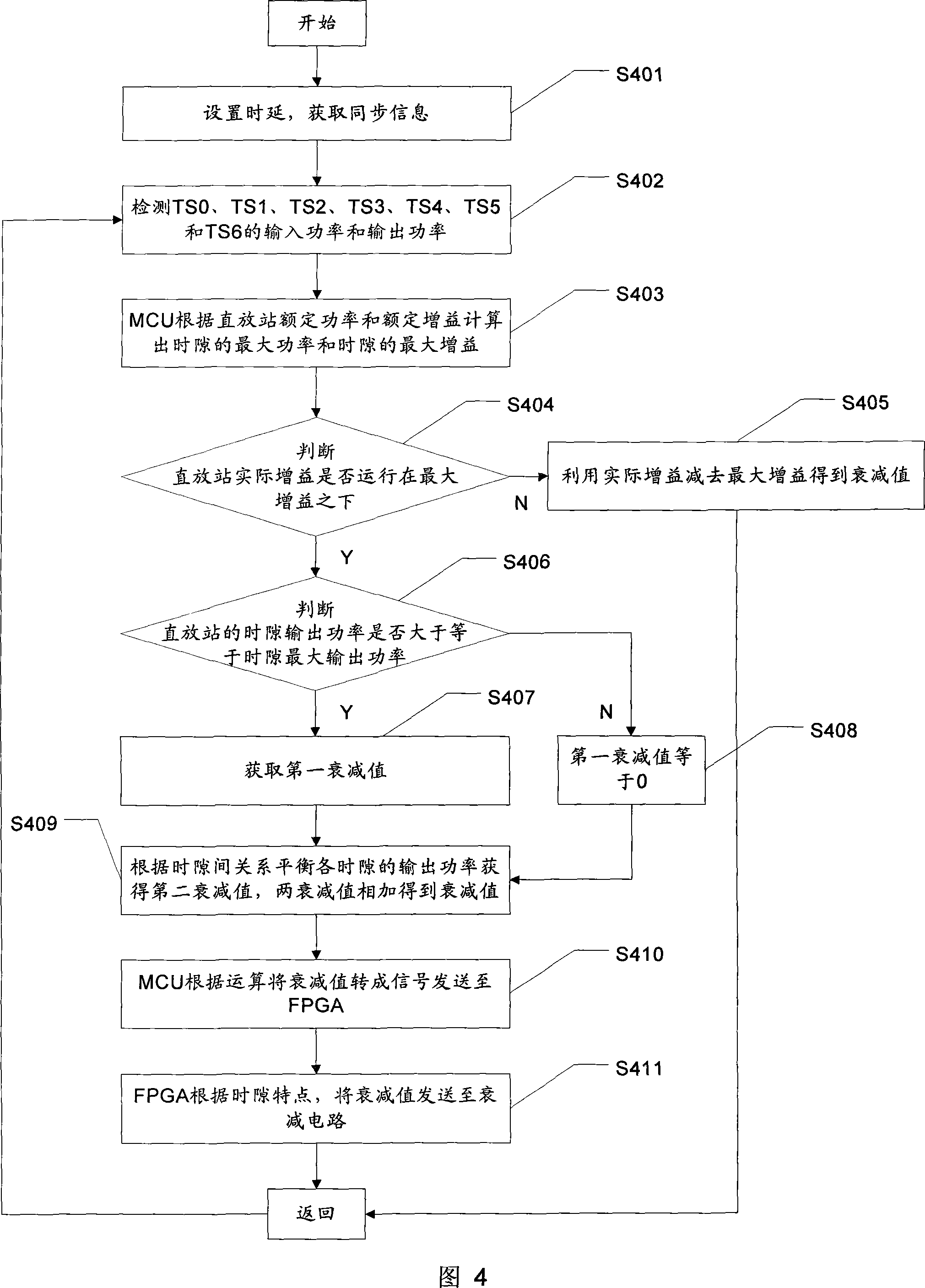

[0088] Step S301, setting a time delay, and obtaining synchronization information.

[0089] Step S302, detecting the output powers of TS0, TS1, TS2, TS3, TS4, TS5 and TS6.

[0090] The TD-SCDMA signal is provided by the RF module, and the sampling power intensity is obtained through ADC detection; because there is always a certain distance between the base station and the repeater link, and there is also a certain distance between the end user's mobile phone and the base station, we can monitor and set , which is transmitted to the FPGA of the synchronization module, and the FPGA compensates the delay control amount to ensure the accuracy of the link power detection value;

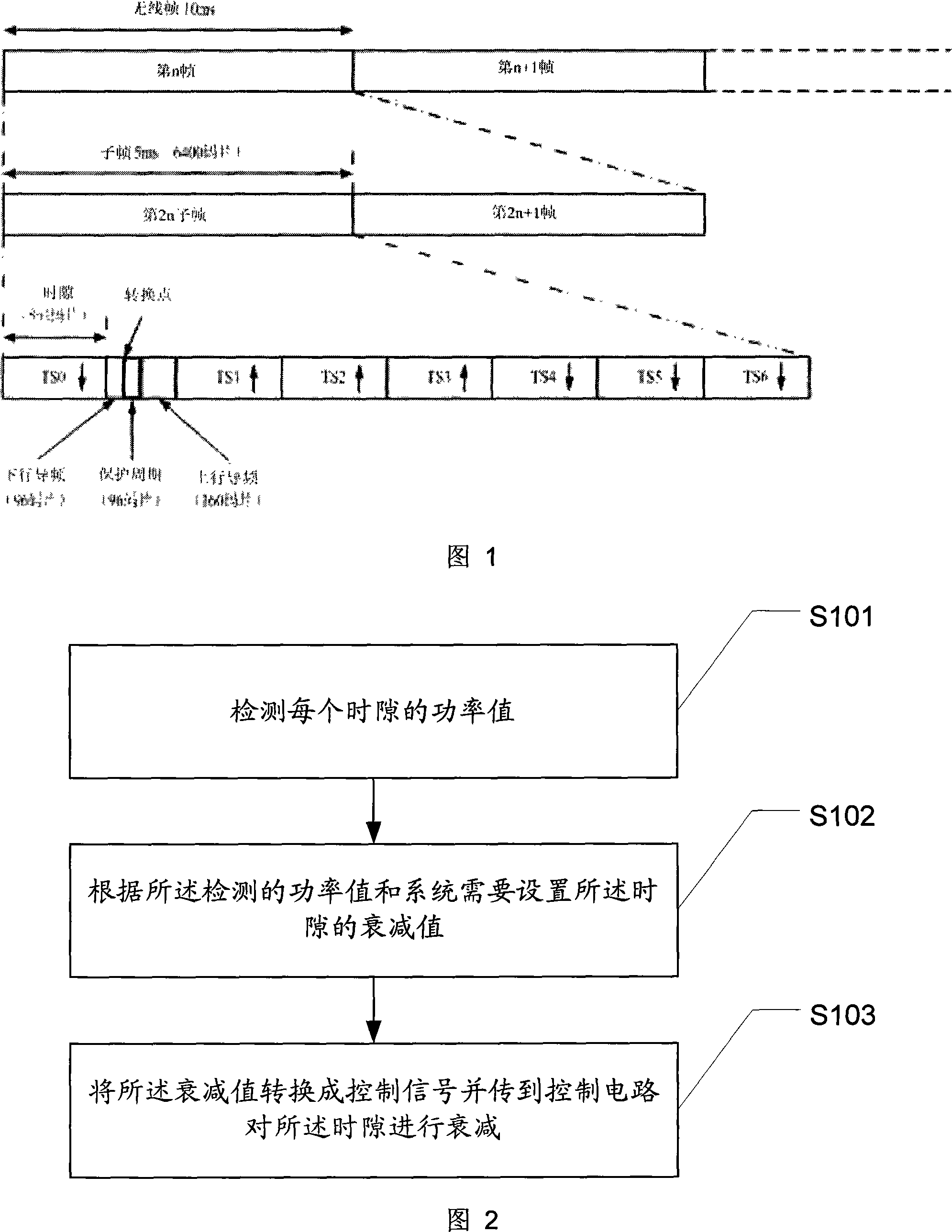

[0091] The synchronization control module FPGA finds out the uplink and downlink time slots, the position of the switching point and the position of the training sequence code of each time slot according to the power intensity provided by the ADC sampling and the time feature of TD-SCDMA, according to the ...

Embodiment 2

[0099] Step S401 , setting a time delay, and obtaining synchronization information.

[0100] Step S402, detecting the input power and output power of TS0, TS1, TS2, TS3, TS4, TS5 and TS6.

[0101] The TD-SCDMA signal is provided by the RF module, and the sampling power intensity is obtained through ADC detection; because there is always a certain distance between the base station and the repeater link, and there is also a certain distance between the end user's mobile phone and the base station, we can monitor and set , which is transmitted to the FPGA of the synchronization module, and the FPGA compensates the delay control amount to ensure the accuracy of the link power detection value.

[0102] The synchronization control module FPGA finds out the uplink and downlink time slots, the position of the switching point and the position of the training sequence code of each time slot according to the power intensity provided by the ADC sampling and the time characteristics of TD-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More