Grid making method

A manufacturing method and gate technology, applied in the field of gate manufacturing, can solve problems such as enhancement and incomplete etching, and achieve the effects of complete outline, improved reliability and product yield.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

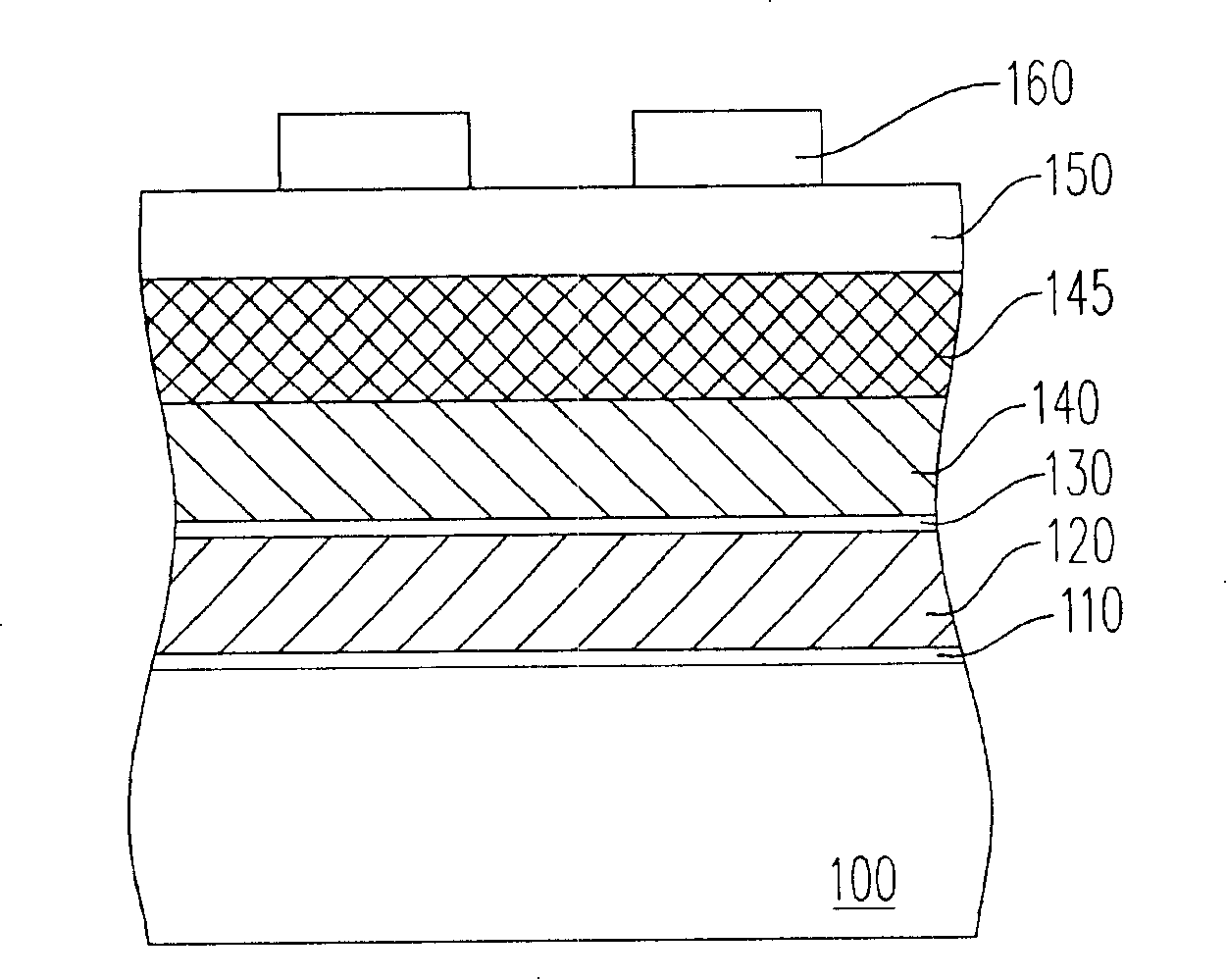

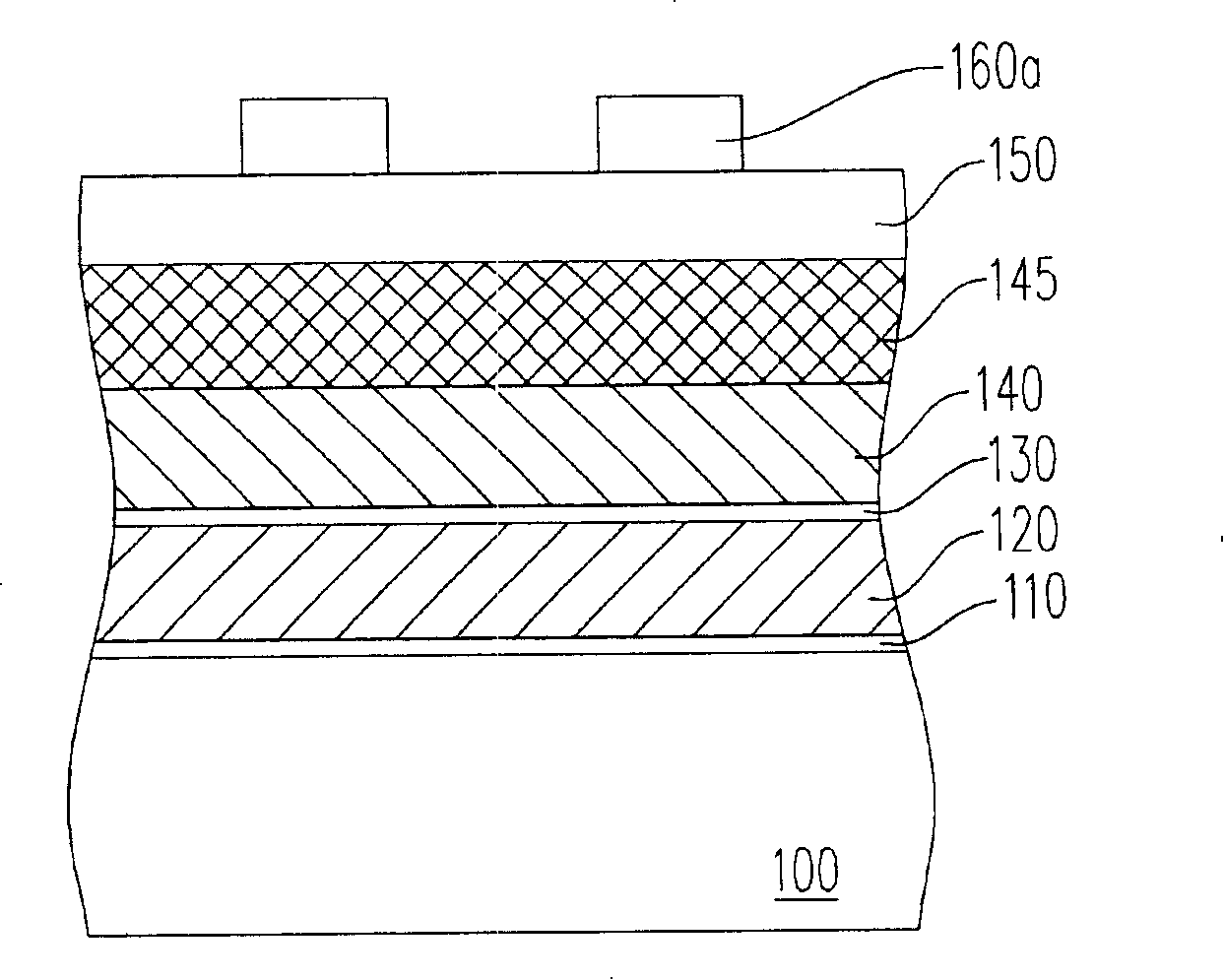

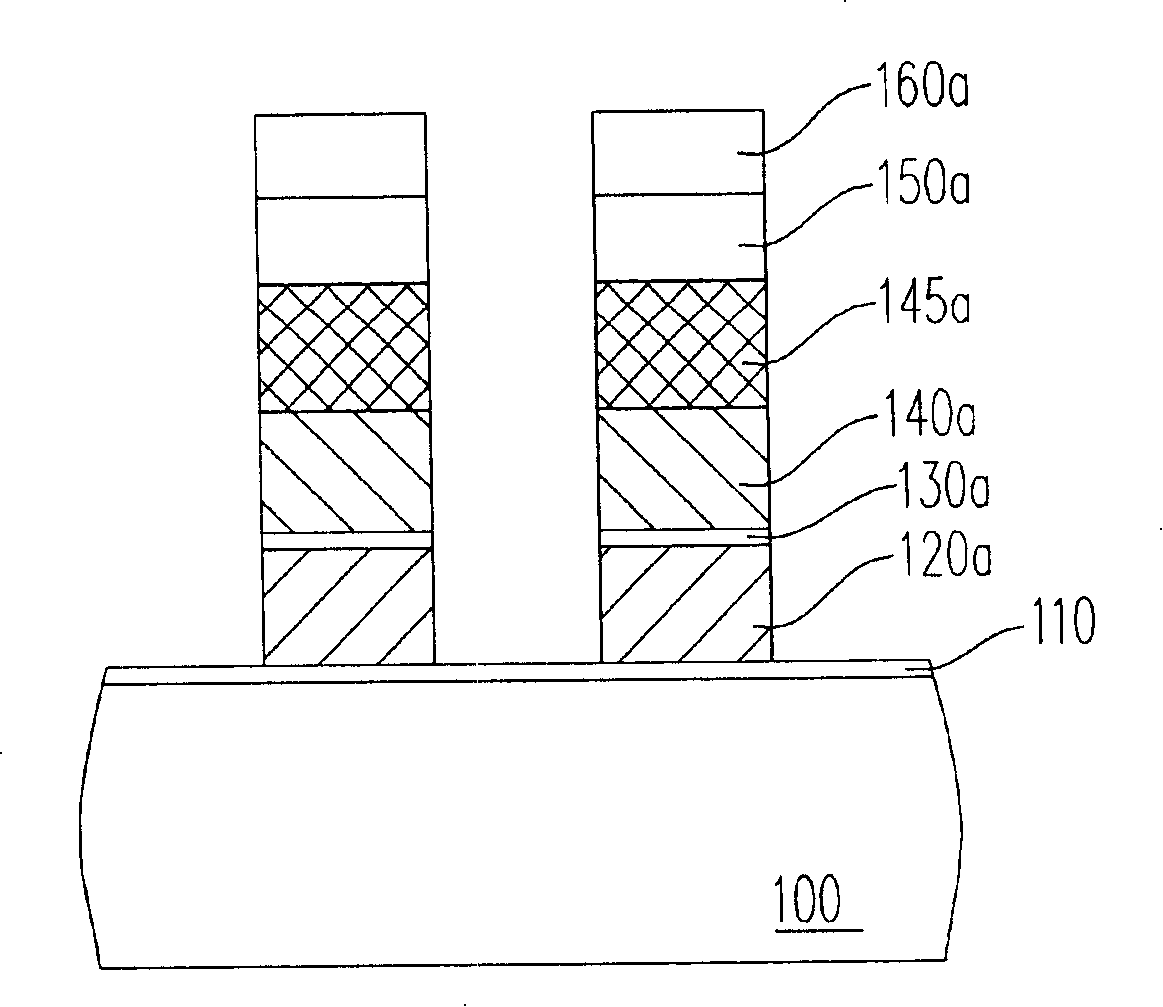

[0048] Figure 1A to Figure 1D It is a schematic cross-sectional view illustrating a manufacturing process of a gate according to an embodiment of the present invention.

[0049] Please refer to Figure 1A , the gate manufacturing method of this embodiment is applied in the manufacturing process of the memory element, of course, the present invention is not limited thereto. Firstly, a substrate 100 is provided, on which a tunnel dielectric layer 110 , a floating gate material layer 120 , an inter-gate dielectric layer 130 and a control gate material layer 140 have been sequentially formed.

[0050] Wherein, the material of the tunneling dielectric layer 110 is, for example, silicon oxide, and its formation method is, for example, thermal oxidation or chemical vapor deposition.

[0051] The material of the floating gate material layer 120 and the control gate material layer 140 is, for example, doped polysilicon, which is formed by, for example, using a chemical vapor depositi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More