Semiconductor packaging structure

A packaging structure and semiconductor technology, used in semiconductor devices, semiconductor/solid-state device components, electrical solid-state devices, etc., can solve the problems of through-silicon via technology potential not being fully utilized, and reduce stress, reduce The effect of connecting spacing, increasing feasibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

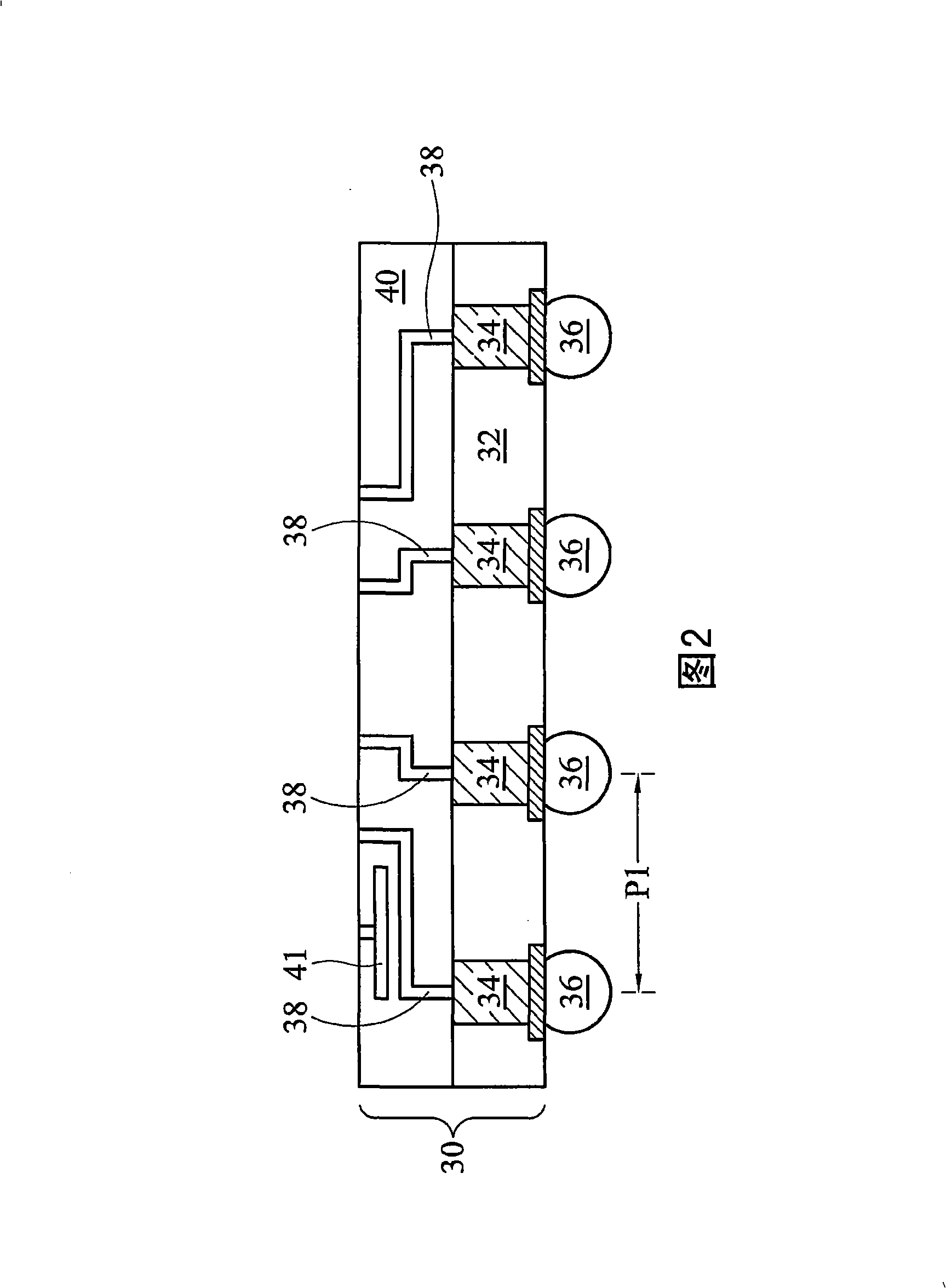

[0057] FIG. 2 shows interposer 30 . In a preferred embodiment, interposer 30 is a silicon-containing interposer including a silicon-containing substrate 32 . Preferably, the thickness of silicon-containing substrate 32 is less than about 750 μm, and more preferably less than 150 μm. In one embodiment, the substrate 32 includes commonly used materials, such as inorganic materials, organic materials, ceramics or multi-layer materials of the above materials. A semiconductor chip (also referred to as a die in the art) intended to be connected to the interposer 30 is usually formed on a silicon substrate. The coefficient of thermal expansion (CTE) of the silicon-containing interposer 30 is not much different from that of the semiconductor chip, so the stress caused by the mismatch of the coefficient of thermal expansion (CTE) can be significantly reduced. Furthermore, the existing silicon process technology can be used to form a silicon-containing interposer, which not only has h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com