Semiconductor package and manufacturing method thereof

A semiconductor and packaging technology, applied in the field of semiconductor packaging and its manufacturing method, can solve problems such as delamination and limited adhesion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

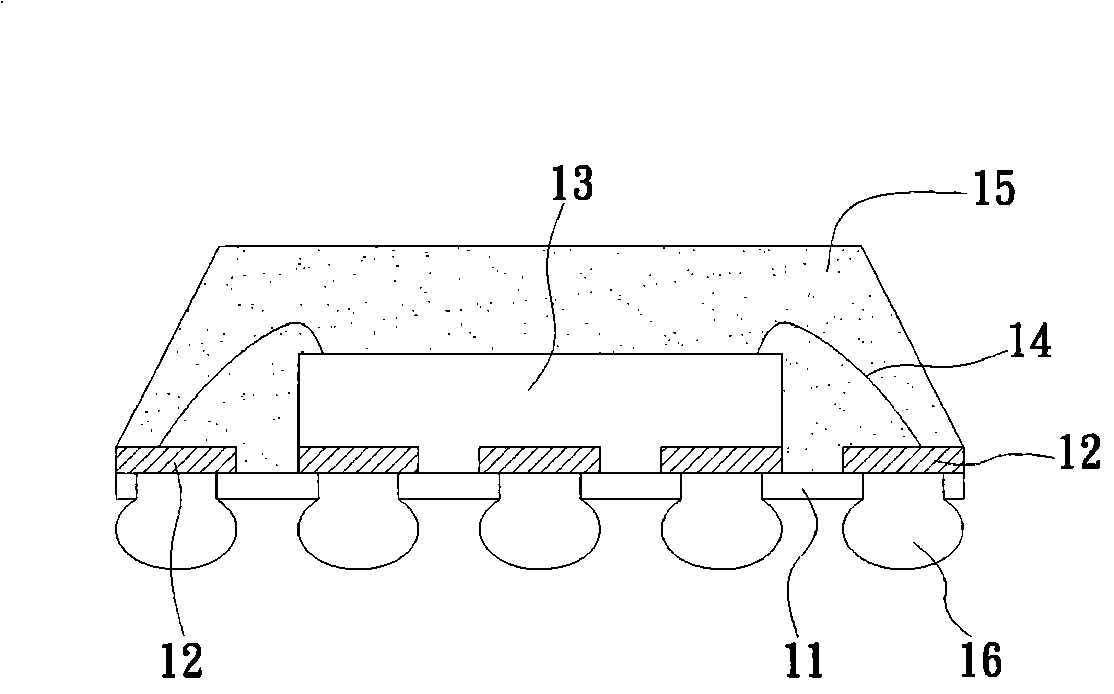

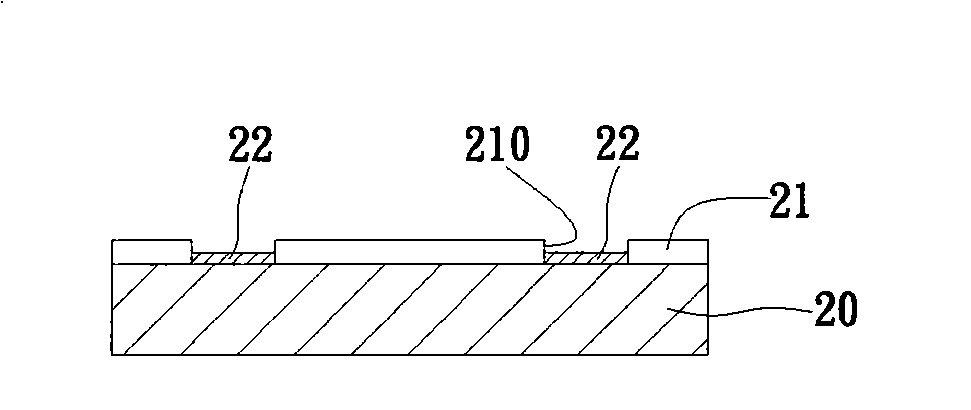

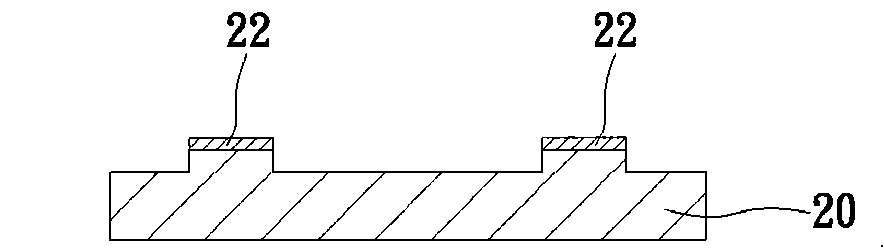

[0054] see Figure 4A to Figure 4G , is a schematic cross-sectional view of the first embodiment of the semiconductor package and its manufacturing method of the present invention.

[0055] Such as Figure 4A As shown, at first, prepare a carrier plate 40 (for example, copper plate (CuPlate)) of a metal material, and cover the first resistance layer 41 on a surface of the metal carrier plate 40, and make the first resistance layer 41 form how many times A first opening 410 is used to define a subsequent terminal position 41a for electrical connection with the semiconductor chip and a die pad position 41b for placing the semiconductor chip.

[0056] Such as Figure 4B As shown, an electroplating process is performed to form a metal block 42 in the first opening 410 by electroplating, and its material is copper, for example.

[0057] Such as Figure 4C As shown, the first resistance layer 41 is removed, and the second resistance layer 43 is covered on the metal carrier 40, a...

no. 2 example

[0067] see Figure 5A to Figure 5G , is a schematic diagram of a second embodiment of the semiconductor package and its manufacturing method of the present invention. The semiconductor package and its manufacturing method of this embodiment are roughly the same as those of the foregoing embodiments, the main difference being that when forming a metal block on the metal carrier, the metal block is in the shape of multiple columns, and a metal layer covering the multiple columns is formed. The metal layer on the outer surface of the block, so that when the metal carrier and the metal block are subsequently removed, a groove with a protruding metal layer can be formed on the surface of the encapsulant, thereby increasing the number of conductive elements subsequently planted in the groove The contact area and bonding force with the metal layer.

[0068] Such as Figure 5A As shown, a metal carrier 50 is prepared, and a first resistance layer 51 is covered on a surface of the me...

no. 3 example

[0076] see again Figure 6 , is a schematic diagram of the third embodiment of the semiconductor package of the present invention.

[0077]The semiconductor package of this embodiment is substantially the same as the previous embodiment, the main difference is that after the metal block is formed on the metal carrier, when the metal layer covering the metal block is to be formed, the second resistive layer is added compared with the previous embodiment. Two opening sizes, so as to form a metal layer 64 covering the metal block on the metal carrier, and at the same time form an extension part 640, for subsequent completion of chip placement, wire bonding, packaging and molding operations, and remove the metal carrier and the metal block, the metal layer 64 can be formed on the bottom surface and the side of the groove 670 on the surface of the encapsulant 67, and the metal layer extension 640 can be formed on the surface of the encapsulant 67 around the groove 670, thereby incr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More