Semiconductor device, wafer coarse alignment mark and coarse alignment method

A semiconductor, rough alignment technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc. Mark precision alignment failure and other problems to achieve the effect of improving the success rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

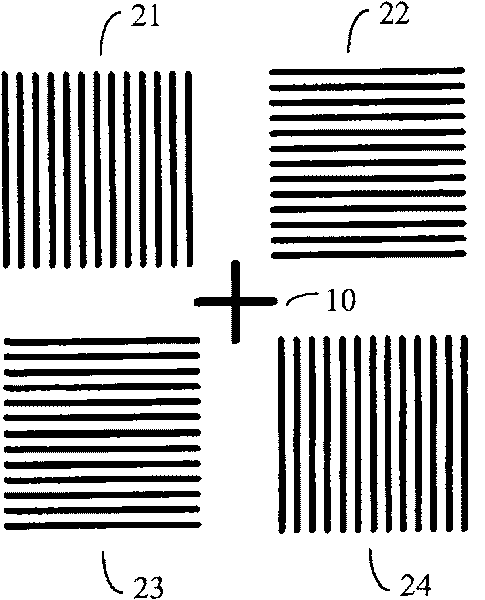

[0033] The structure of the rough alignment mark of the semiconductor device, the rough alignment mark of the wafer and the rough alignment method of the present invention is similar to that of the alignment mark used for the calibration of the lithography device. The alignment marks are exposed, developed and etched at the same time in the previous process, so they are well coupled with the fine alignment marks in the lithography device. Therefore, the rough wafer alignment marks of the above scheme can improve the precision alignment of the lithography device. The success rate of finding fine alignment marks during the process.

[0034] The semiconductor device, the rough alignment mark of the wafer and the rough alignment method of the present invention are described in detail through the preferred embodiments, so that the rough alignment mark of the wafer and the rough alignment method of the present invention are more clear.

[0035] refer to figure 1 As shown, the rough...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More