Stress buffering package for a semiconductor component

A stress buffer, semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., can solve problems such as the influence of electronic circuits, and achieve the effect of reducing the surface area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

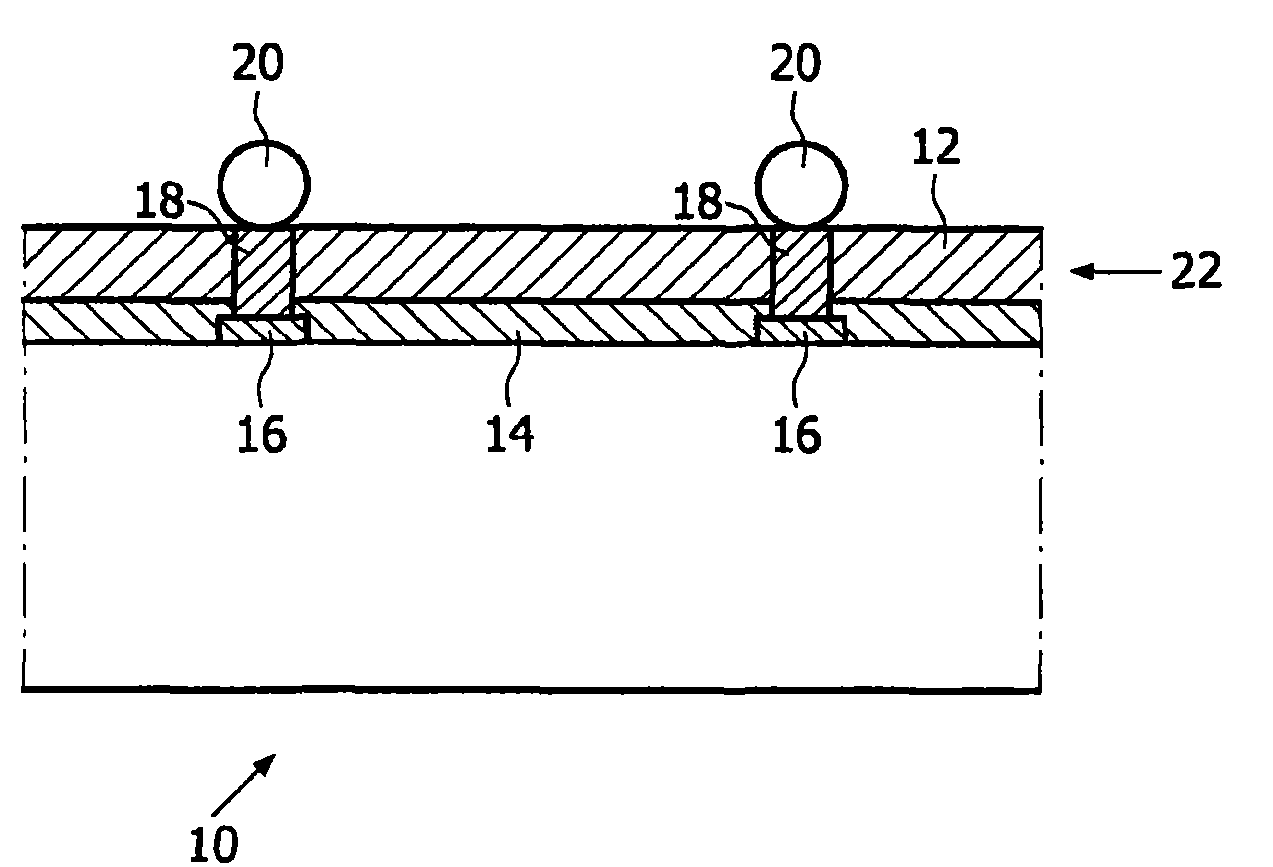

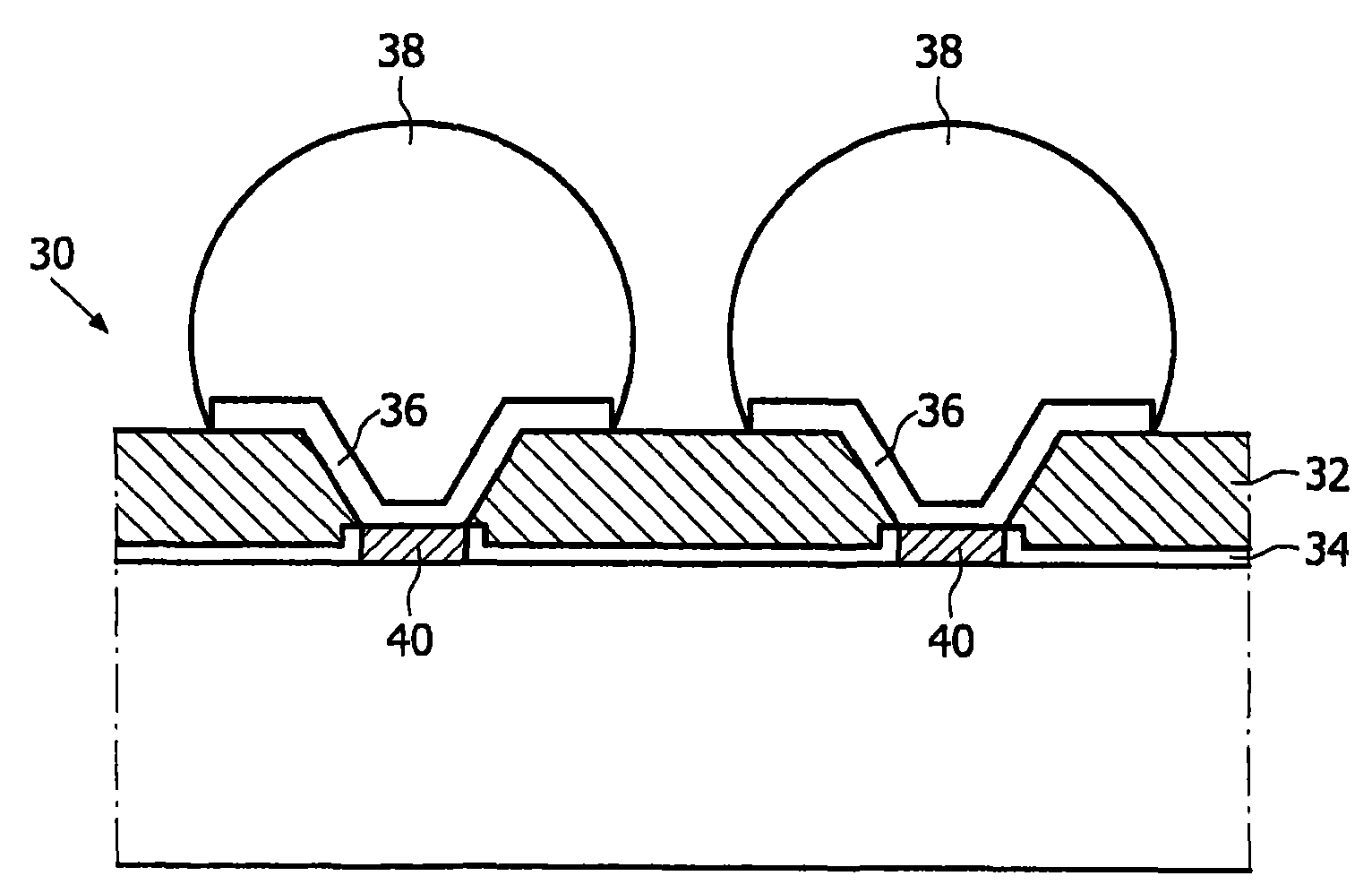

[0037] figure 1 with 2 An encapsulation according to the prior art is shown, discussed above.

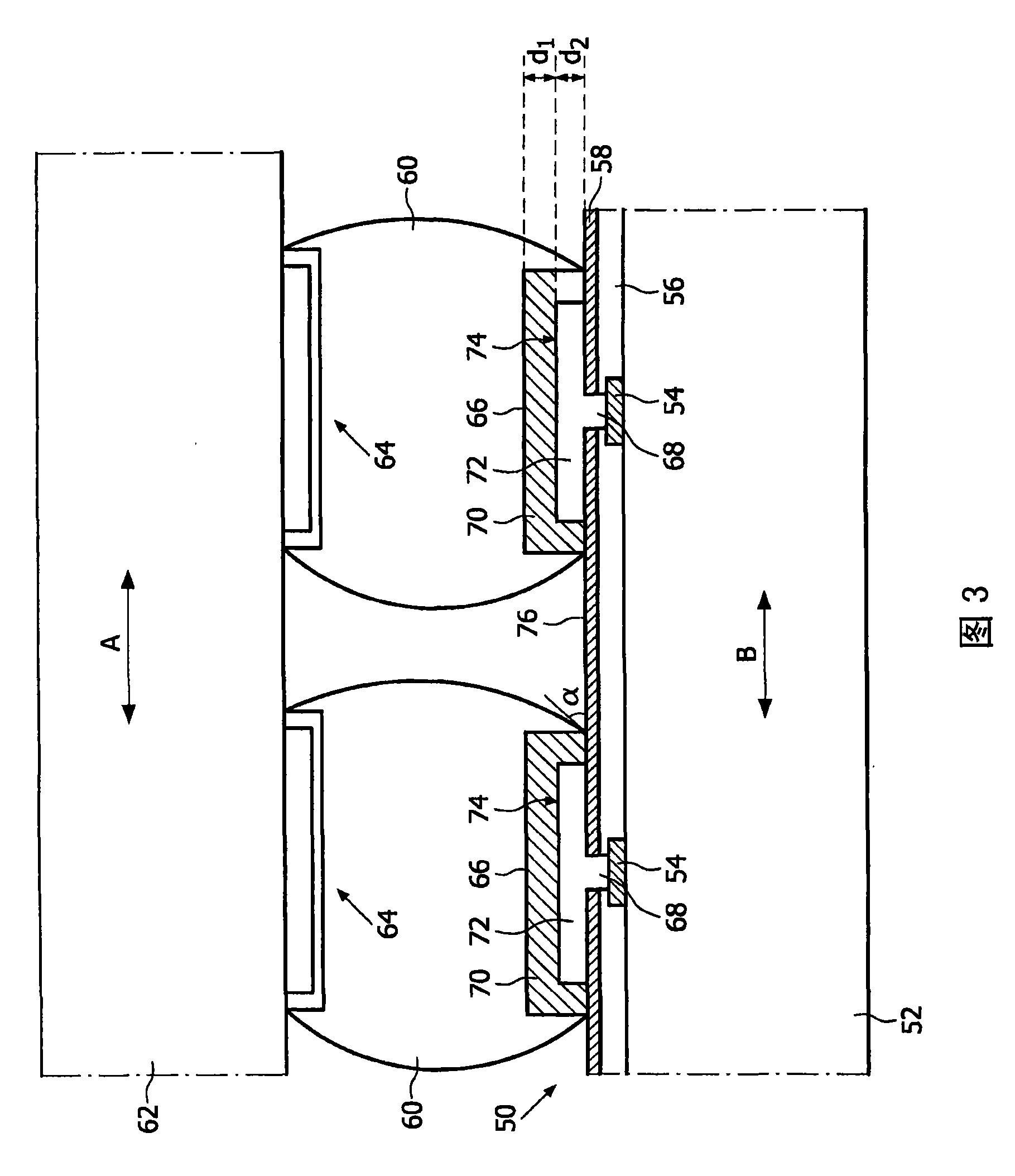

[0038] FIG. 3 shows a stress buffer package 50 for a semiconductor 52 including a plurality of I / O pads 54 on its upper surface. The semiconductor also includes a passivation layer 56 that protects the active regions of the semiconductor and exposes the I / O pads. Preferably, the passivation layer comprises silicon oxide. An additional passivation layer 58 of silicon nitride is usually applied on the passivation layer 56 .

[0039] The function of the solder balls 60 is to electrically connect the semiconductor 52 or another electrical component to the end of the board 62 where the electrodes 64 are disposed. The I / O pads and solder balls are electrically connected through the underball metallization 70 and the stress buffer element 74 . The outer surface of the under-ball metallization 70 forms a so-called bond pad 66, which makes it possible to place a solder ball.

[0040] E...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| elastic modulus | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More