Chip encapsulation substrate assembly and chip encapsulation construct

A chip packaging and substrate technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of pin and chip bump peeling, insufficient bonding strength between pins and chip bumps, and decreased manufacturing yield. Improve package yield and reliability, prevent pin stripping, and increase contact area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

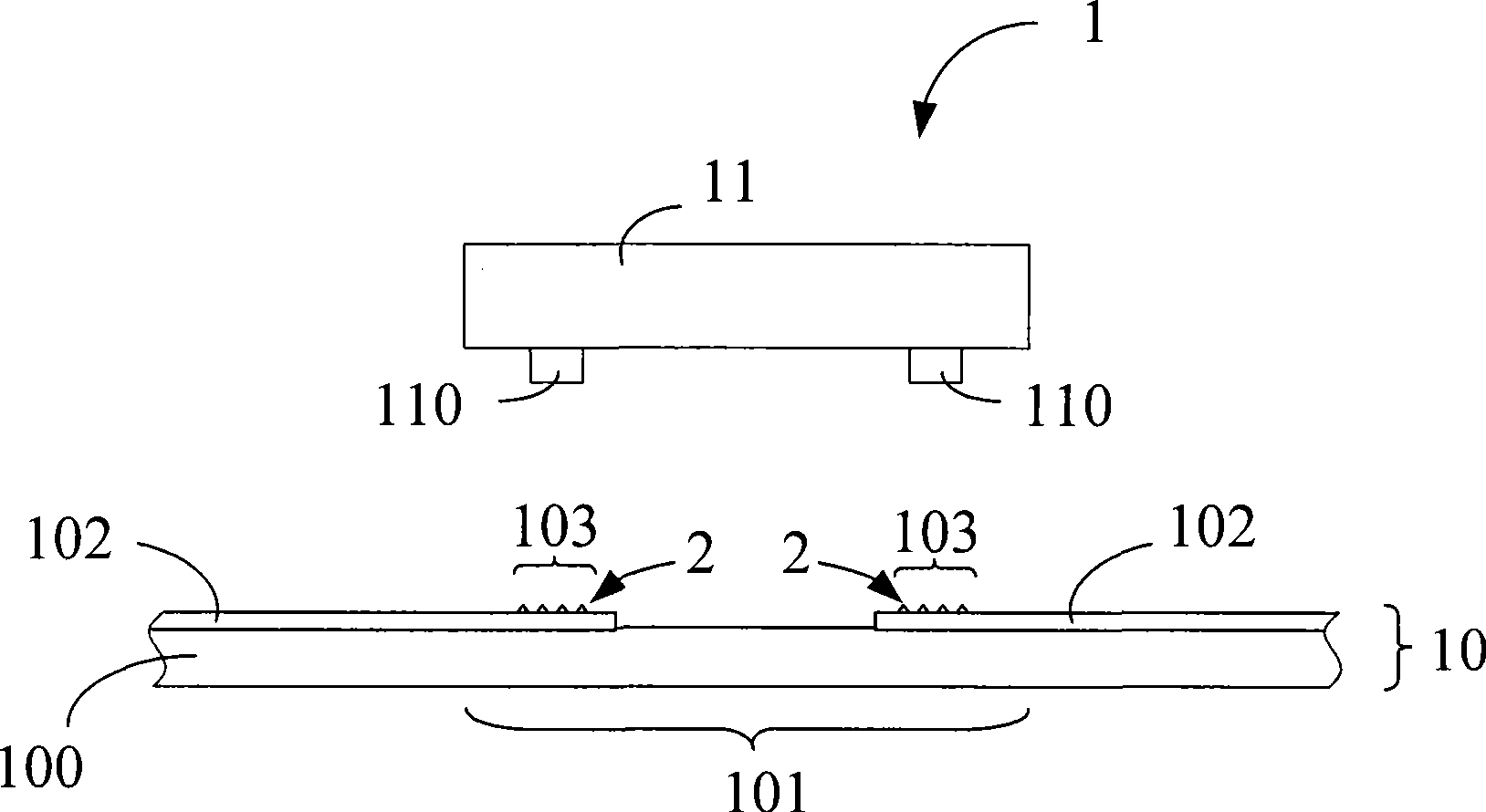

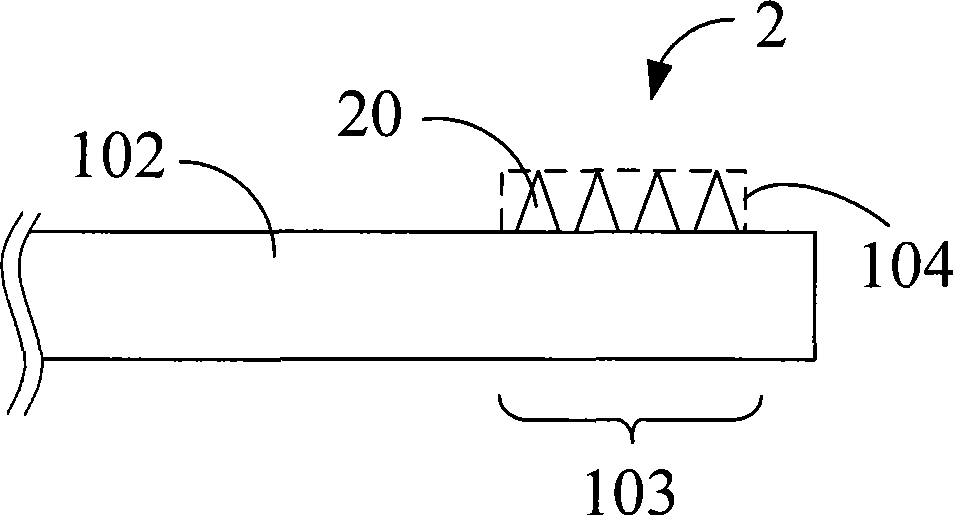

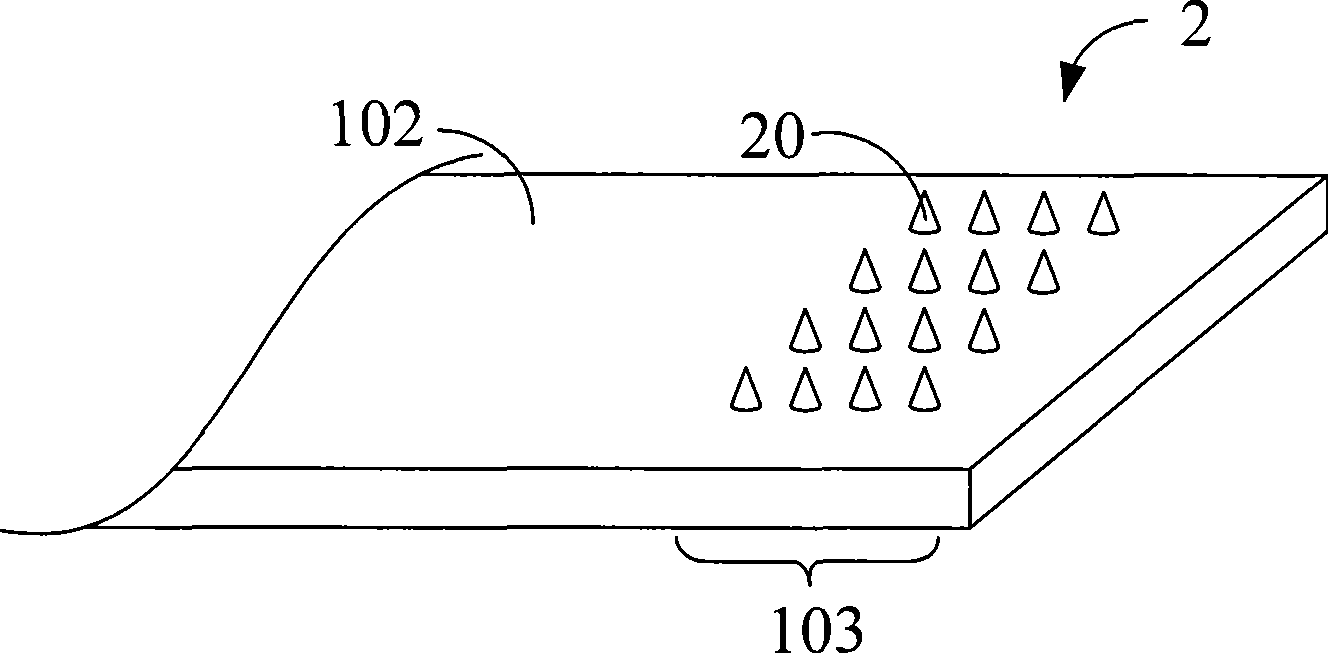

[0028] The first embodiment of the present invention is a chip packaging structure 1, and its cross-sectional view is as follows figure 1 shown. The chip packaging structure 1 includes a chip packaging substrate assembly 10 and a chip 11 . The chip package substrate assembly 10 includes a flexible dielectric layer 100 and a plurality of pins 102 . In practical applications, the chip package structure 1 can be a tape carrier package (TapeCarrier Package, TCP) or a chip-on-film package (Chip-On-Film, COF).

[0029] A chip bonding area 101 is defined on the flexible dielectric layer 100 . The flexible dielectric layer 100 can be an organic dielectric film layer made of materials such as polyimide (PI) or polyethylene terephthalate (PET). With the organic dielectric film layer, the pins 102 can be fixed on the chip packaging substrate assembly 10 , and the pins 102 can be electrically isolated.

[0030] In this embodiment, the pin 102 is made of a material with high conductivi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More