Method for manufacturing semiconductor substrate, semiconductor device and electronic device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, circuits, etc., can solve problems such as low heat resistance, reduced performance of semiconductor elements, and increased threshold voltage value, so as to reduce lattice defects, The effect of improving flatness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

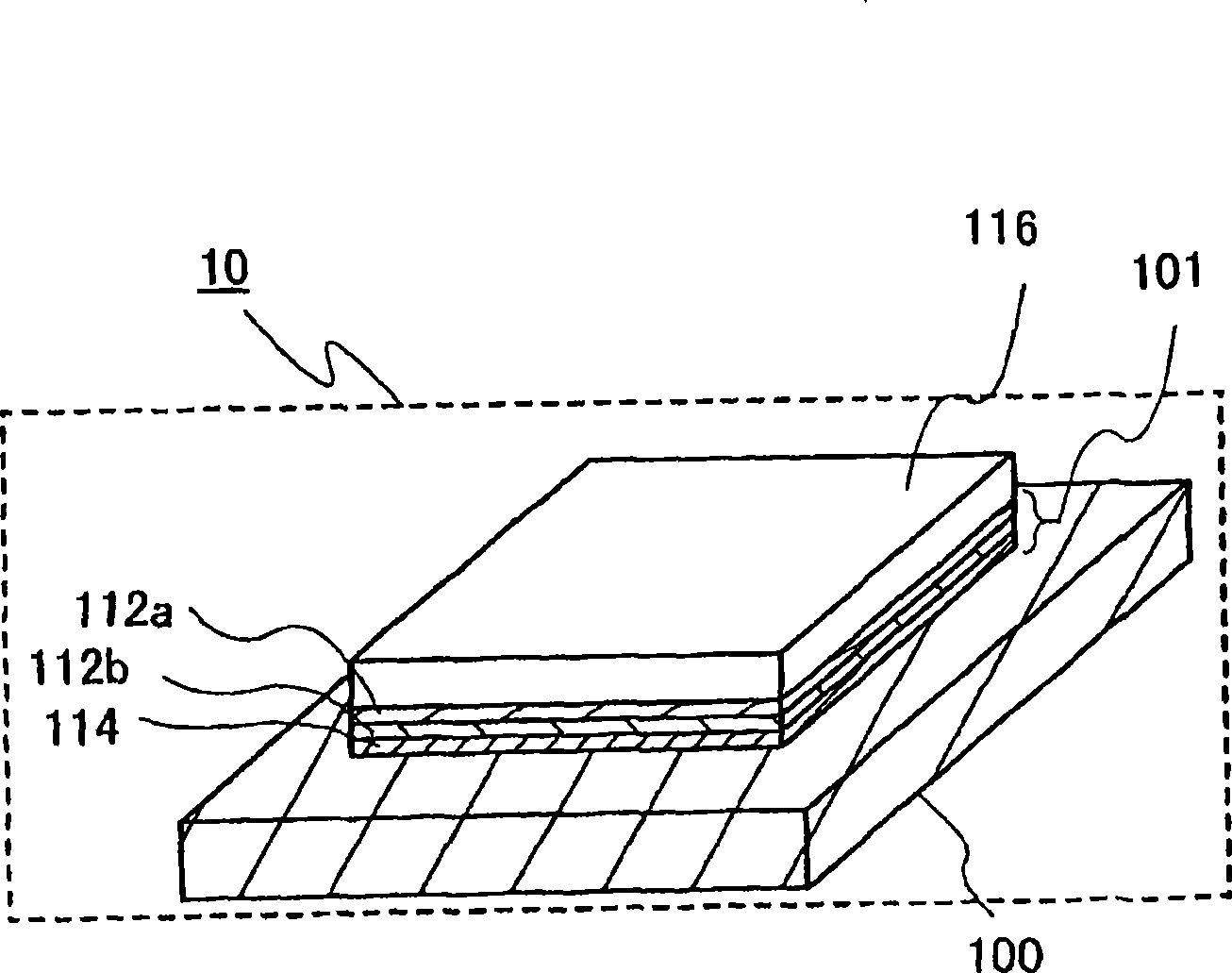

[0079] figure 1 is a perspective view showing a structural example of a semiconductor substrate. In the semiconductor substrate 10 , a single crystal semiconductor layer 116 is attached to the support substrate 100 . The single crystal semiconductor layer 116 is provided on the supporting substrate 100 via the buffer layer 101, and the semiconductor substrate 10 is a substrate having a so-called SOI structure in which a single crystal semiconductor layer is formed on an insulating layer.

[0080] The buffer layer 101 may have a single crystal structure or a multilayer structure in which two or more films are laminated. In this embodiment, the buffer layer 101 has a three-layer structure in which a bonding layer 114 , an insulating film 112 b , and an insulating film 112 a are laminated from the support substrate 100 side. The bonding layer 114 is formed of an insulating film. In addition, the insulating film 112a is an insulating film serving as a barrier layer. The barrie...

Embodiment approach 2

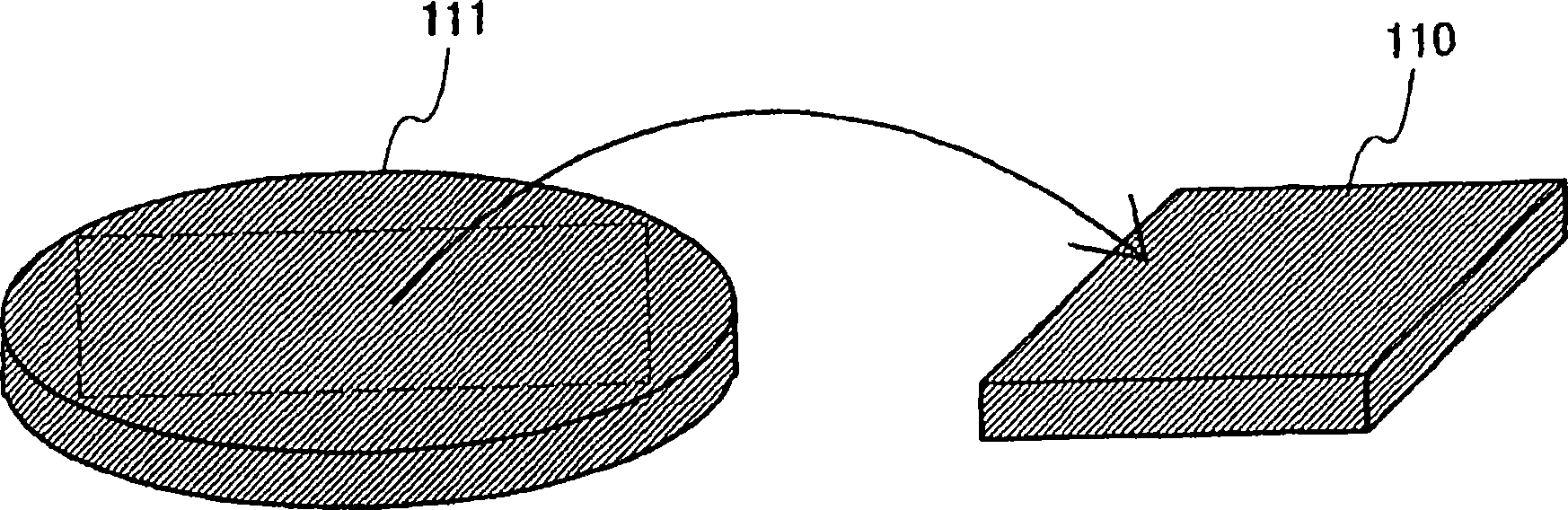

[0244] The single crystal semiconductor substrate 117 from which the single crystal semiconductor layer 115 has been separated can be regenerated and utilized as the single crystal semiconductor substrate 110 . In this embodiment, a regeneration treatment method will be described.

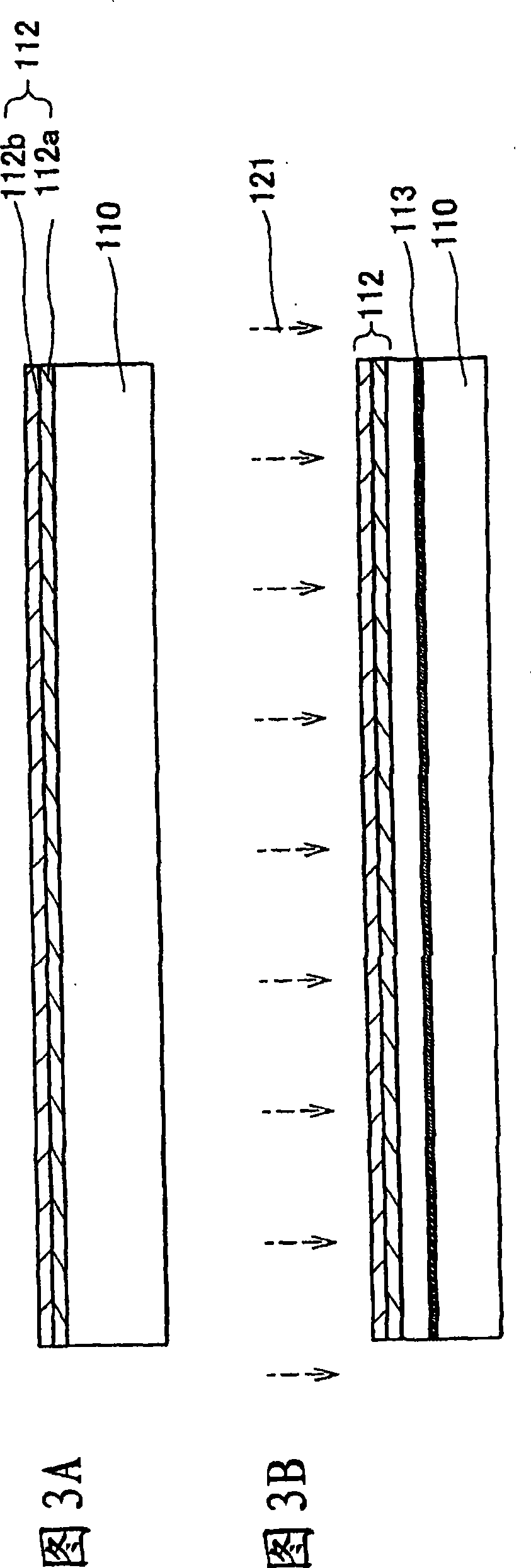

[0245] As shown in FIG. 4A , a portion not bonded to the supporting substrate 100 is left around the single crystal semiconductor substrate 117 . The insulating film 112b, the insulating film 112a, and the bonding layer 114 not attached to the support substrate 100 are left in this portion.

[0246] First, an etching process for removing the insulating film 112b, the insulating film 112a, and the bonding layer 114 is performed. For example, when these films are formed of silicon oxide, silicon oxynitride, or silicon oxynitride, the insulating film 112b, the insulating film 112a, and the bonding layer 114 can be removed by wet etching using a hydrofluoric acid aqueous solution.

[0247] Next, etch...

Embodiment approach 3

[0252] In this embodiment, refer to Figure 16A to Figure 18 , a method of manufacturing a transistor will be described as an example of a method of manufacturing a semiconductor device using the semiconductor substrate 10 . Various semiconductor devices are formed by combining a plurality of transistors. Below, refer to Figure 16A to Figure 18 A cross-sectional view illustrating how the transistor is fabricated. Note that, in this embodiment mode, a method of simultaneously manufacturing an n-channel type transistor and a p-channel type transistor will be described.

[0253] As shown in FIG. 16(A), the semiconductor film 603 and the semiconductor film 604 are formed by processing (patterning) the single crystal semiconductor layer on the supporting substrate 100 into a desired shape by etching. A p-type transistor is formed using the semiconductor film 603 , and an n-type transistor is formed using the semiconductor film 604 .

[0254] In order to control the threshold v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More