Silicon slice mark capturing system and method

A technology for marking, silicon wafers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

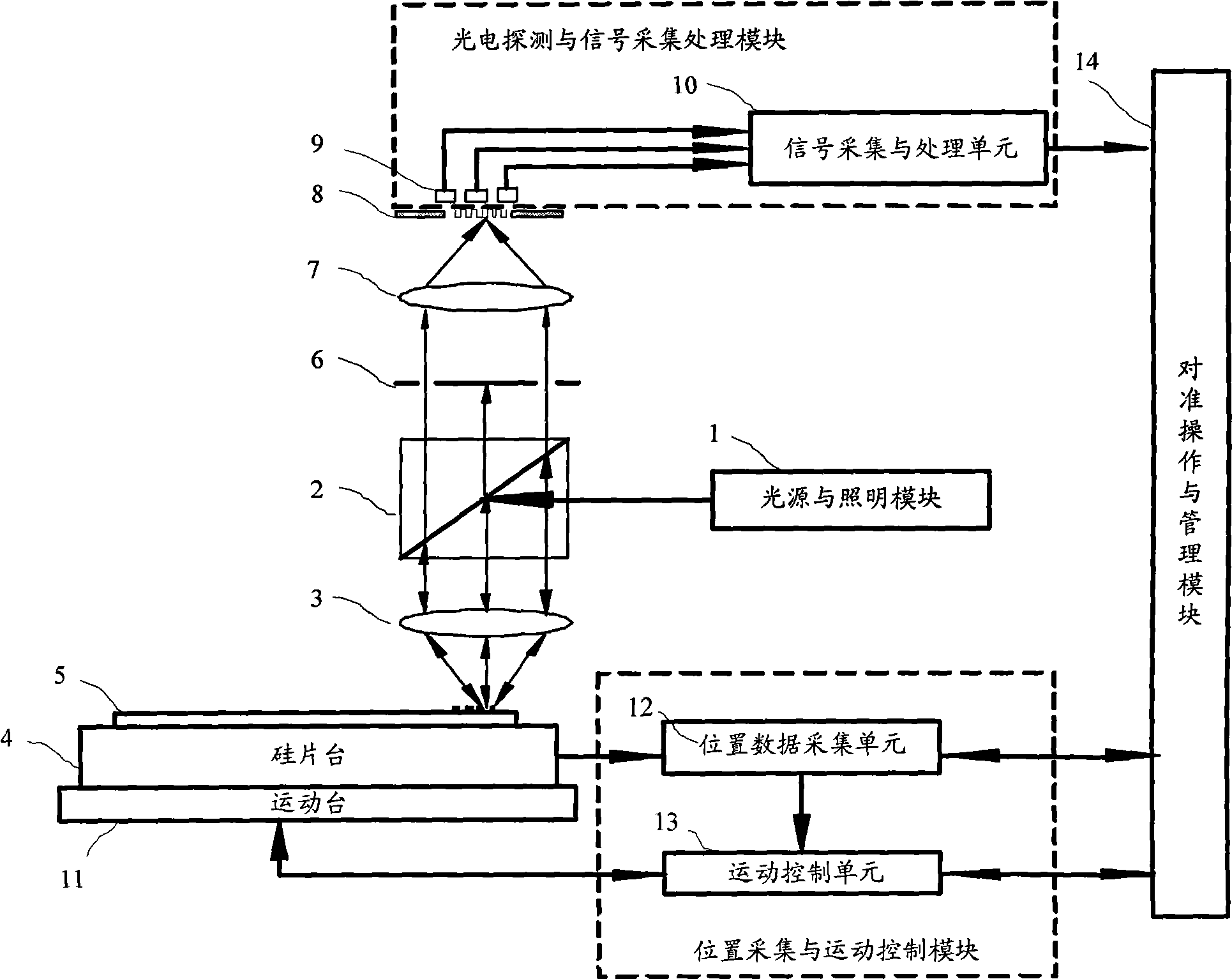

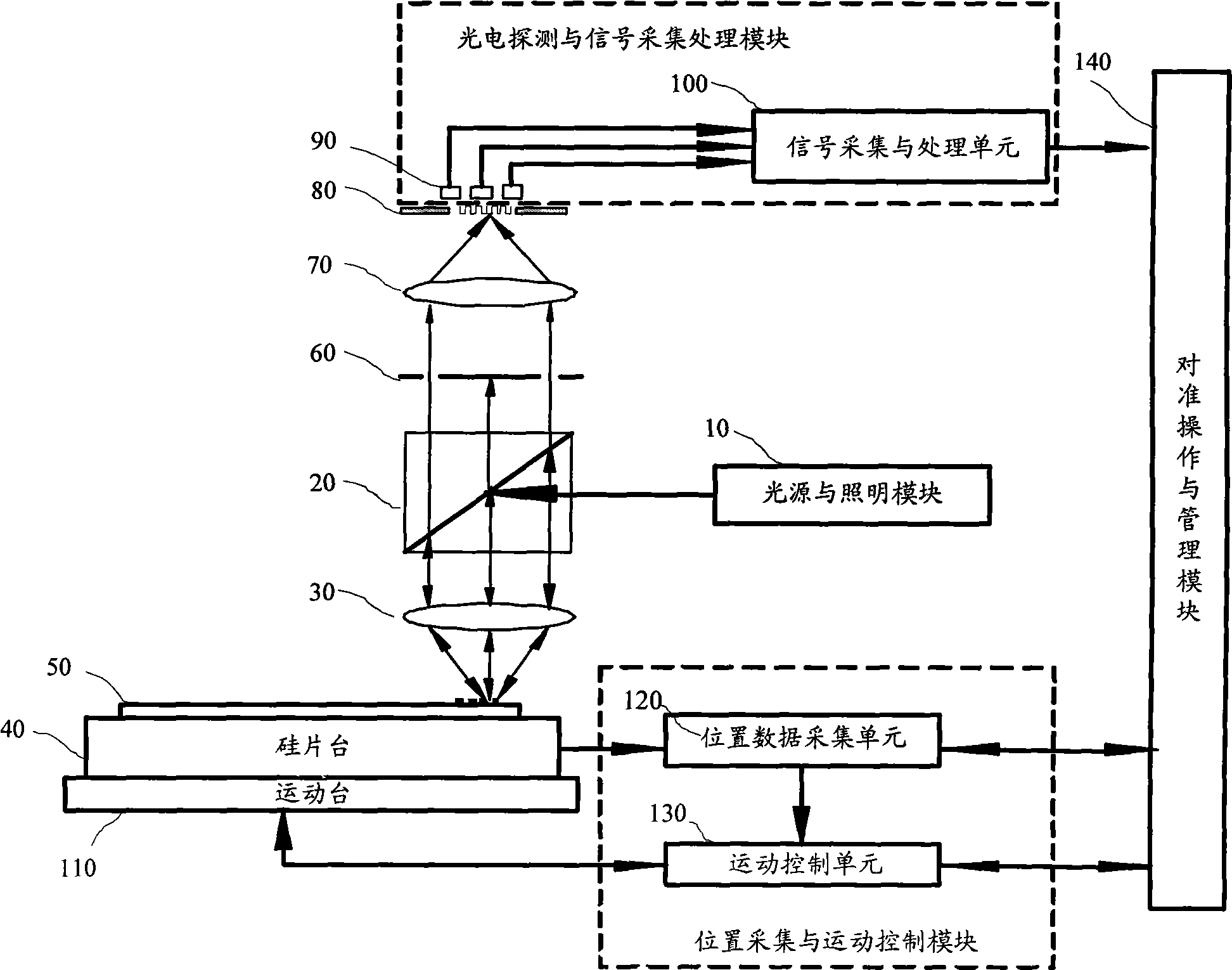

[0046] The system and method for capturing silicon wafer markers proposed by the present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

[0047] An embodiment of the present invention provides a silicon wafer mark capture system and method, which can ensure that the correct silicon wafer mark alignment position can be obtained even when the wafer on-chip repeat error exceeds the capture range of the silicon wafer alignment system , Thereby improving production efficiency.

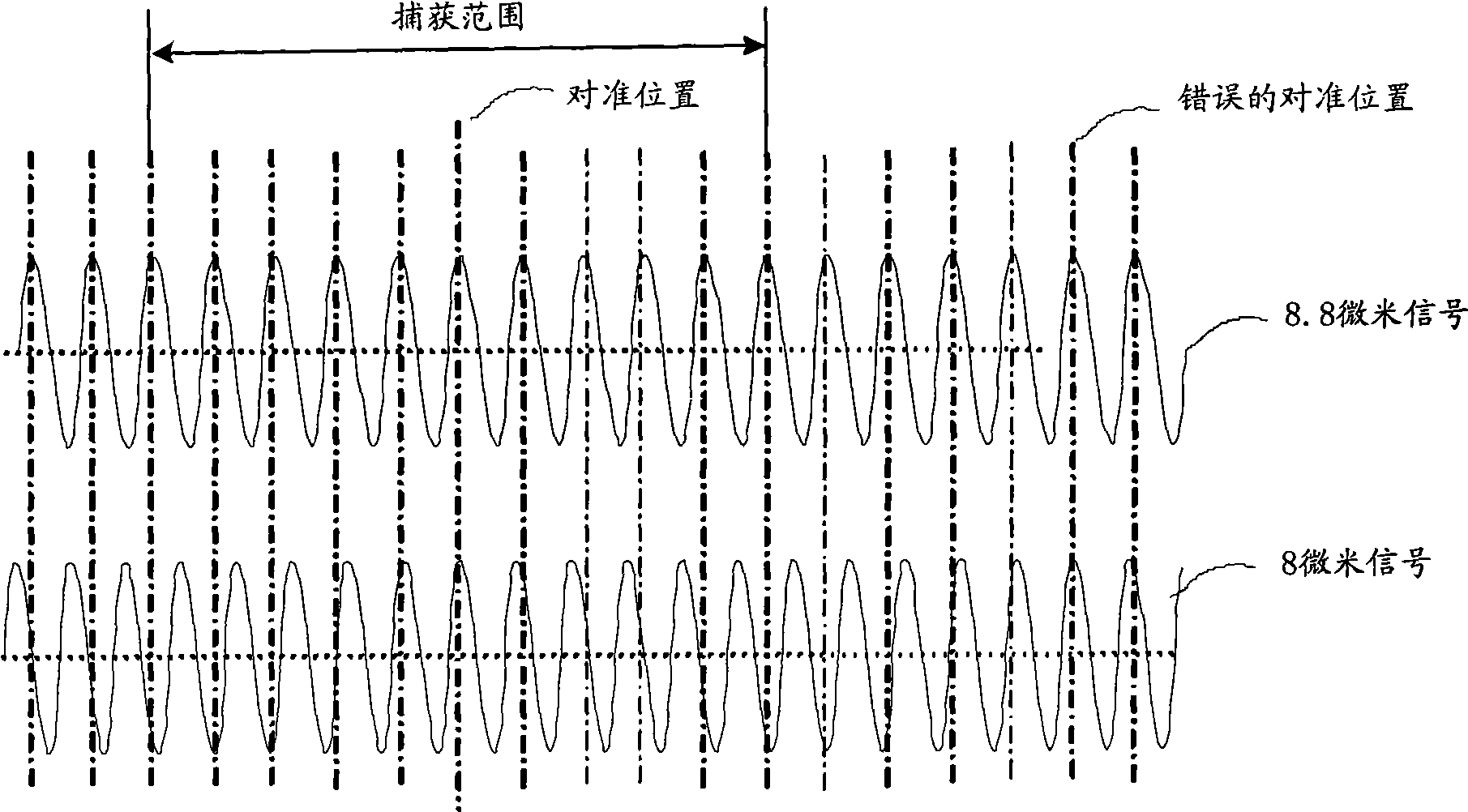

[0048] In the process of engraving the silicon wafer, the lithography equipment first performs mechanical pre-alignment. If the on-chip repetition error of the silicon wafer exceeds the capture range of the silicon wafer alignment system of the lithography equipment, the mark pair cannot be accurately captured. Therefore, the silicon wafer mark capture system for lithography equipment is used to scan to obtain the position of the captu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More