Test graph builder of integrated circuit

A test pattern and generator technology, applied in the direction of instruments, measuring electricity, measuring devices, etc., can solve the problems of the performance degradation of the circuit under test, reduce the test efficiency, prolong the test cycle, etc., to reduce the test power consumption, low cost, reduce jump effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

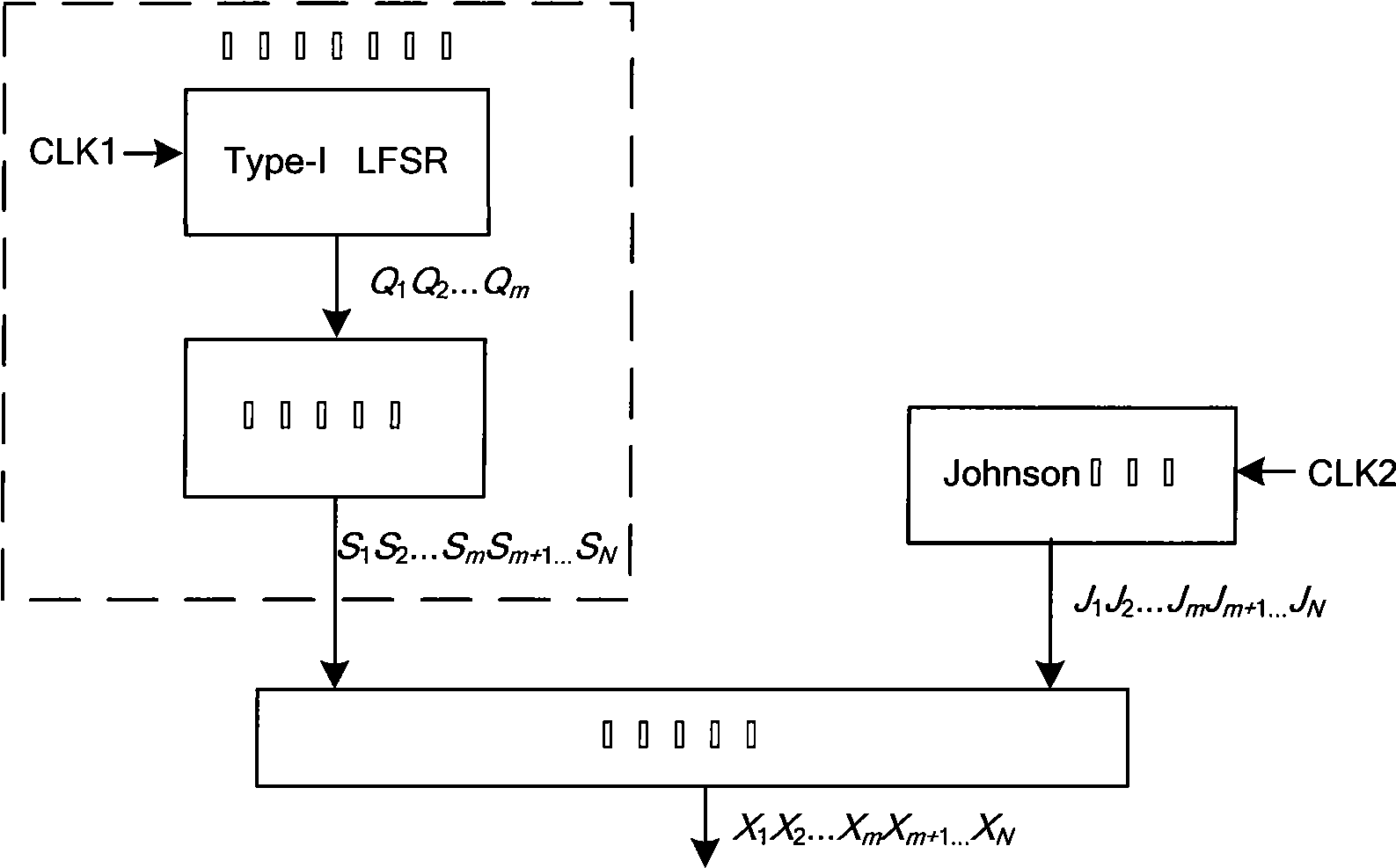

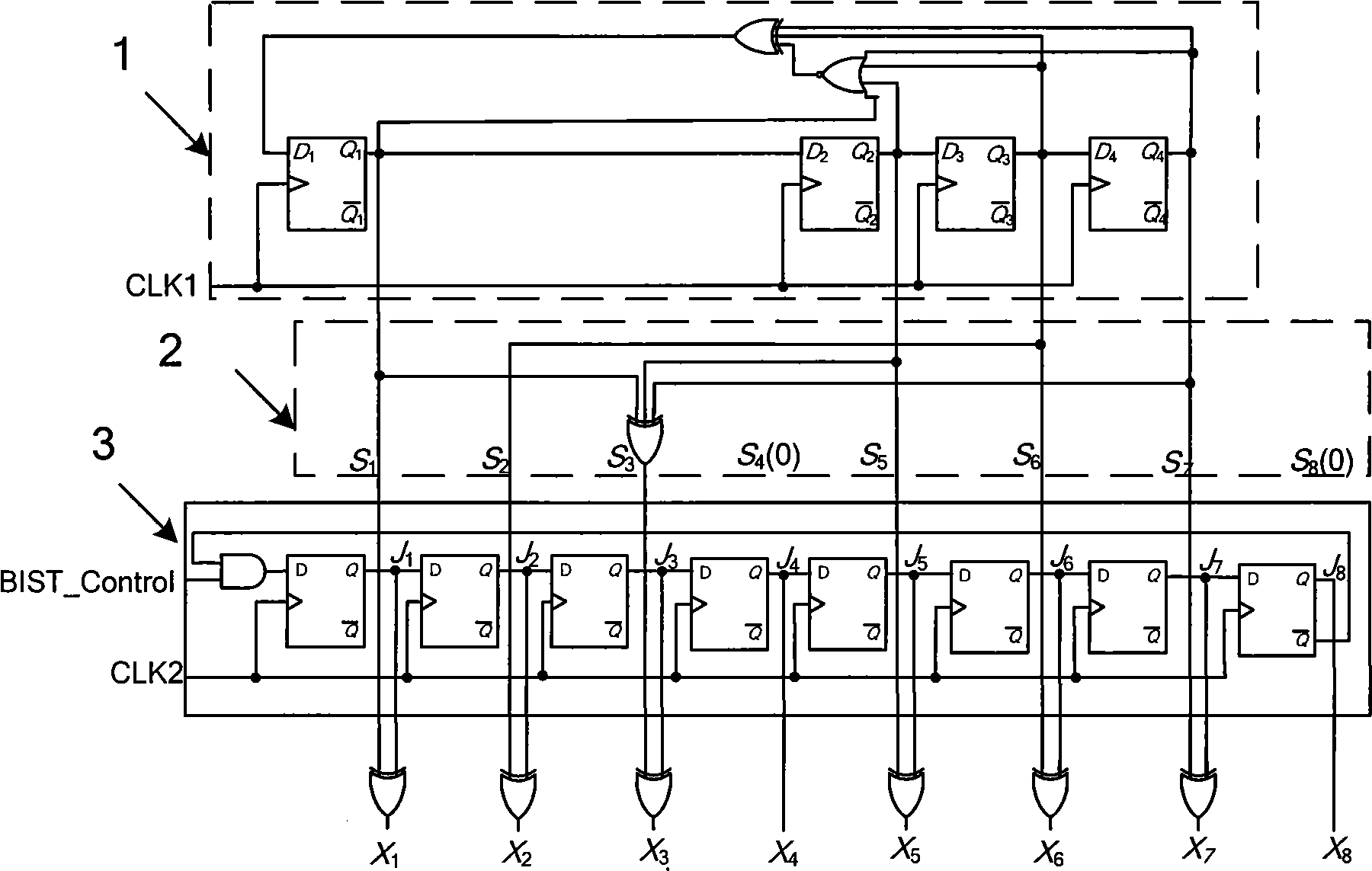

[0025] refer to figure 1 , a test pattern generator for integrated circuits, mainly including: Type I-linear feedback shift register (Type-I LFSR), decompression circuit (Decompressor), Johnson counter (JohnsonCounter) and exclusive OR gate network (XOR-Network).

[0026] Type I-linear feedback shift register (Type-I LFSR) and decompression circuit (Decompressor) together form a seed sequence generator (Seed Generator), which is used to generate a seed vector. Among them, the clock (CLK1) frequency of type I-linear feedback shift register is f 1 , generating sequence Q=[Q 1 Q 2 ...Q m ], where m is a natural number; the decompression circuit will sequence Q=[Q 1 Q 2 ...Q m ] logically expanded to N-bit output sequence S=[S 1 S 2 ... S m S m+1 ... S N ], that is, the seed vector, where the bit width is a natural number N, and N>m. The Type-I-Linear Feedback Shift Register (Type-I LFSR) in the present invention refers to a Linear Feedback Shift Register (LFSR) that a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More