High-side NLDMOS structure

A high-side, N-type technology, applied in the field of high-side NLDMOS structure, can solve the problem of low drain-source breakdown voltage and achieve the effect of improving off-state breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

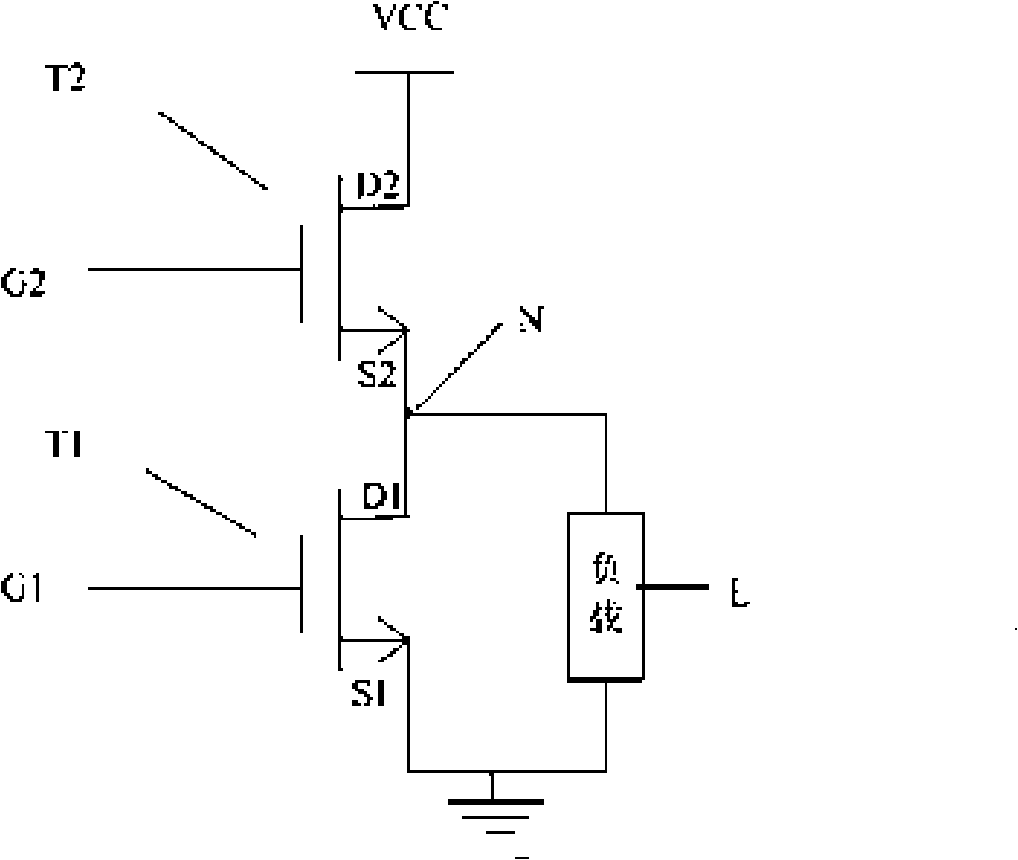

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

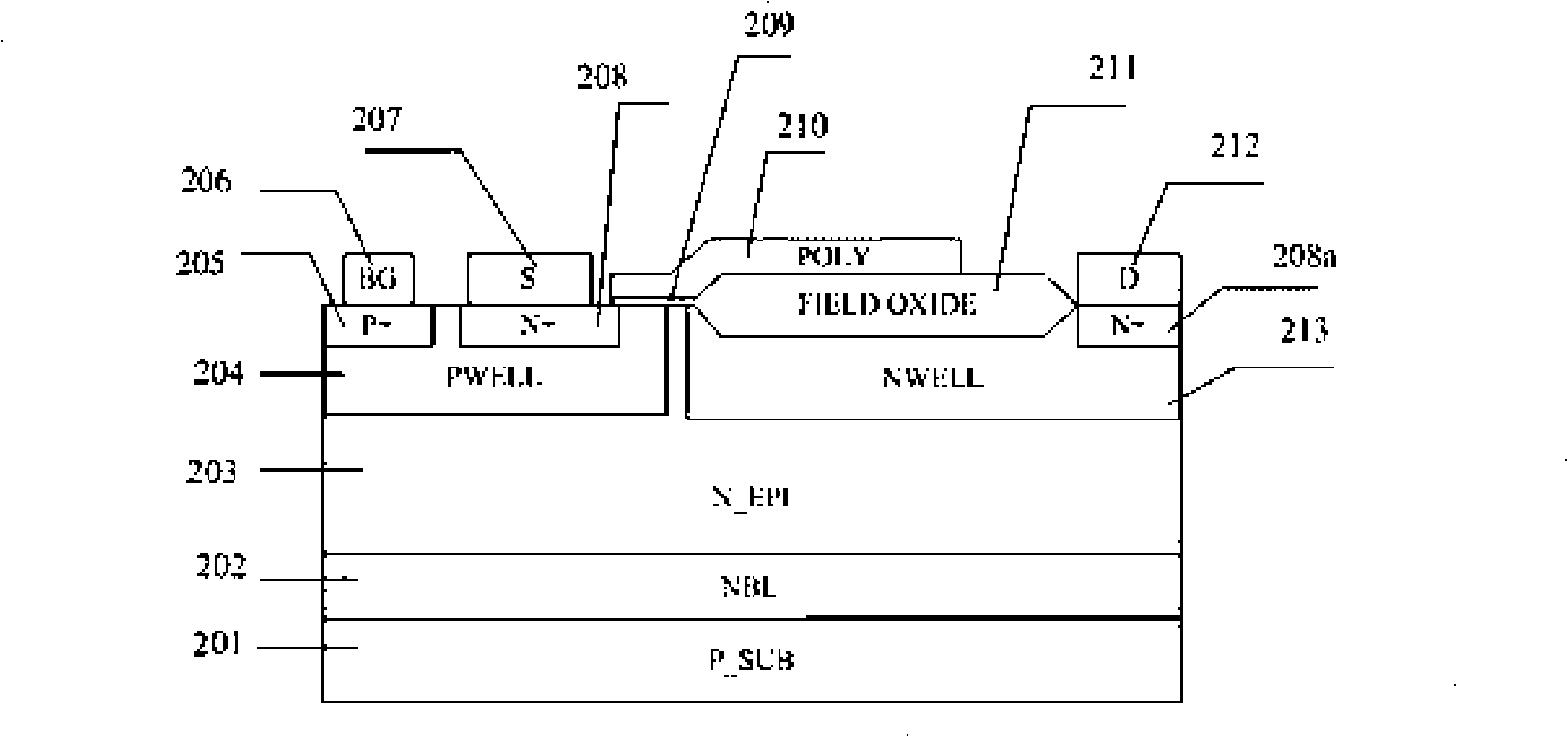

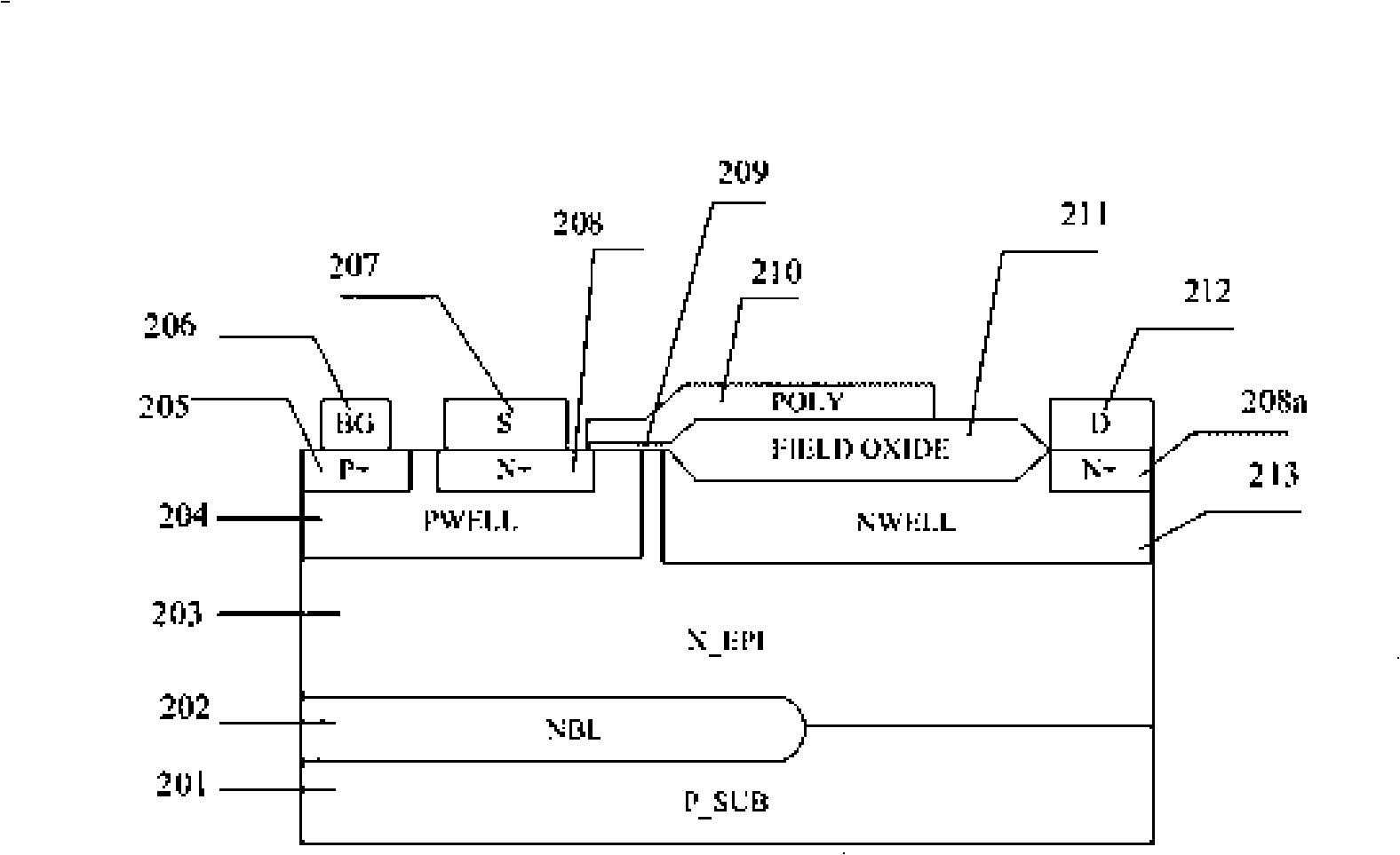

[0017] Embodiments of the present invention: the present invention will be further described in conjunction with the drawings and embodiments of the description. image 3 is a schematic structural diagram of the high-side NLDMOS of the present invention. A portion of the N-type buried layer 202 is located above the P substrate 201 . An N-type epitaxy 203 is above part of the N-type buried layer 202 and part of the P-substrate 201 . The top of the N-type epitaxy 203 is a well region. The P well 204 forms the channel of the LDMOS, and the N well 213 forms the drain drift region of the device. The P+ injection region 205 in the P well 204 is connected to the back gate electrode 206 of the device, the N+ injection region 208 is connected to the source electrode 207 ; the N+ injection region 208a in the N well 213 is connected to the drain electrode 212 . The gate electrode 210 is made of polysilicon, covers the gate oxide 209 , and partly extends to the field oxide 211 to funct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com