ldmos device and its manufacturing method

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., capable of solving problems such as Rsp increase

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

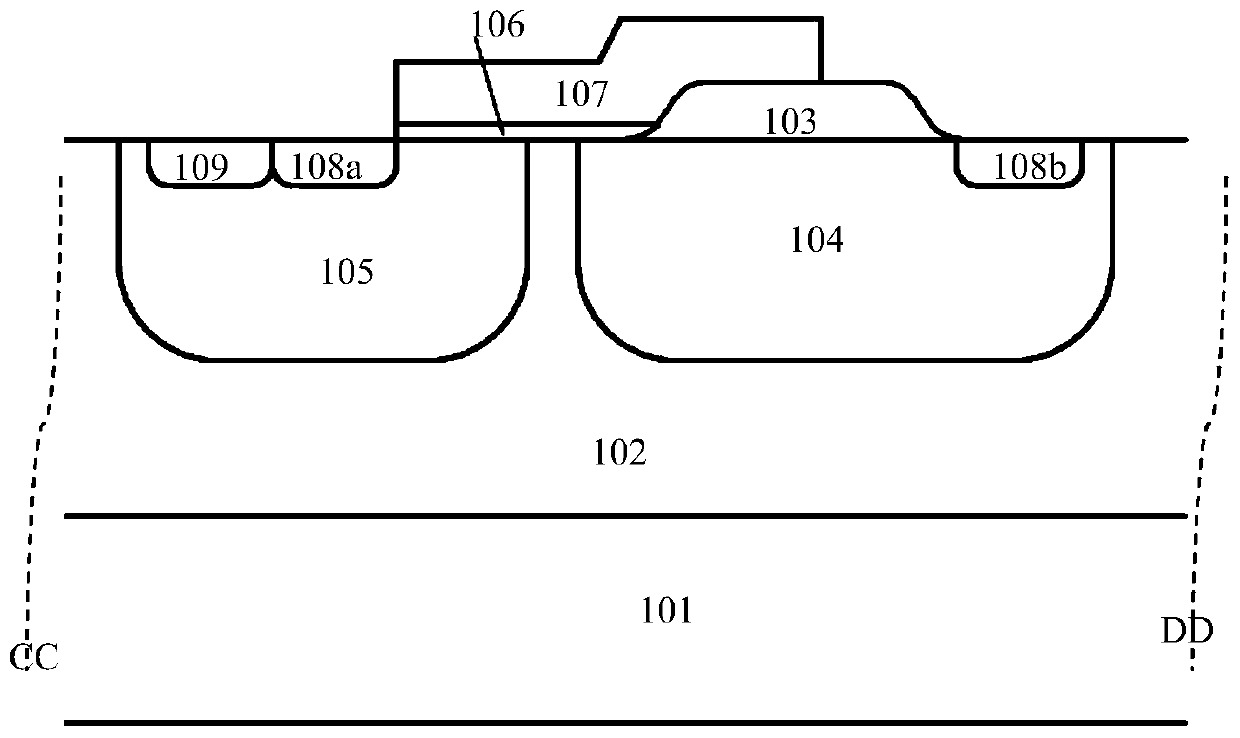

[0054] Such as figure 2 What is shown is a schematic structural diagram of an LDMOS device in an embodiment of the present invention; the LDMOS device in an embodiment of the present invention includes:

[0055] The first epitaxial layer 102 of the second conductivity type has a drift region 104 of the first conductivity type and a body region 105 of the second conductivity type formed in a selected area of the first epitaxial layer 102; the drift regions 104 and The body region 105 is laterally contacted or separated by a distance. Usually multiple LDMOS devices are integrated on the same first epitaxial layer 102, figure 2 Only one LDMOS device located between the dashed line CC and the dashed line DD is shown in the figure. LDMOS devices with the same structure are also formed in other areas outside the dashed line CC and the dashed line DD, and LDMOS devices in other areas outside the dashed line CC and DD Device figure 2 No longer shown in.

[0056] A first buried layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More