Novel methodology to realize automatic virtual metrology

An automated, measurement technology for electrical components, comprehensive factory control, semiconductor/solid-state device manufacturing, etc., that solves problems such as missing parameters or steps, inaccuracies, mispredictions, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] It is to be understood that the present invention provides many different embodiments or examples for implementing the various features of the present invention. Specific equipment and configurations are described below to simplify the present invention. These are of course examples only and not intended to be limiting. Furthermore, the present disclosure may repeat reference numerals and / or text in different instances. The repetition is for the purpose of simplicity and clarity and does not represent a relationship between the different embodiments or configurations discussed. The present invention provides an innovative approach to enable wafer outcome prediction across batch fabrication tools. Various examples, embodiments, variations, and varieties of the invention are described below.

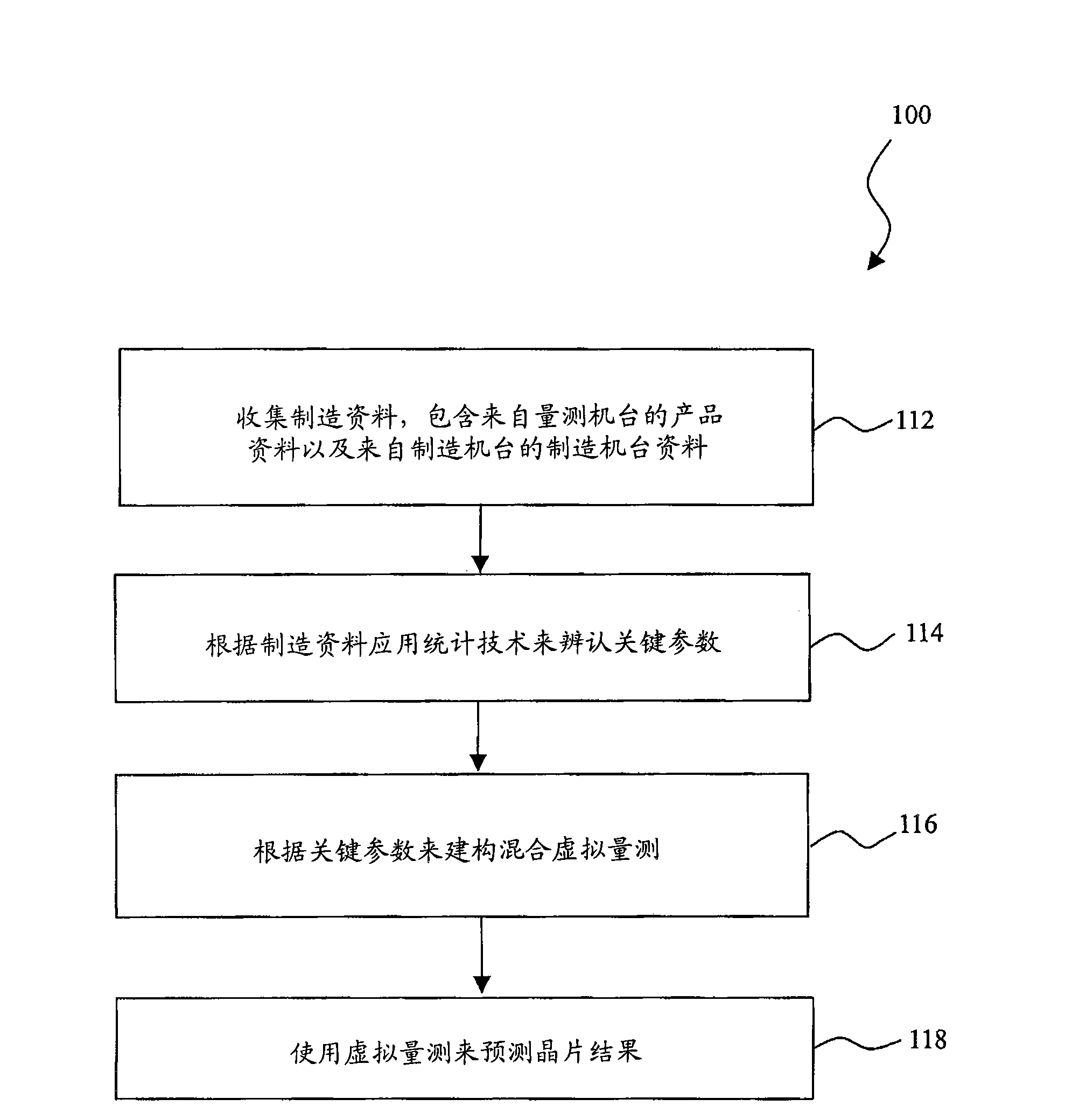

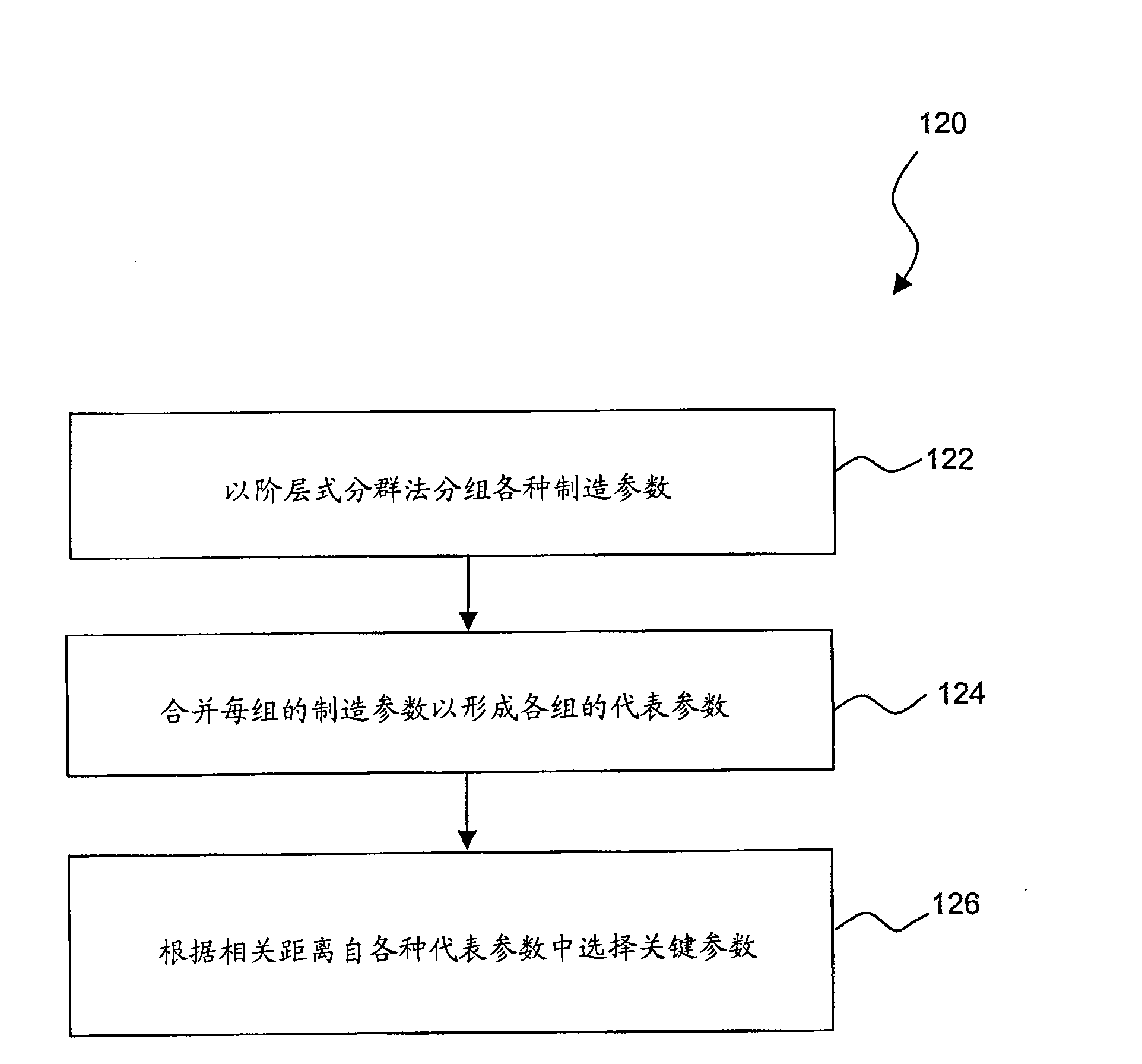

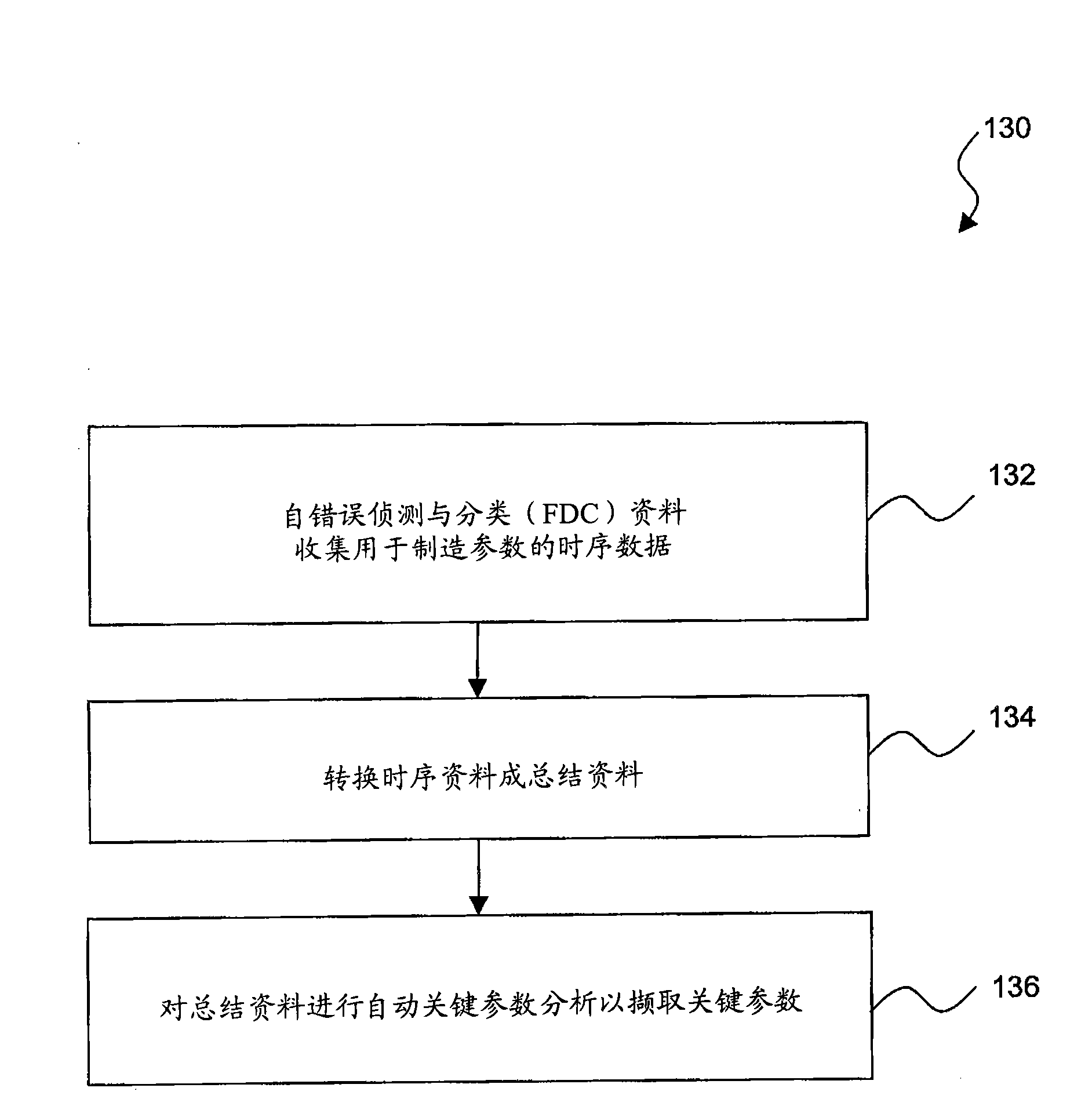

[0042] figure 1 A simplified flow diagram of a method 100 for enabling wafer result prediction using hybrid virtual metrology and / or clustering techniques. Image 6 It is a blo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More