Parallel frame synchronous scrambling device and descrambling device thereof

A frame synchronization and frame synchronization signal technology, applied in the direction of synchronization devices, baseband systems, digital transmission systems, etc., can solve problems such as slow computing speed, small universal range, and complex iterations, so as to improve work efficiency and processing frequency, reduce Computational complexity, the effect of less combinatorial logic

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

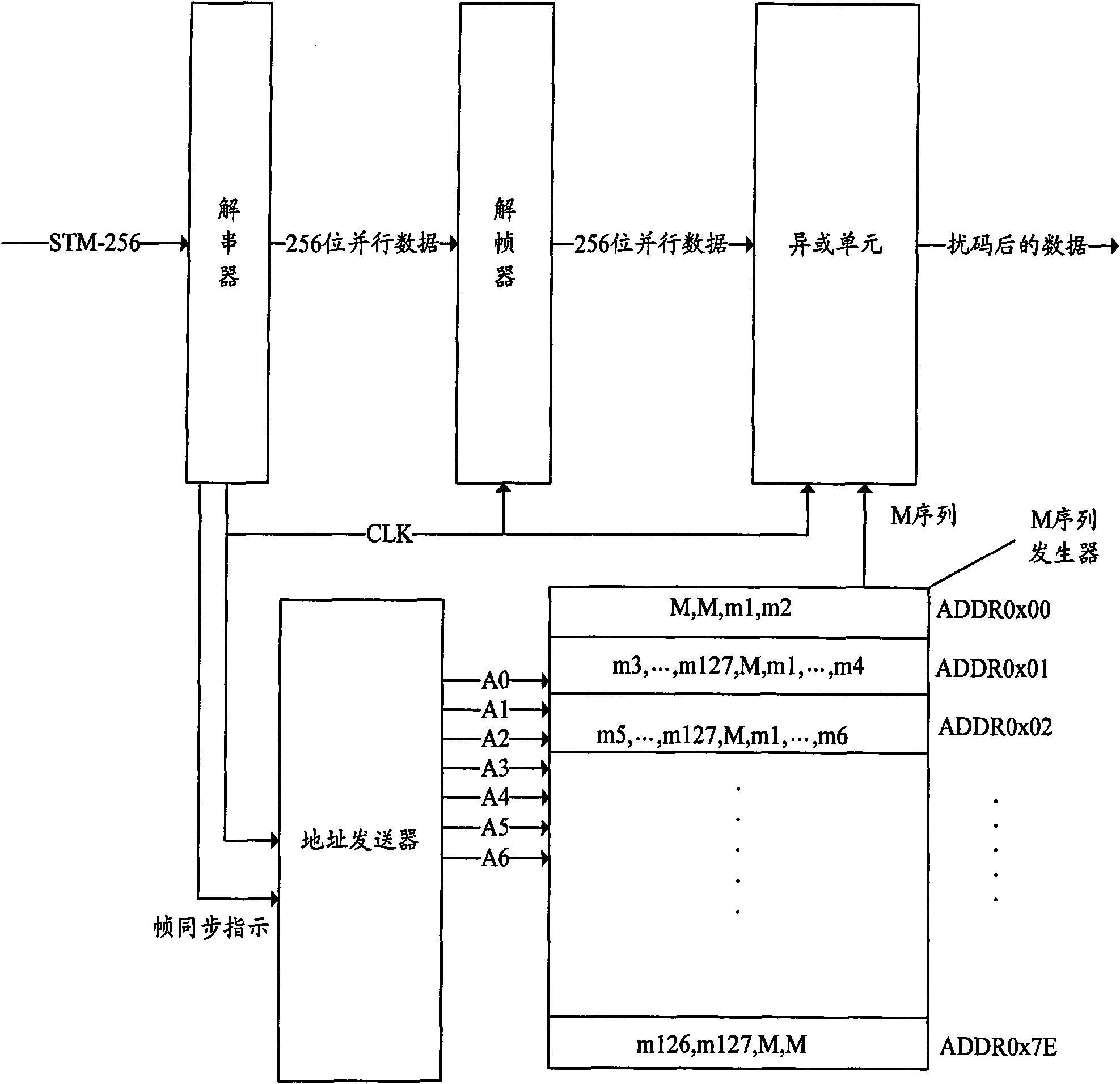

[0059] Combine below image 3 , only a 256-bit width SDH STM-256 signal parallel frame synchronization scrambler is described as a design example, but all solutions are applicable to parallel frame synchronization scramblers with other bit widths.

[0060] The system works at a clock frequency of 155.52MHz, and realizes the scrambling function with a parallel width of 256 bits. The M-sequence generator is composed of ROM, since the characteristic polynomial of SDH scrambling code is x 7 +x 6 +1 for using 2 7 -1 is a pseudo-random sequence with a 127-bit period, so its capacity is: (2 7 -1×256) bits, 2 7 -1 is the depth of the storage space; 256 is the width of the storage space, which contains 256 127-bit pseudo-random sequences. It should be pointed out that: image 3 Among them, M represents the entire 127-bit pseudo-random sequence, and m1, m2... represent the contents of the corresponding bit positions of the pseudo-random sequence.

[0061] image 3 Among them, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More