Protection sealing ring used for preventing stress caused by cutting die

A sealing ring and chip technology, used in electrical components, electrical solid devices, circuits, etc., can solve the problem of crack propagation without sufficient strength, and achieve the effect of reducing crack propagation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The making and using of the embodiments are discussed in detail below. It should be appreciated, however, that the embodiments present many applicable inventive concepts that can be implemented in a wide variety of specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use the invention, and do not limit the scope of the invention.

[0017] A seal ring structure with improved crack resistance and a method of forming the same are provided. Variations of this embodiment are also discussed. The same reference numerals are used to refer to the same elements throughout the various views and exemplary embodiments of the invention.

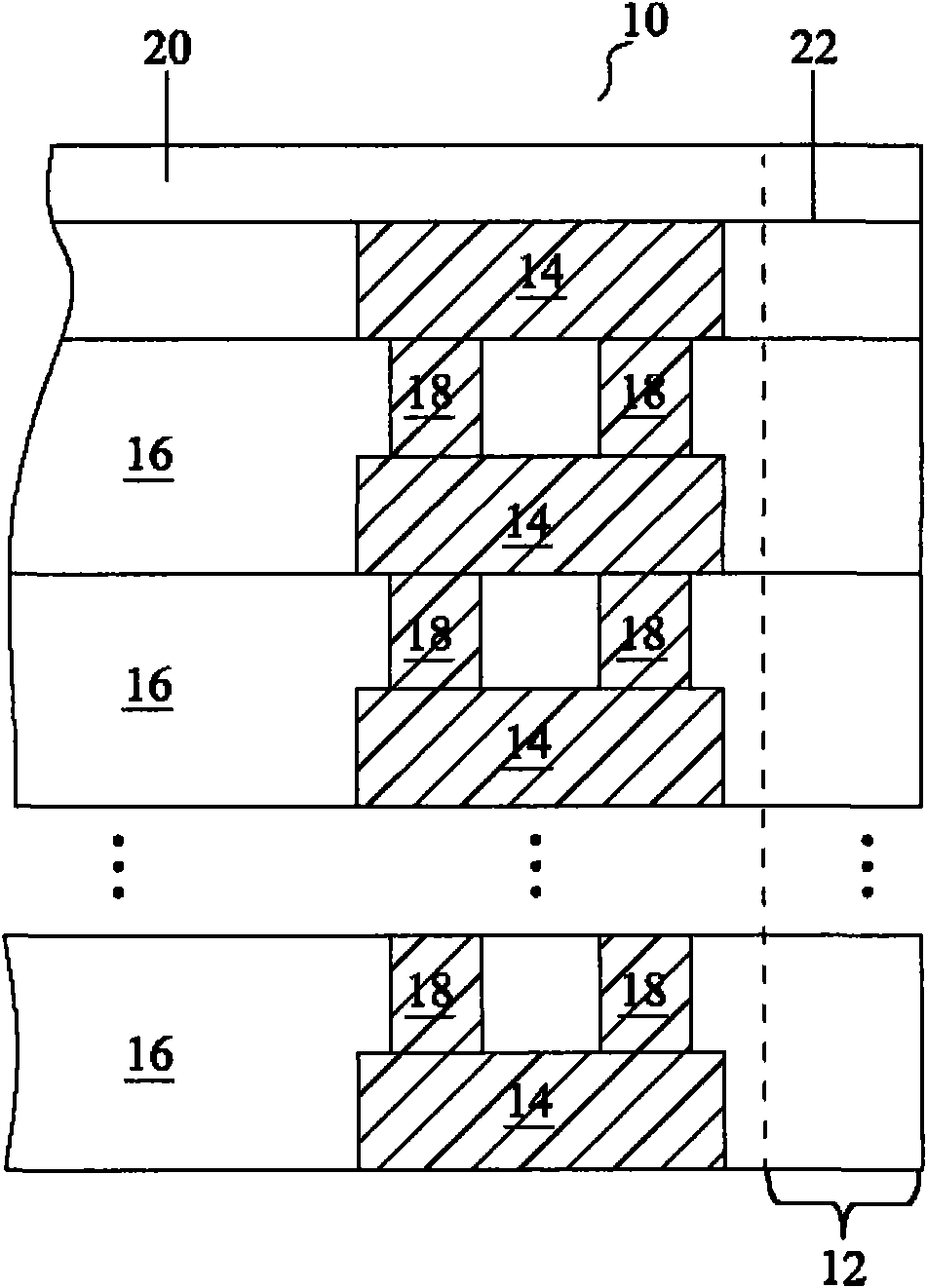

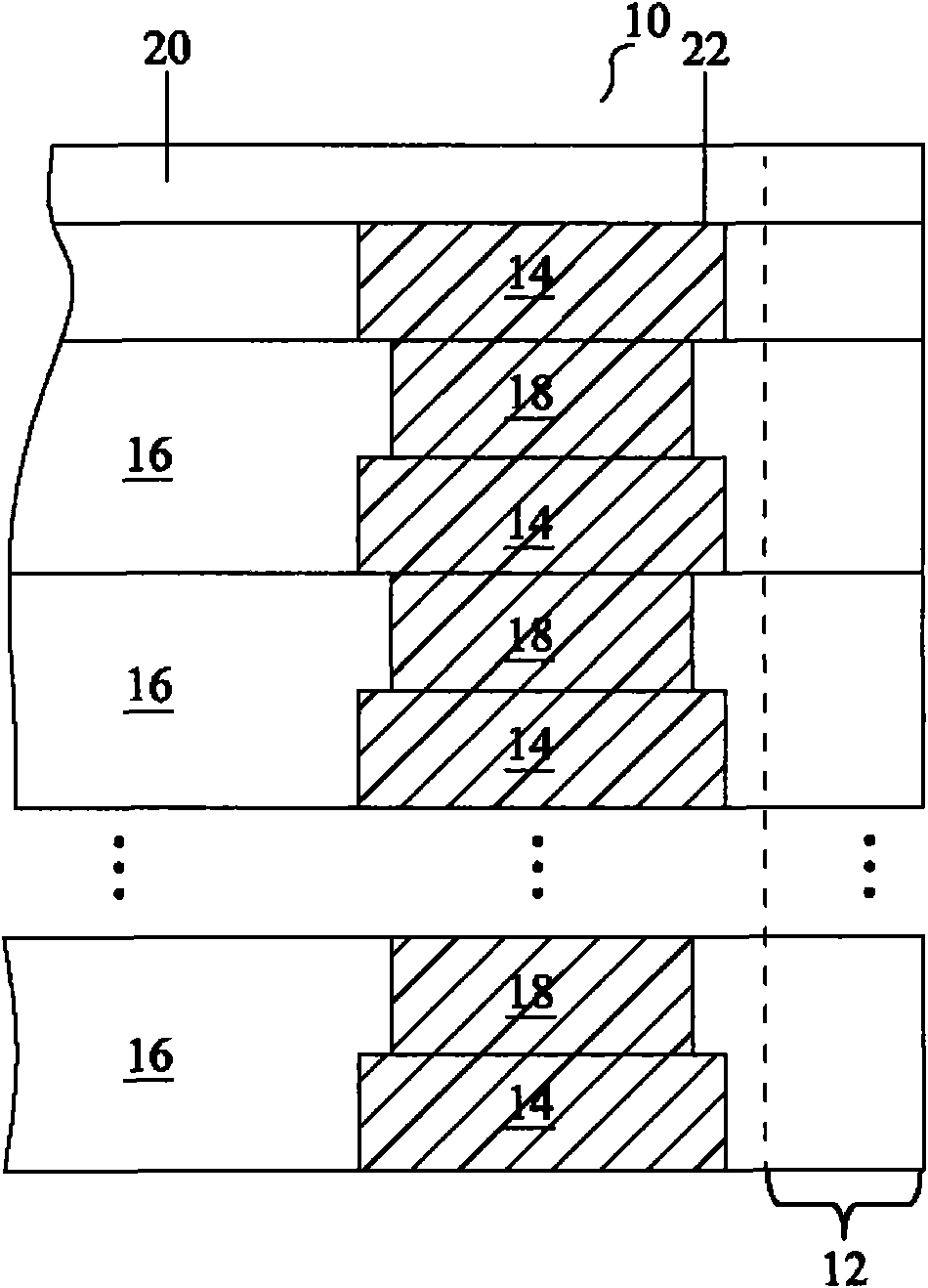

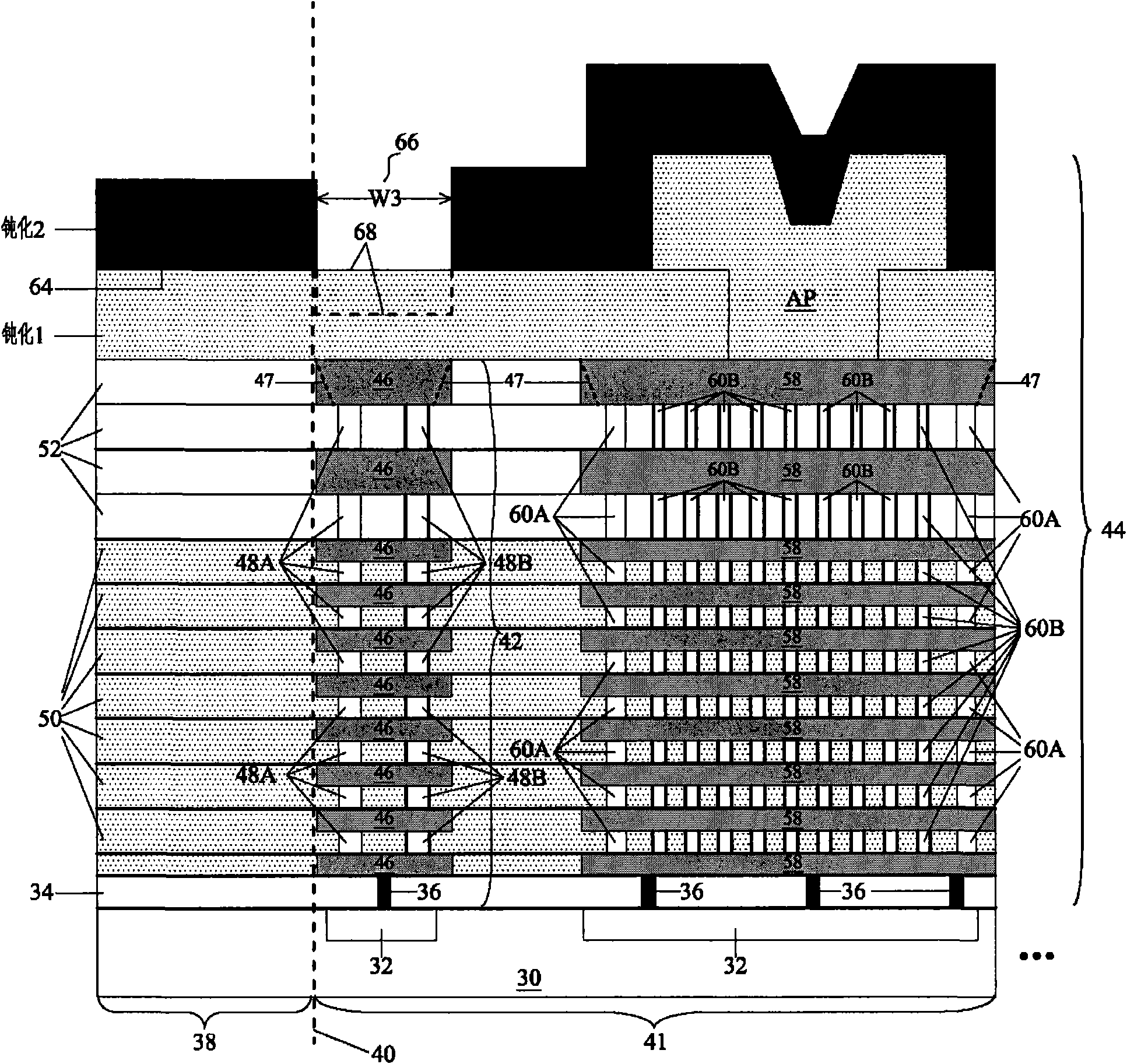

[0018] attached Figure 3A A first embodiment of the invention is shown. A portion of the semiconductor wafer includes a semiconductor substrate 30, which may be formed from silicon or other Group III, IV and / or V elements. The semiconductor substrate 30 may be lightly doped with p-type impu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More