Method for reducing resource consumption of instruction memory on stream processor chip

An instruction memory, stream processor technology, applied in memory systems, concurrent instruction execution, electrical digital data processing, etc., can solve problems such as low program performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

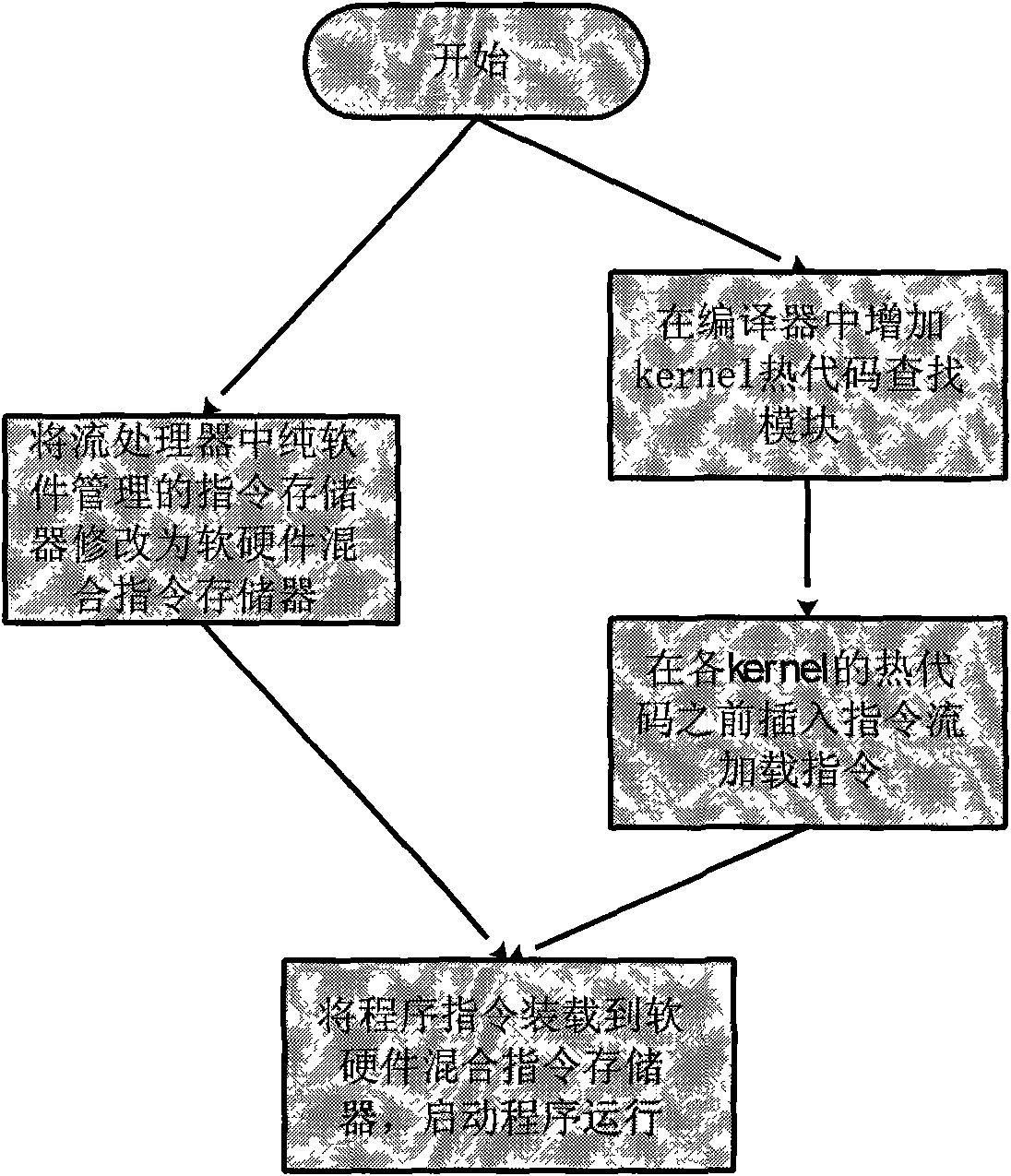

[0087] figure 1 Is the overall flow chart of the present invention.

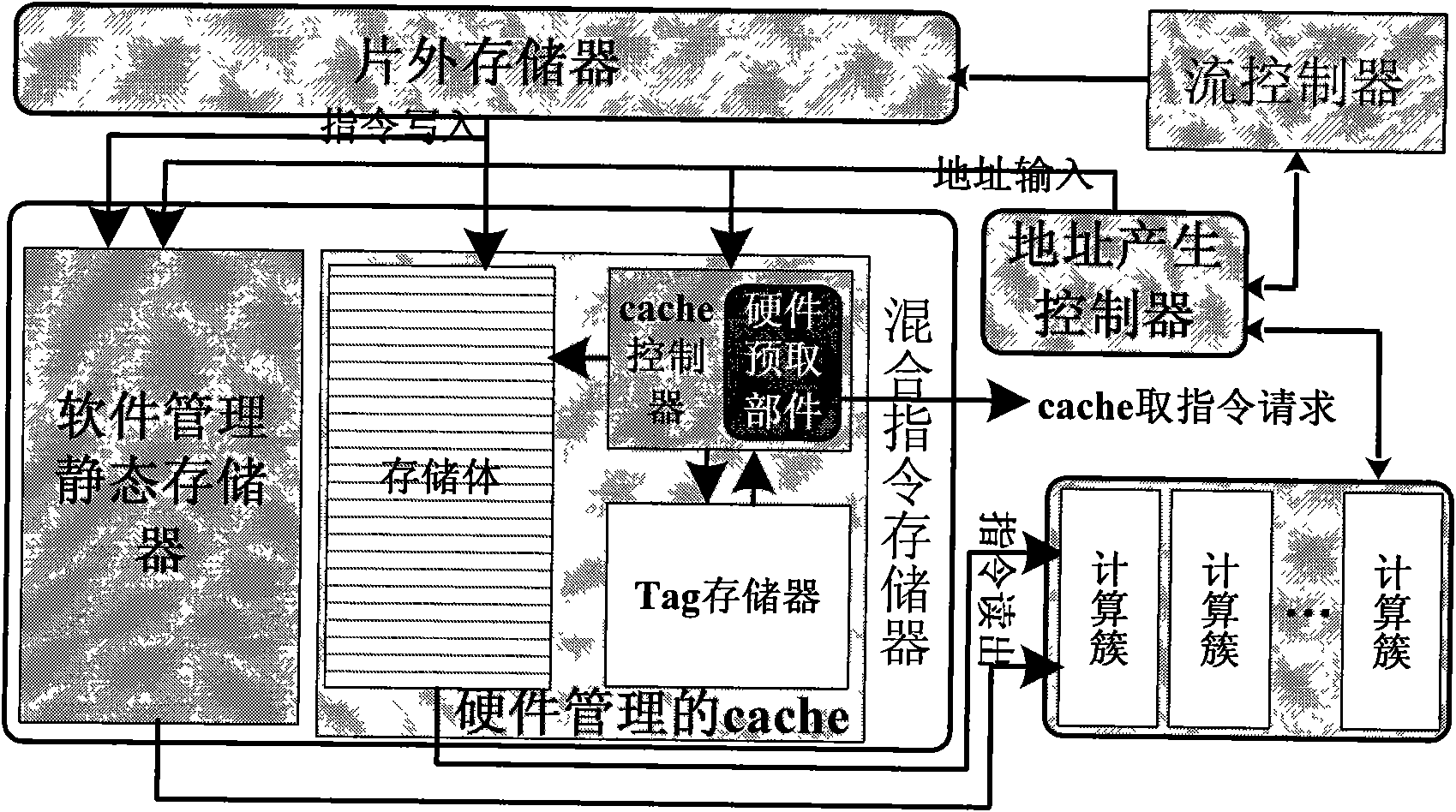

[0088] The first step is to modify the pure software-managed instruction memory in the stream processor to a software-hardware hybrid instruction memory. The software-hardware hybrid instruction memory is composed of software-managed static memory and hardware-managed cache. Such as figure 2 shown.

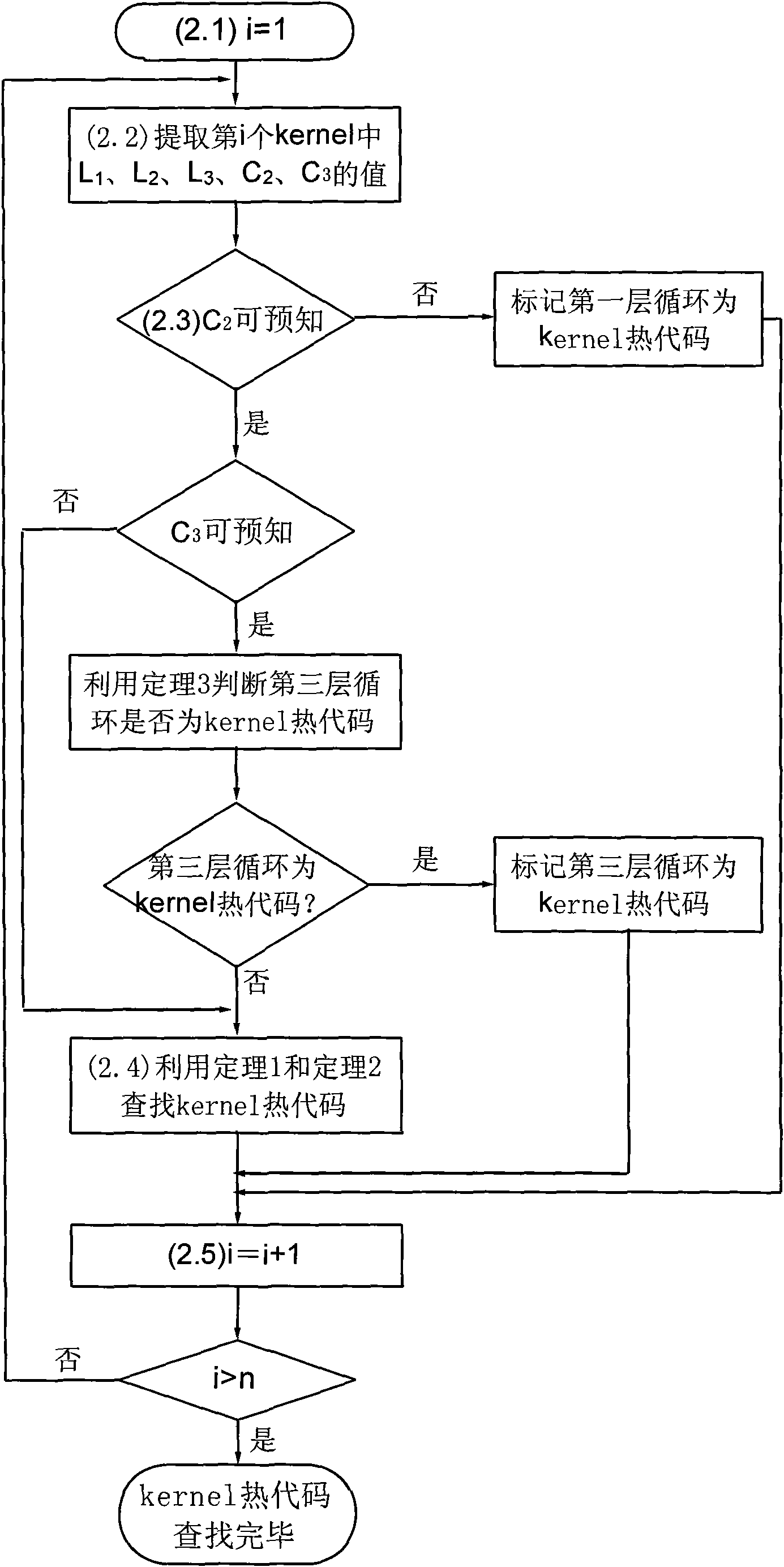

[0089] The second step is to add a kernel hot code search module to the compiler, and use the kernel hot code search module to search for kernel hot code. The search method flow is as follows image 3 shown.

[0090] The third step is to add instruction stream loading instructions before each kernel hot code during stream-level compilation.

[0091] The fourth step is to load the program instructions into the mixed hardware and software instruction memory, and start the program to run. The flow of the program running process and the read / write operation of the mixed hardware and software instruction memor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More