High-speed high-precision flow line structure ADC

A pipeline, high-precision technology, applied in the direction of analog-to-digital converters, etc., can solve the problem of linearity, offset and other parameters affecting the gain of the circuit board, complex reference circuit and bias structure, and high circuit technology requirements.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] Further describe the present invention below in conjunction with accompanying drawing.

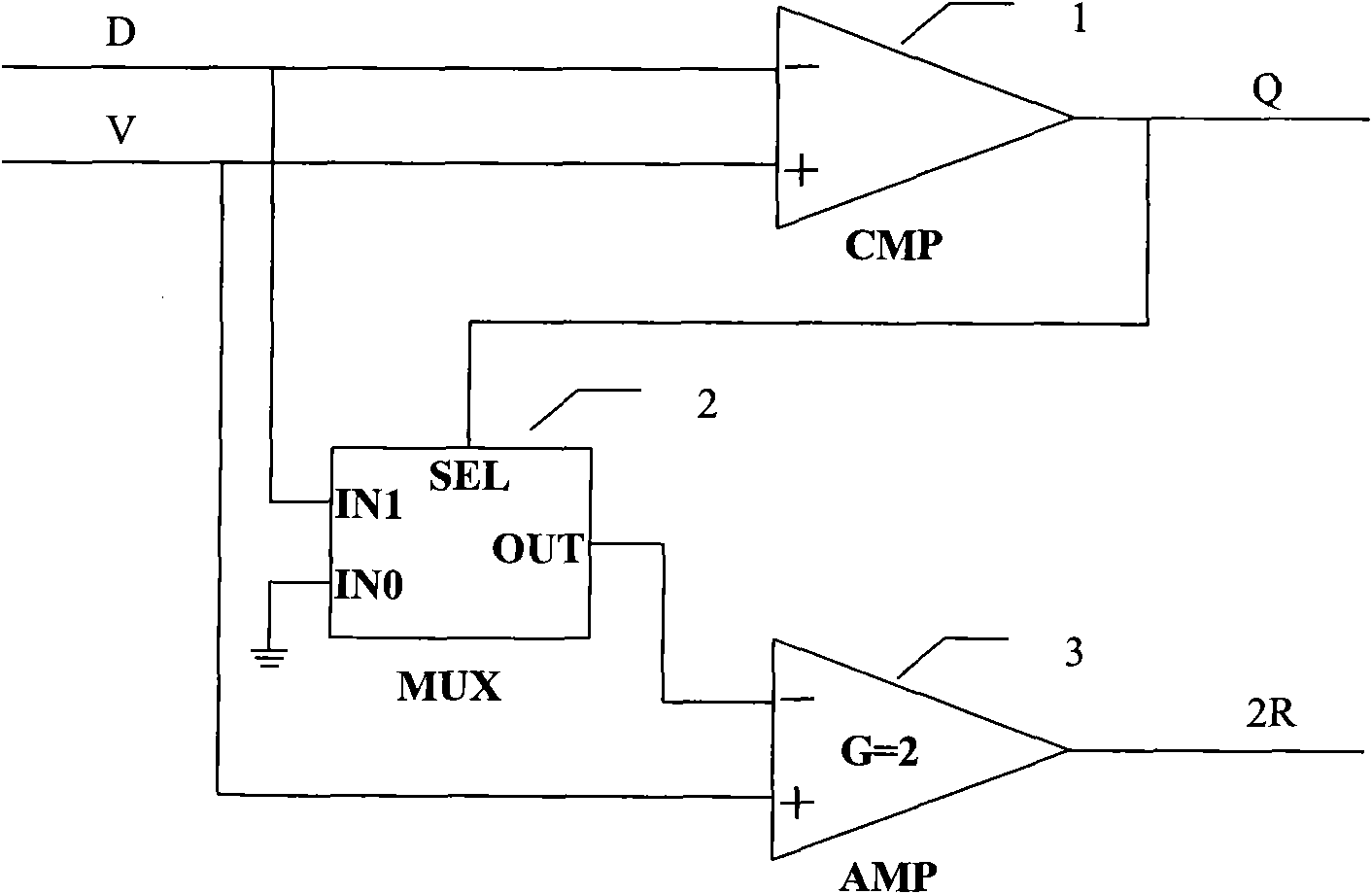

[0020] like figure 1 The one-bit analog-to-digital conversion sub-module is composed of a comparator 1, an analog data selector 2, and a subtractor 3 with a fixed gain of 2. The positive and negative inputs of the comparator are respectively connected to the input signal V i (divisor) and reference signal D (divisor), the comparator output Q (quotient) is also used as the control terminal of the analog data selector. The input of the two-to-one analog data selector is the reference signal D and 0 level, if Q is 0, the output is 0, and if Q is 1, the output is D. The positive and negative inputs of the subtractor with a gain of 2 are respectively connected to the input signal V i Choose one of the two to simulate the output of the data selector, so that the output of the subtractor 2R is V i 2 times the remainder of division by (binary division) D.

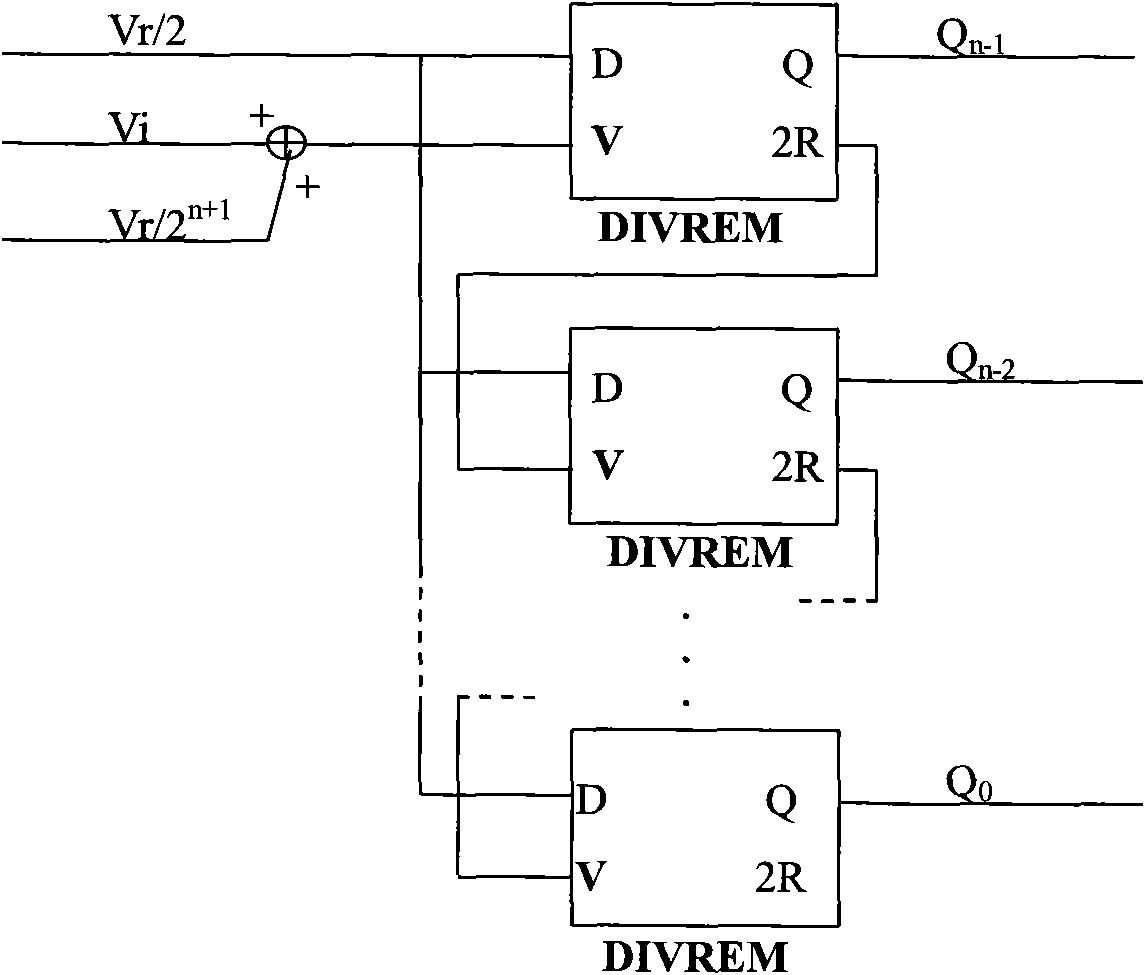

[0021] like figure 2 Will ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More