Solder bump interconnect for improved mechanical and thermo mechanical performance

A technology of bump structure and metal under bump, which is applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., and can solve problems such as overlap

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

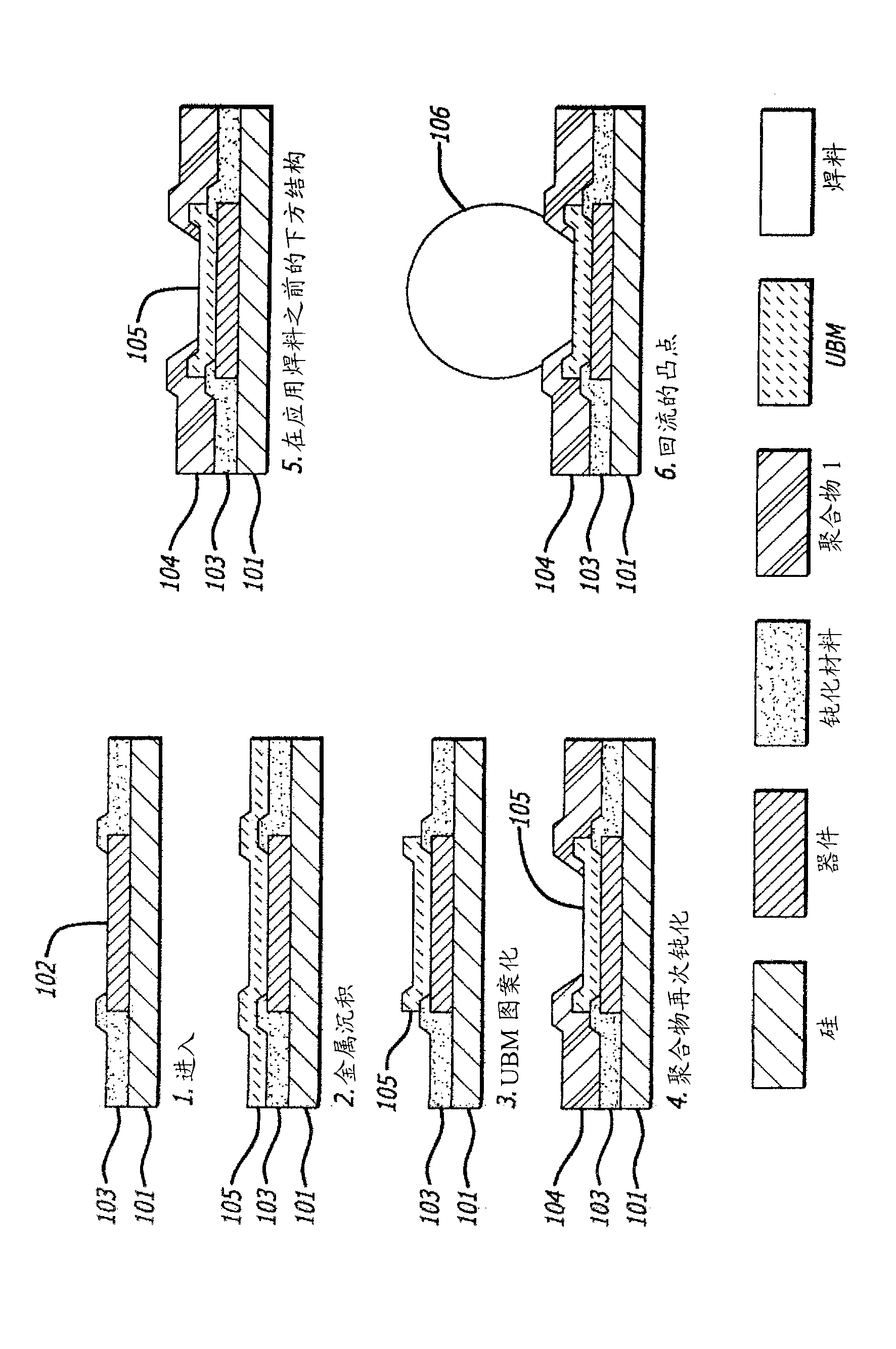

[0041] The following description and drawings illustrate specific embodiments sufficient to enable a person skilled in the art to practice the systems and methods described herein. Other embodiments may incorporate structural, logical processing and other changes and are also intended to fall within the scope of this disclosure. Examples represent possible variations only.

[0042] Elements that implement various embodiments of the present systems and methods are described below. Many elements are configurable using known structures. It should also be understood that the techniques of the present systems and methods can be implemented using a variety of techniques.

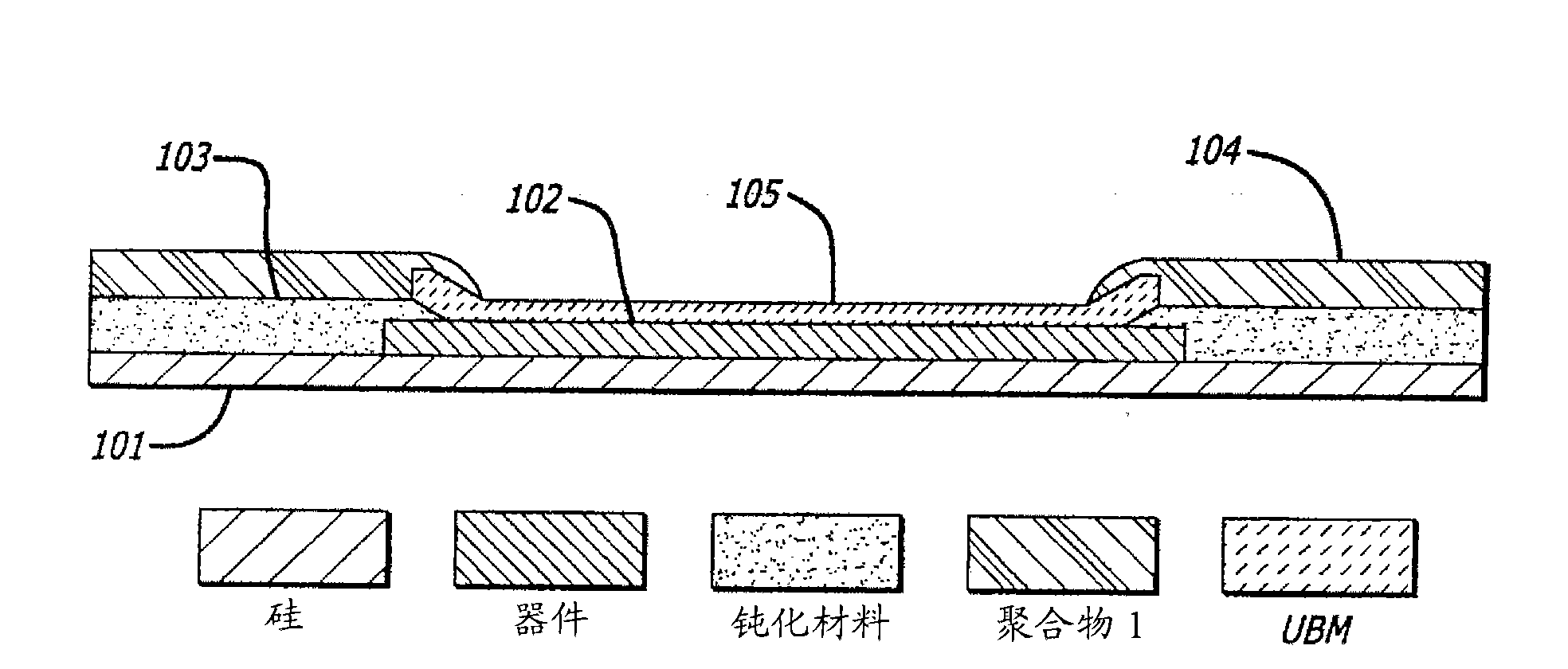

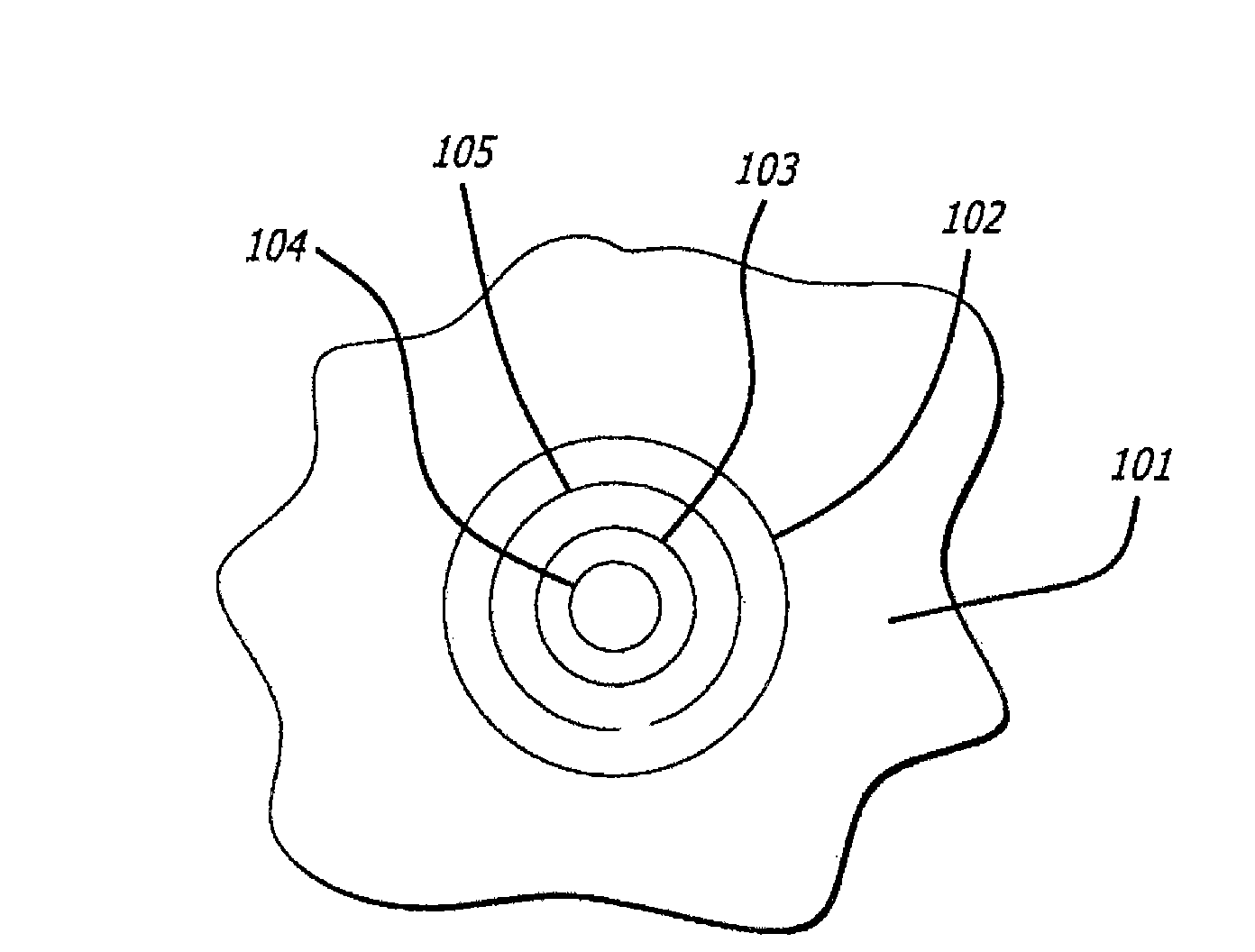

[0043] Disclosures of specific embodiments of solder bump interconnect structures with improved thermomechanical strength and drop test performance are presented below. Semiconductor device packages are typically implemented as chip-scale or wafer-level packages, eg, for chip-on-board assembly applications, or ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More