Systems, methods and software for preloading instructions from variable length instruction sets with appropriate predecoding

A pre-decoding, instruction set technology, applied in concurrent instruction execution, microprogram loading, instrumentation, etc., can solve problems such as adverse effects on processor performance and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

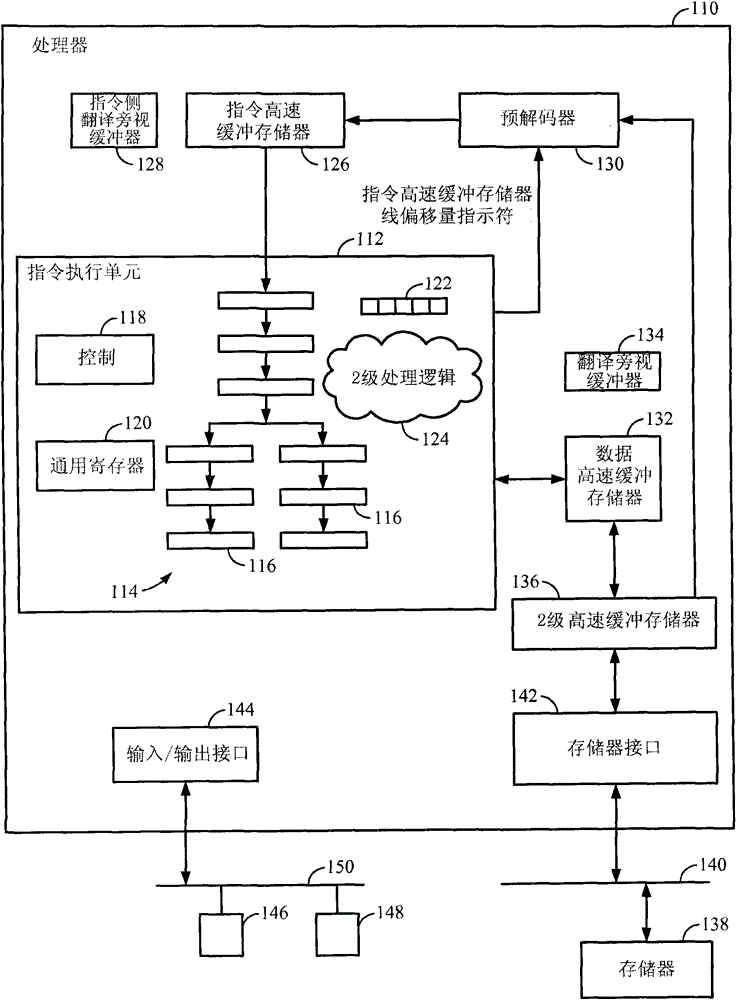

[0016] figure 1 A functional block diagram of processor 110 executing instructions from at least one variable length instruction set is depicted. In particular, processor 110 correctly pre-decodes instructions preloaded from a variable length instruction set. The processor 110 executes instructions in an execution unit 112 comprising a pipeline 114 including a plurality of registers or latches 116 organized in pipe levels and logic and computation circuitry such as an arithmetic logic unit (ALU) (not shown). The pipeline executes instructions according to the control logic 118 . As shown, pipeline 114 may be of a superscalar design.

[0017] A general purpose register (GPR) file 120 provides registers that form the top of the memory hierarchy. In one embodiment, the instruction execution unit also includes a status register 122, which may indicate an offset into the instruction cache line where the first instruction is located, as explained further herein. Instruction exec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More