Refrigeration structure for three-dimensional encapsulation of micro-electronics and preparation method thereof

A three-dimensional packaging and microelectronics technology, applied in the direction of electric solid device, semiconductor/solid state device manufacturing, circuit, etc., can solve the problems of reducing the reliability of chip operation, increasing the volume of integrated devices, increasing refrigerant exposure, etc. Realize, improve heat dissipation efficiency, and the effect of high process integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The embodiments of the present invention are described in detail below. This embodiment is implemented on the premise of the technical solution of the present invention, and detailed implementation methods and specific operating procedures are provided, but the protection scope of the present invention is not limited to the following implementation example.

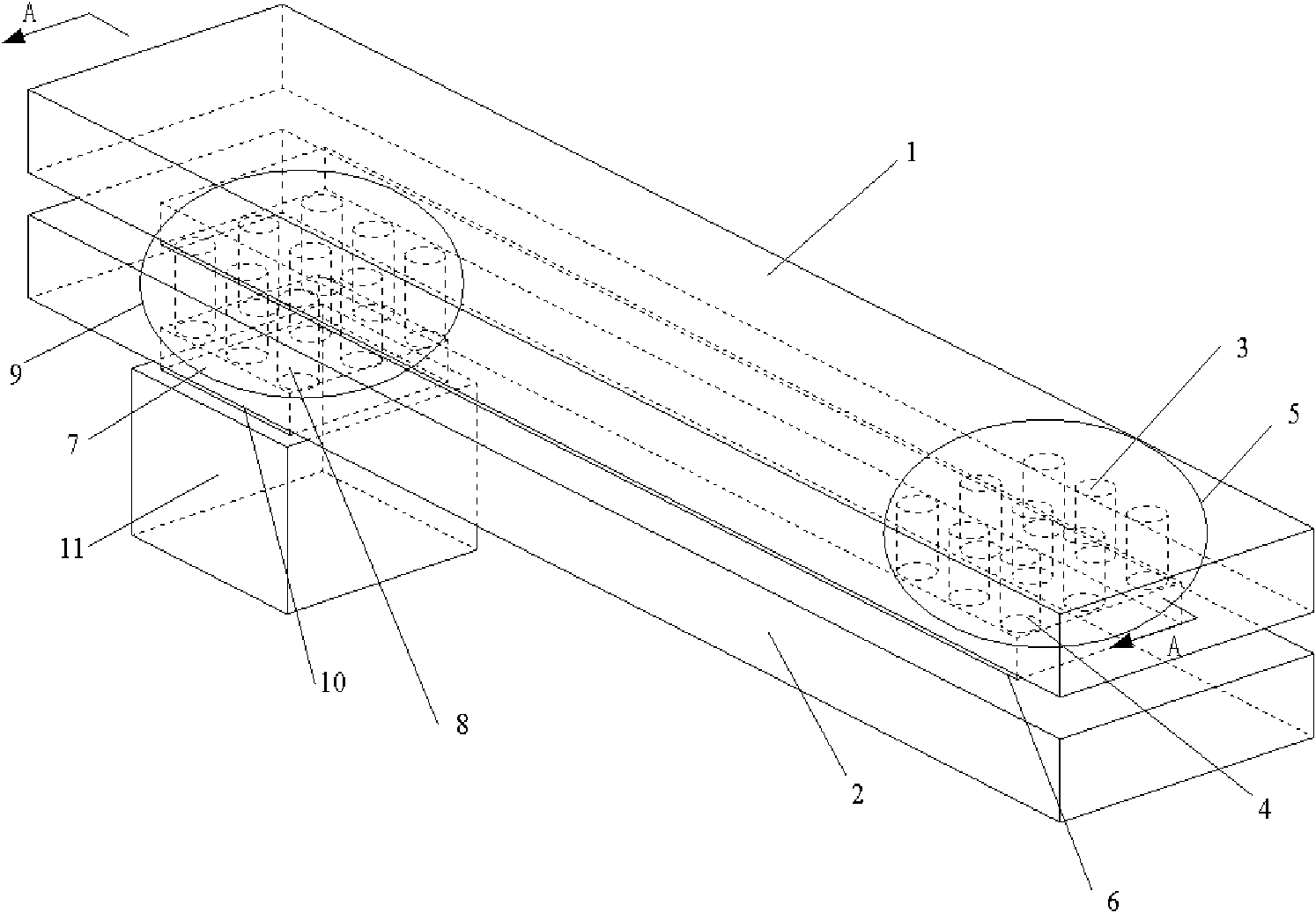

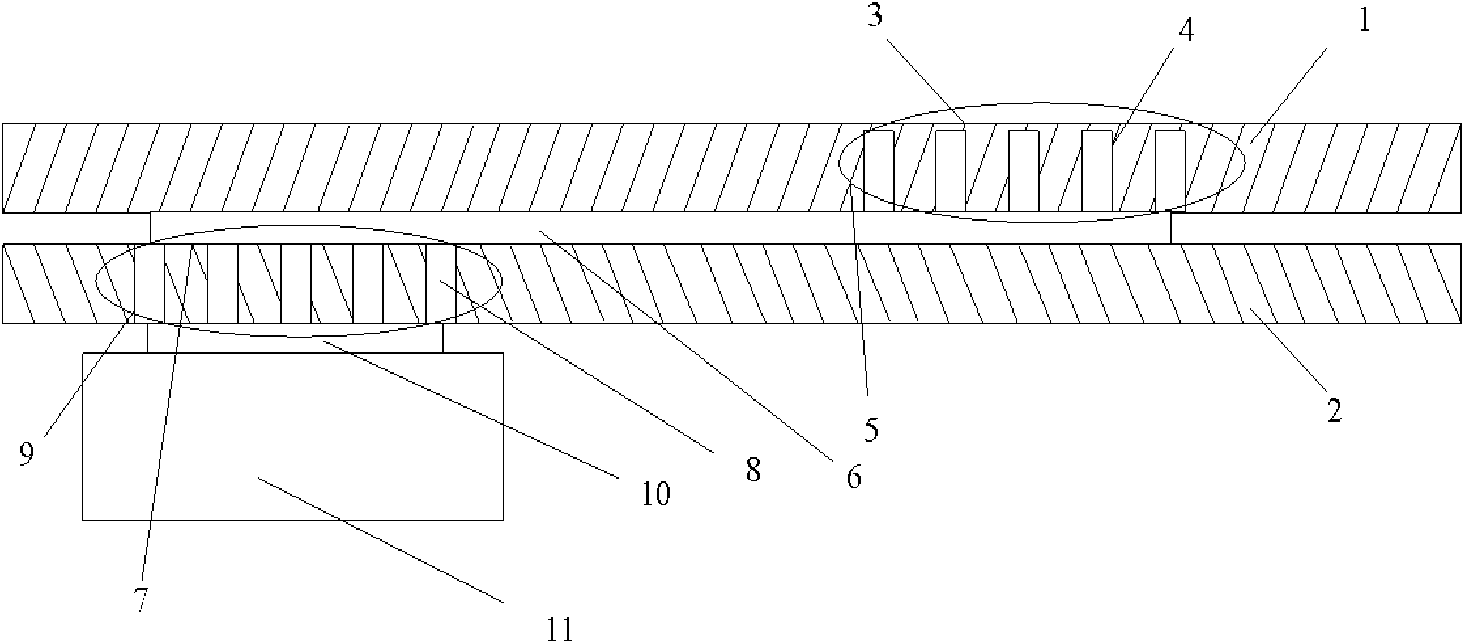

[0023] Such as figure 1 with figure 2 As shown, the refrigeration structure used for microelectronic three-dimensional packaging includes: an upper stacked chip 1 and a lower stacked chip 2, a first vertical metal heat dissipation channel array 5, a second vertical metal heat dissipation channel array 9 and a horizontal metal heat dissipation channel array 6 , wherein: the lower surface of the upper stacked chip 1 and the upper surface of the lower stacked chip 2 are respectively provided with a first vertical metal heat dissipation channel array 5 and a second vertical metal heat dissipation channel array 9, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More