Simulation test method of integrated circuits

An integrated circuit, simulation testing technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of affecting the progress of chip design, time-consuming, lack of recovery, etc., to achieve the effect of shortening the simulation time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

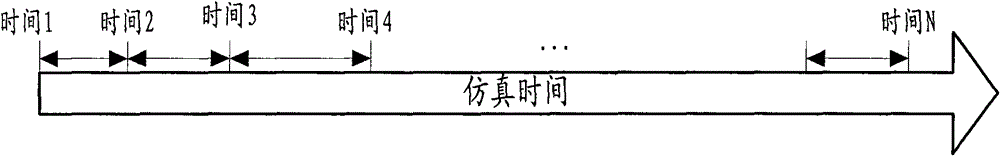

[0030] Such as figure 1 As shown, the present invention divides the simulation test time into a plurality of simulation sections, saves the data of the simulation site at different time points specified, and then enables the multi-thread simulation program, and each thread recovers the simulation data of a time point to start the simulation test. The original single-threaded simulation process is divided into multiple simulation threads that can be executed in parallel, which greatly reduces the time for re-simulation.

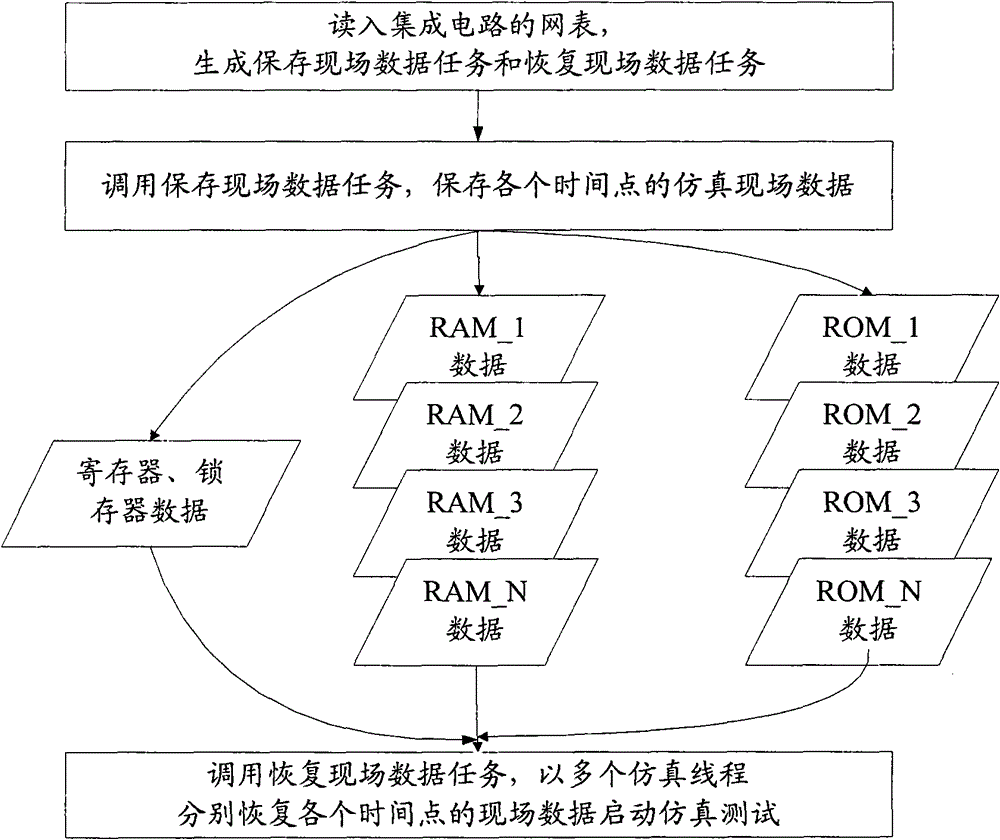

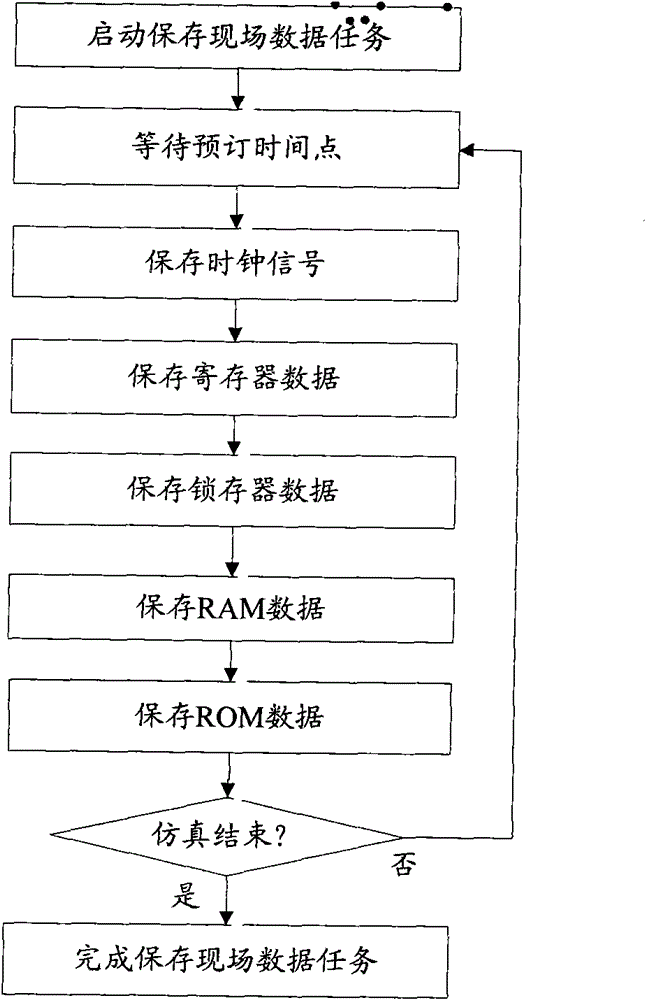

[0031] Such as figure 2 As shown, the realization of the present invention can be divided into the following three stages:

[0032] Phase 1: Data Preparation

[0033] This stage is mainly to generate lists of various data types, and generate verilog tasks for data saving (save) and data restoration (restore) based on these lists. The specific process is as follows:

[0034] (1), read the netlist (netlist) of the integrated circuit through EDA software, acc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More