Multiple-valued counter unit based on nerve MOS tube and multi-digit multiple-valued counter

A MOS tube and counter technology, applied in the field of multi-bit multi-value counters, can solve the problems of high cost, high power consumption, and cumbersome design of counters, and achieve the effect of saving quantity, reducing cost and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

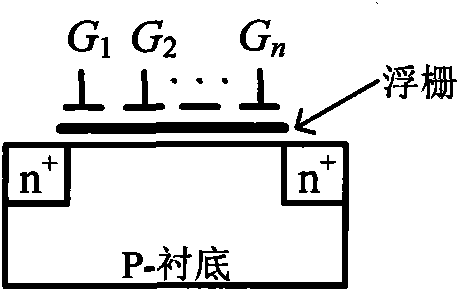

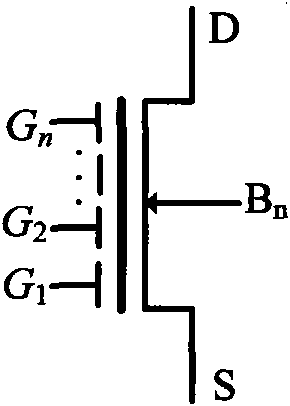

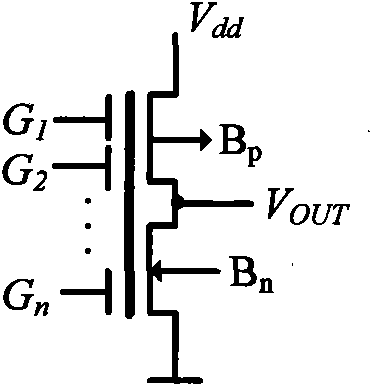

Method used

Image

Examples

Embodiment 1

[0020] Embodiment 1: A multi-valued counter unit based on neural MOS transistors, comprising a neural MOS source follower 1 and a unit trigger circuit connected to the input control gate of the neural MOS source follower, the unit trigger circuit includes the first A binary D flip-flop 2, a second binary D flip-flop 3, an AND gate 4 and an OR gate 5, the second input terminal C of the first binary D flip-flop 2 0 and the second input C of the second binary D flip-flop 3 1 And connected to the clock signal input terminal CP, the first input terminal D of the first binary D flip-flop 2 0 and the second output terminal Q of the second binary D flip-flop 3 1 connection, the first input D of the second binary D flip-flop 3 1 and the first output terminal Q of the first binary D flip-flop 2 0 Connected to the first input terminal of OR gate 5 in parallel, the second output terminal Q of the first binary D flip-flop 2 0 And the first input terminal of AND gate 4 is connected, and...

Embodiment 2

[0021] Embodiment two: a kind of multi-bit multi-valued counter based on neural MOS tube, including two first multi-valued counter unit 10 and the second multi-valued counter unit 20 connected in series, the clock input of the second multi-valued counter unit 20 The terminal CP2 is connected with the first multi-valued counter unit 10 through an auxiliary AND gate 6, and the first multi-valued counter unit 10 includes a neural MOS source follower 11 and an input control gate connected to the neural MOS source follower. A unit trigger circuit, the unit trigger circuit includes a first binary D flip-flop 21, a second binary D flip-flop 31, an AND gate 41 and an OR gate 51, the second input terminal C of the first binary D flip-flop 21 01 and the second input terminal C of the second binary D flip-flop 31 11 And connected to the clock signal input terminal CP1, the first input terminal D of the first binary D flip-flop 2 01 and the second output terminal Q of the second binary D...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More