Memory circuits and routing of conductive layers thereof

A memory circuit and conductive layer technology, applied in static memory, digital memory information, circuits, etc., can solve problems affecting RC time delay, etc., and achieve the effect of shortening RC time delay, reasonable wiring, and reducing word line resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

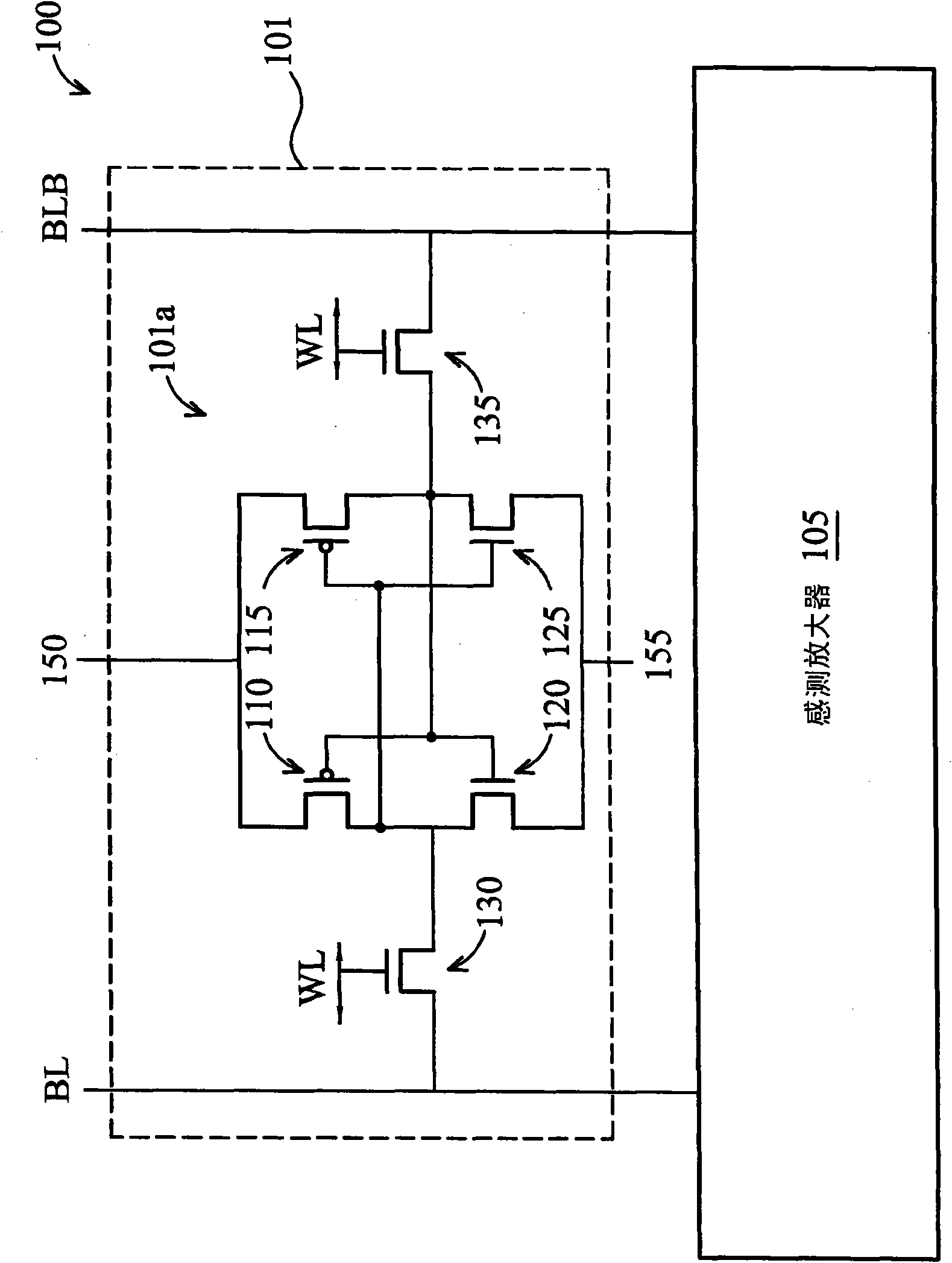

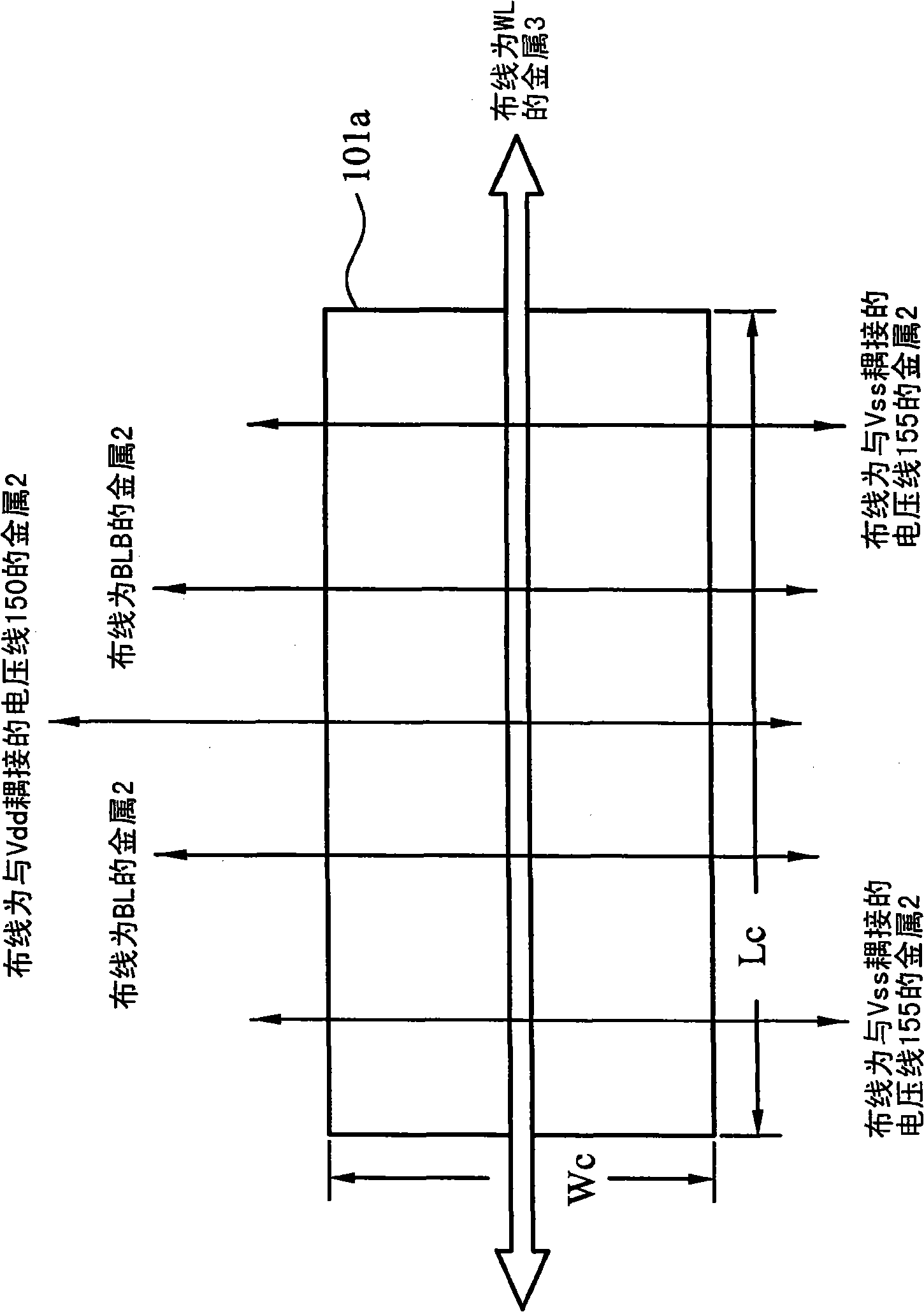

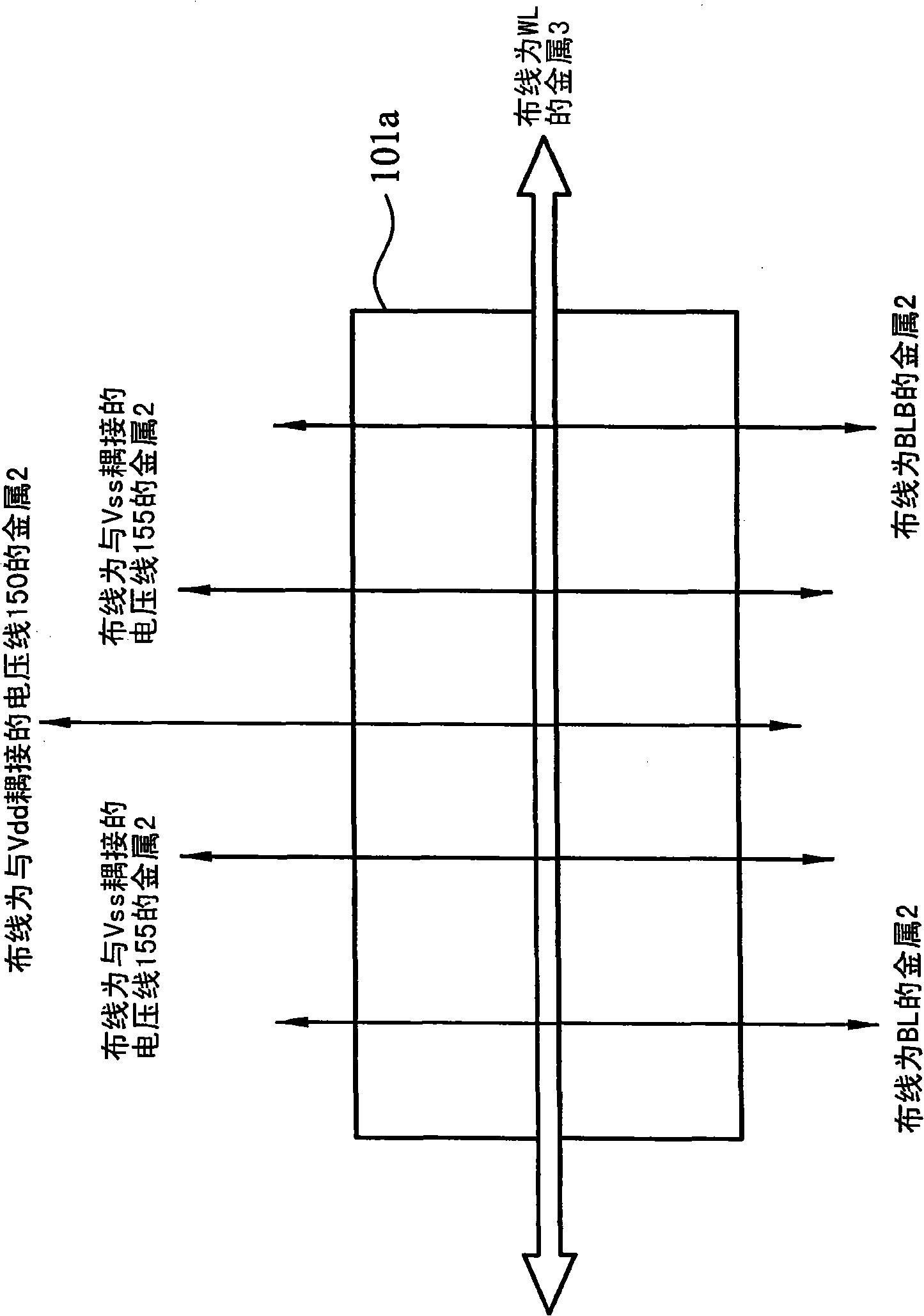

Embodiment Construction

[0034] In order to make the above-mentioned objects, features and advantages of the present invention more comprehensible, preferred embodiments will be described in detail below together with the accompanying drawings.

[0035] It can be appreciated that the following disclosure provides many different embodiments or examples for implementing different features. Specific example combinations and permutations are described below to simplify the present invention. Of course this is only an example and not a limitation. For example, when describing the form of a first feature on a second feature, it may include that the first feature is in direct contact with the second feature, and it may include that an additional feature is formed between the first feature and the second feature such that The first and second features may not be in direct contact. In addition, the present invention may repeat reference numerals and / or letters in various embodiments. These repetitions are f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More