Bidirectional high speed FIFO storage implemented on the basis of FPGA

A memory and high-speed technology, which is applied in the direction of instruments, data conversion, electrical digital data processing, etc., can solve the problems of low integration and slow speed, and achieve the effects of reducing power consumption, fast speed, and system size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

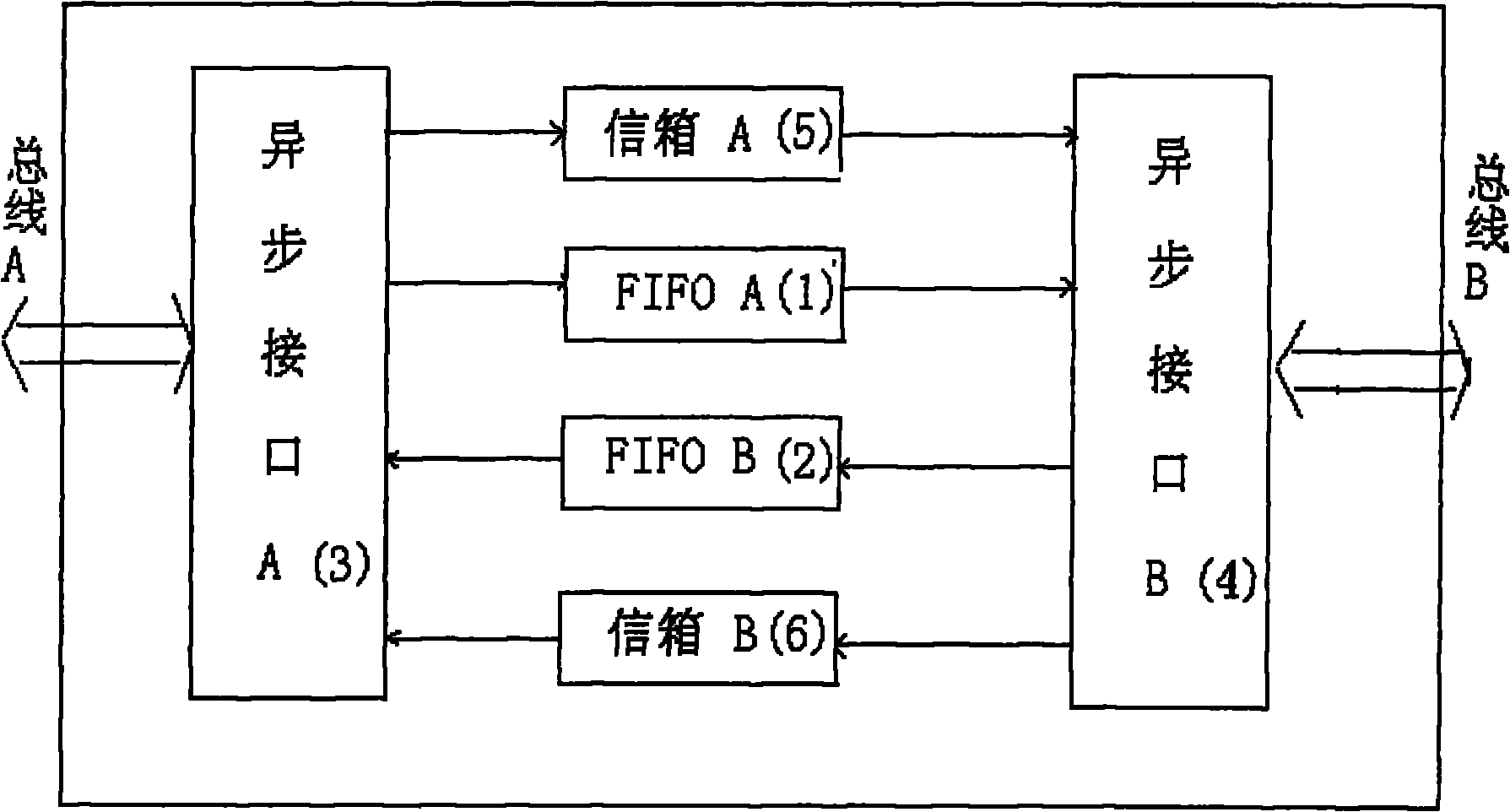

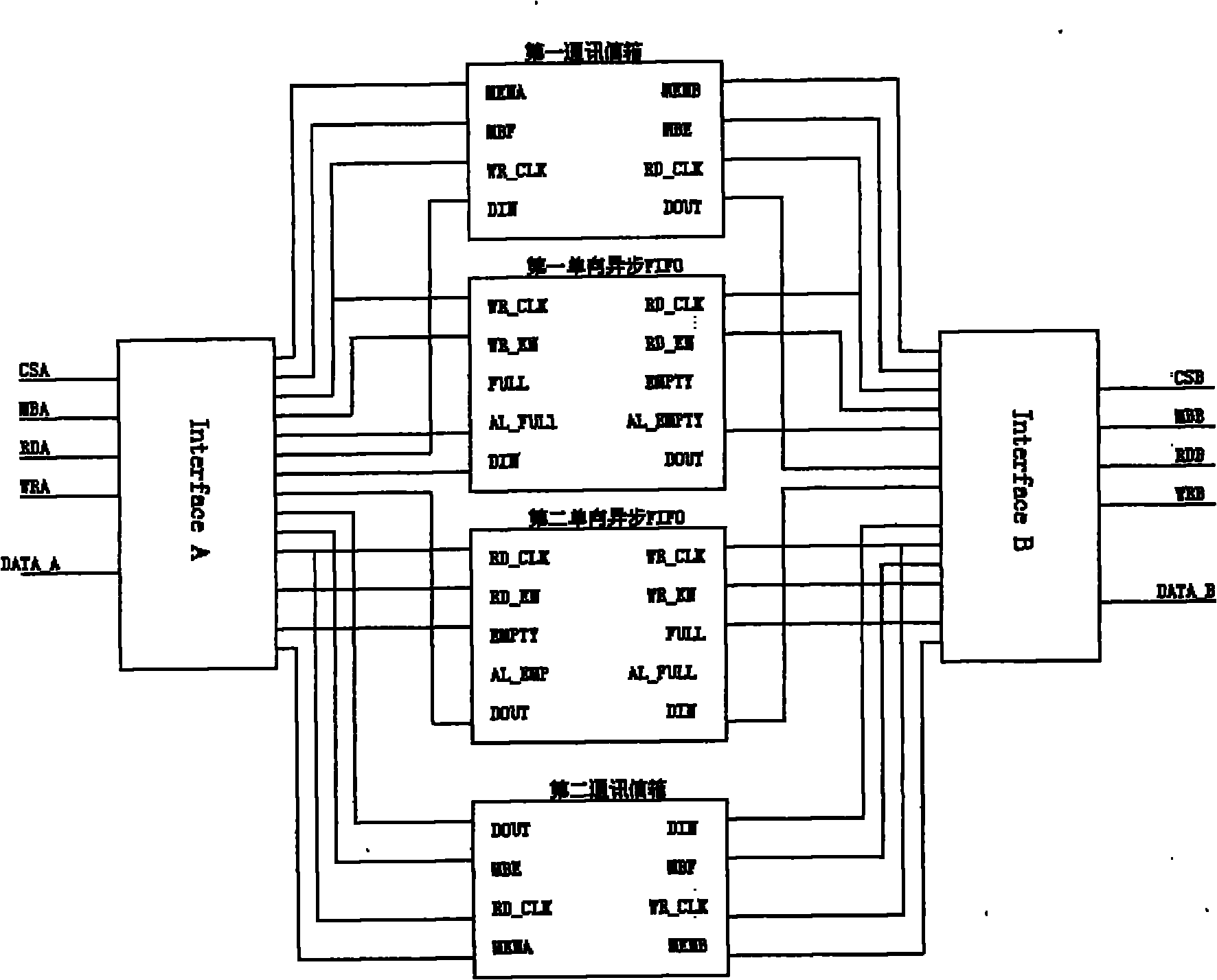

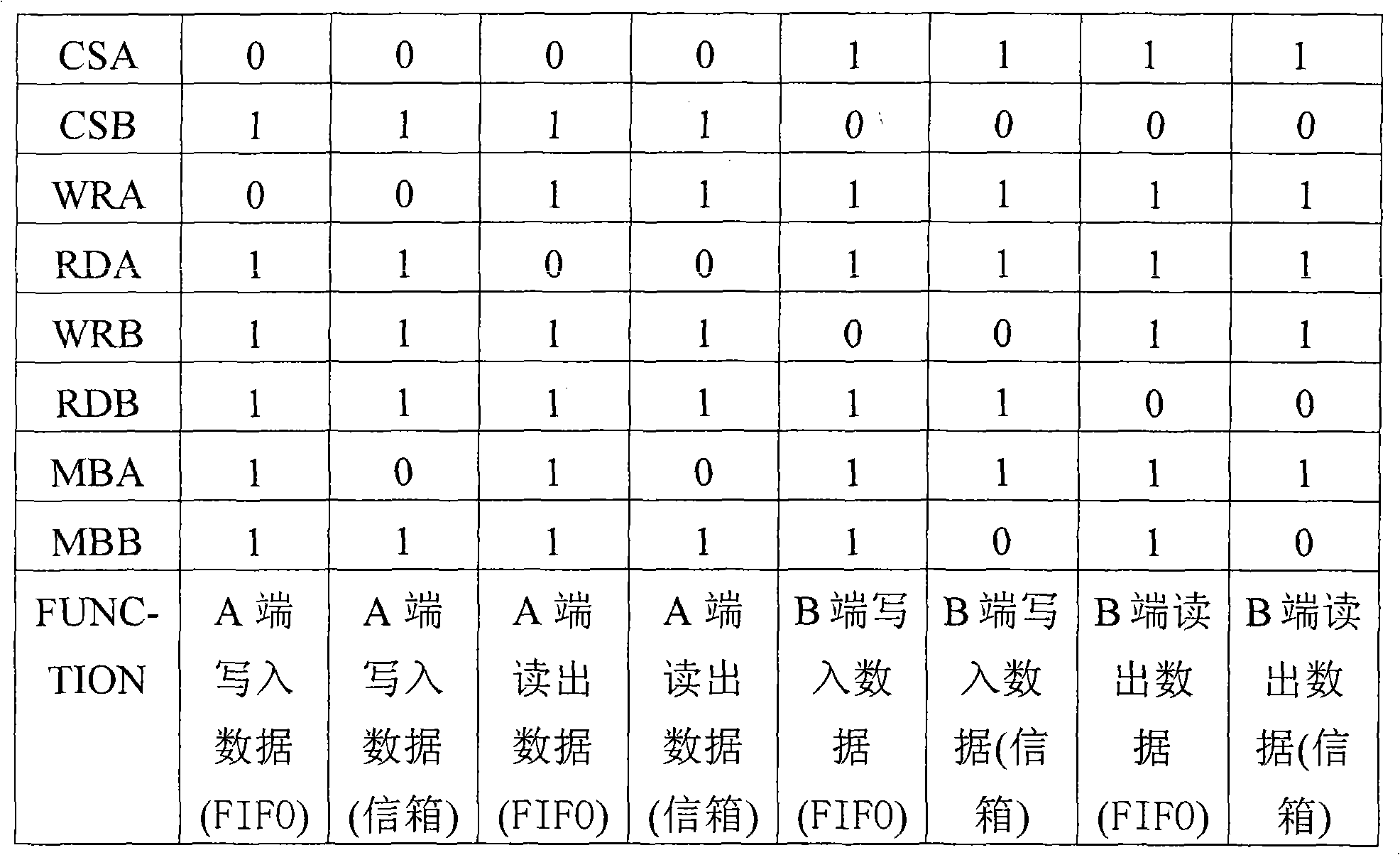

[0040]The bidirectional high-speed FIFO memory based on FPGA provided by the present invention adopts two unidirectional FIFO units to meet the requirement that the first bus A and the second bus B may read and write at the same time, and a communication mailbox is added to solve the problems of special data. Contradictions that are directly output after queuing. One end of the FIFO (i.e. the first one-way asynchronous FIFO read-write module 1 and the second one-way asynchronous FIFO read-write module 2) and the communication mailbox is connected with the first asynchronous bus interface module 3, and the other end is connected with the second asynchronous bus interface Module 4 is connected. The first asynchronous bus i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More