Method and device for increasing read-write rate of double data rate synchronous dynamic random access memory

A double data rate, random access memory technology, applied in the field of data communication, can solve the problems of long activation time of row close, command order adjustment function, complex reordering of DDR read data, and infeasibility.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The technical solutions of the present invention will be clearly and completely described below in conjunction with the accompanying drawings of the present invention.

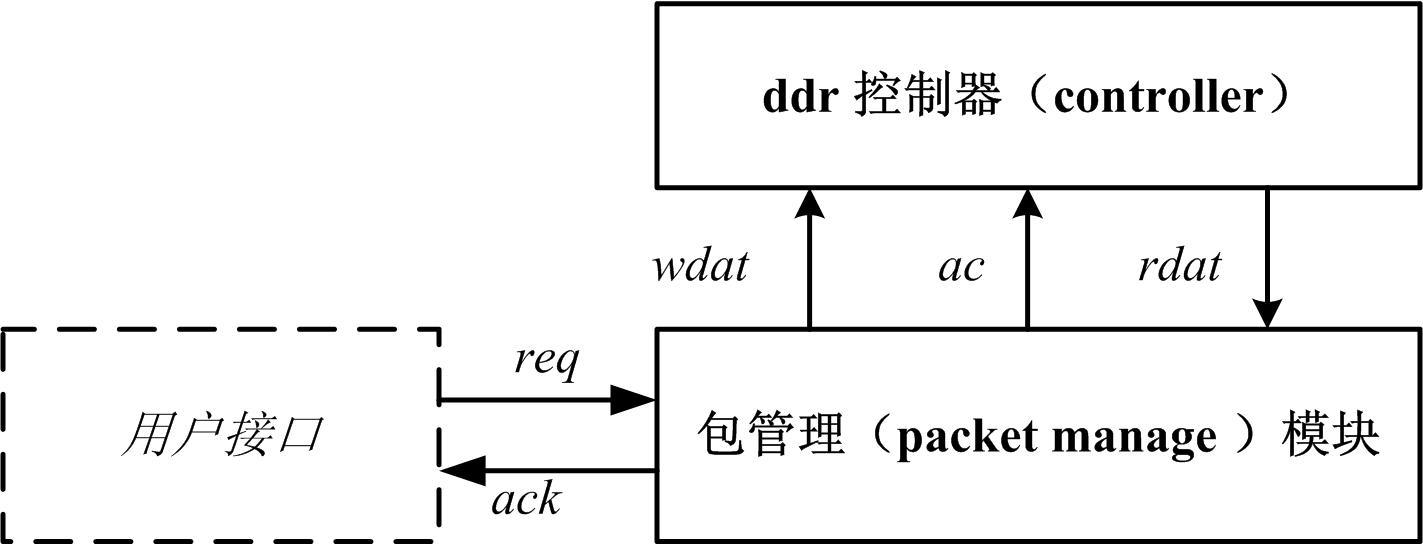

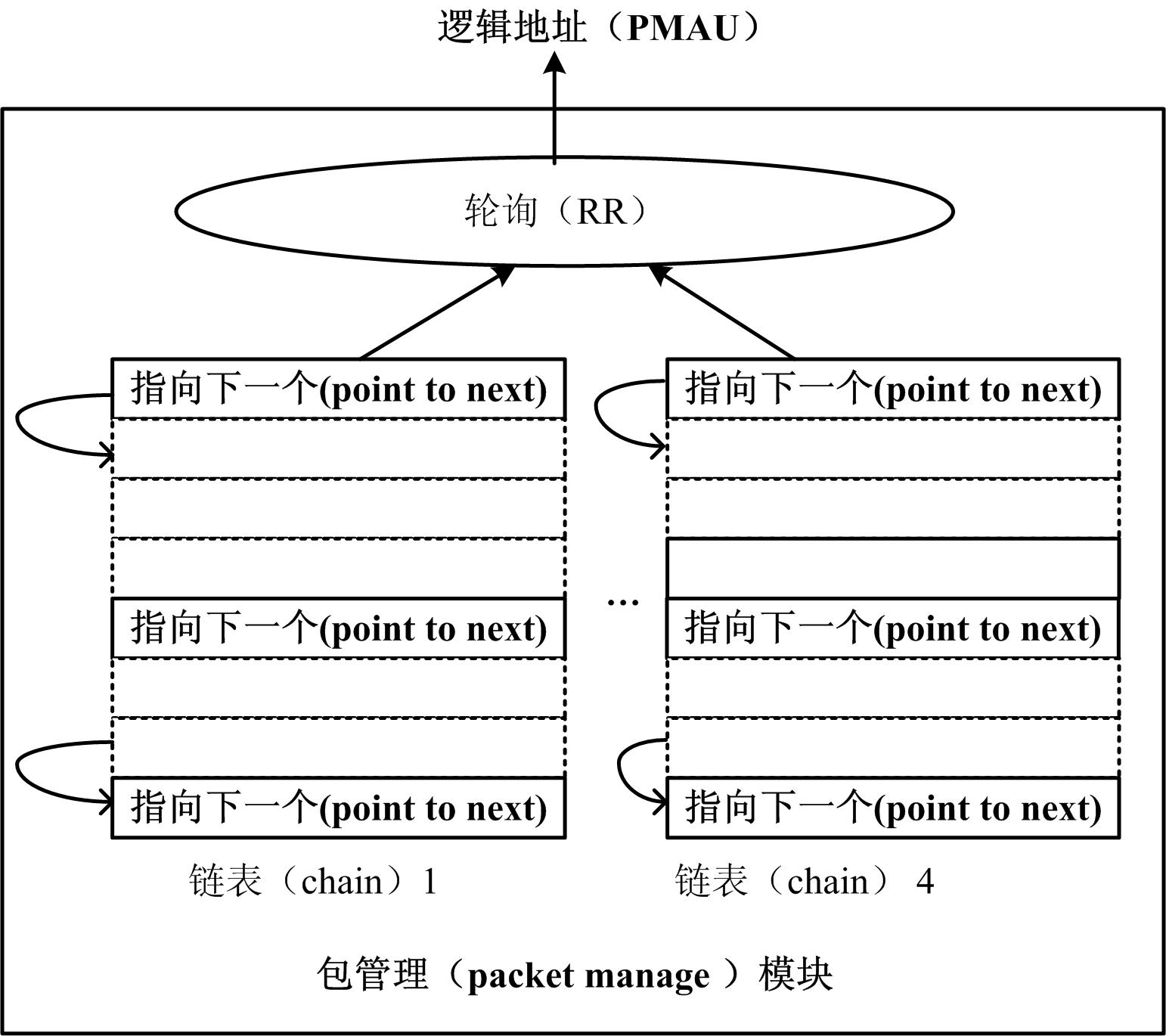

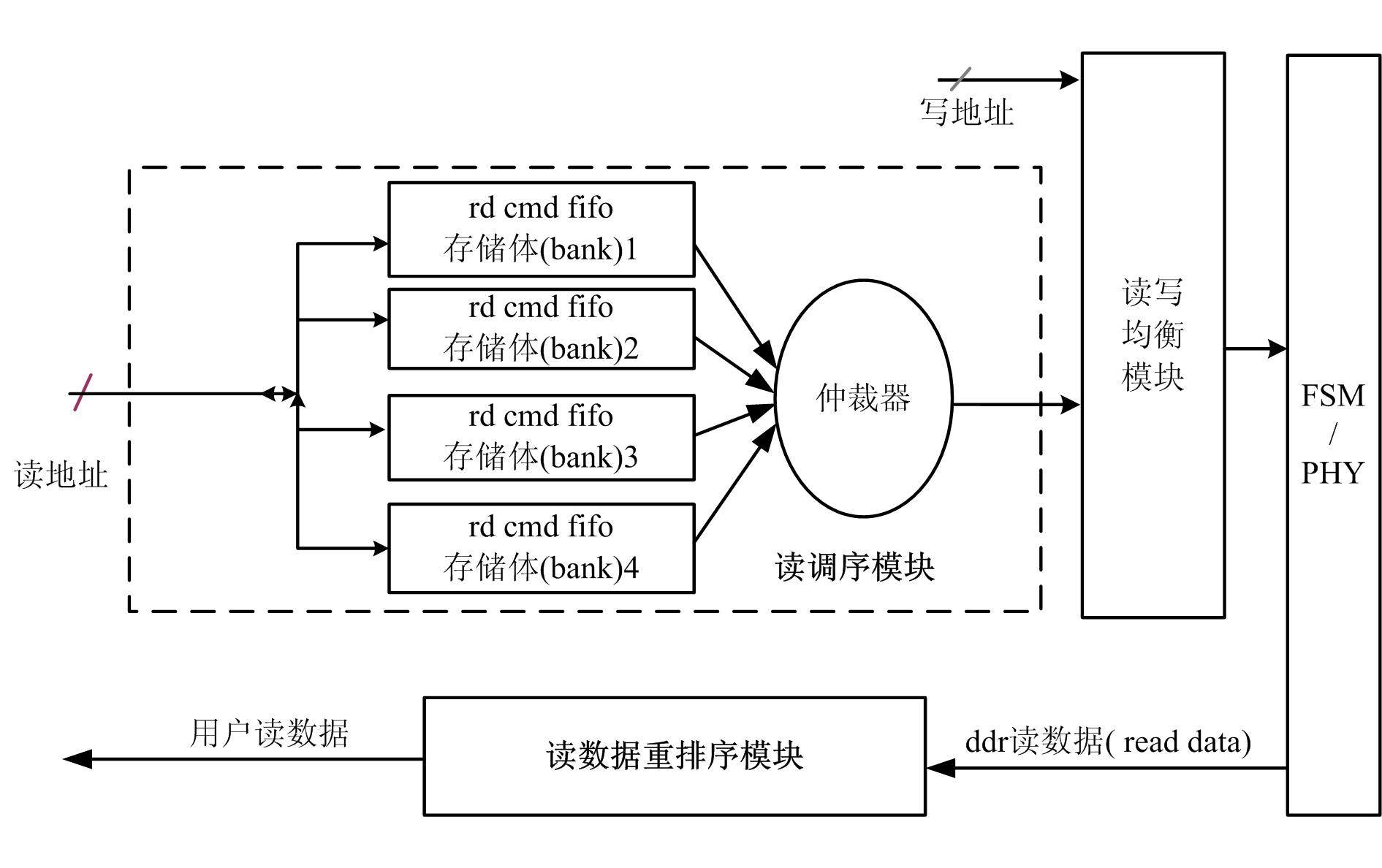

[0044] The present invention proposes a method for managing the logical address of DDR SDRAM using a linked list method. When there is a request for a data packet to be written into the DDR SDRAM, a method of assigning the DDR SDRAM logical write address according to bank polling is adopted. When there is a read request for a data packet When, adjust the read address of the data packet. The strategy of the present invention for polling and assigning the write address of the data packet fundamentally ensures that the write address is already a benign sequence staggered by bank before being sent to the DDR SDRAM, so that the read address of the same data packet will not be caused by the sorting. Prior to the situation where the write address is delivered to the DDR SDRAM; the solution for read address adjust...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More