Method of fabricating high-k/metal gate device

A high-k dielectric and metal gate technology, applied in the field of manufacturing high-k dielectric layers and/or metal gate components, can solve the problems of high-k gate dielectric layer quality degradation and achieve Improved etching process, cost-effective effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to make the present invention more comprehensible, the following specific embodiments are described in detail in conjunction with the accompanying drawings as follows:

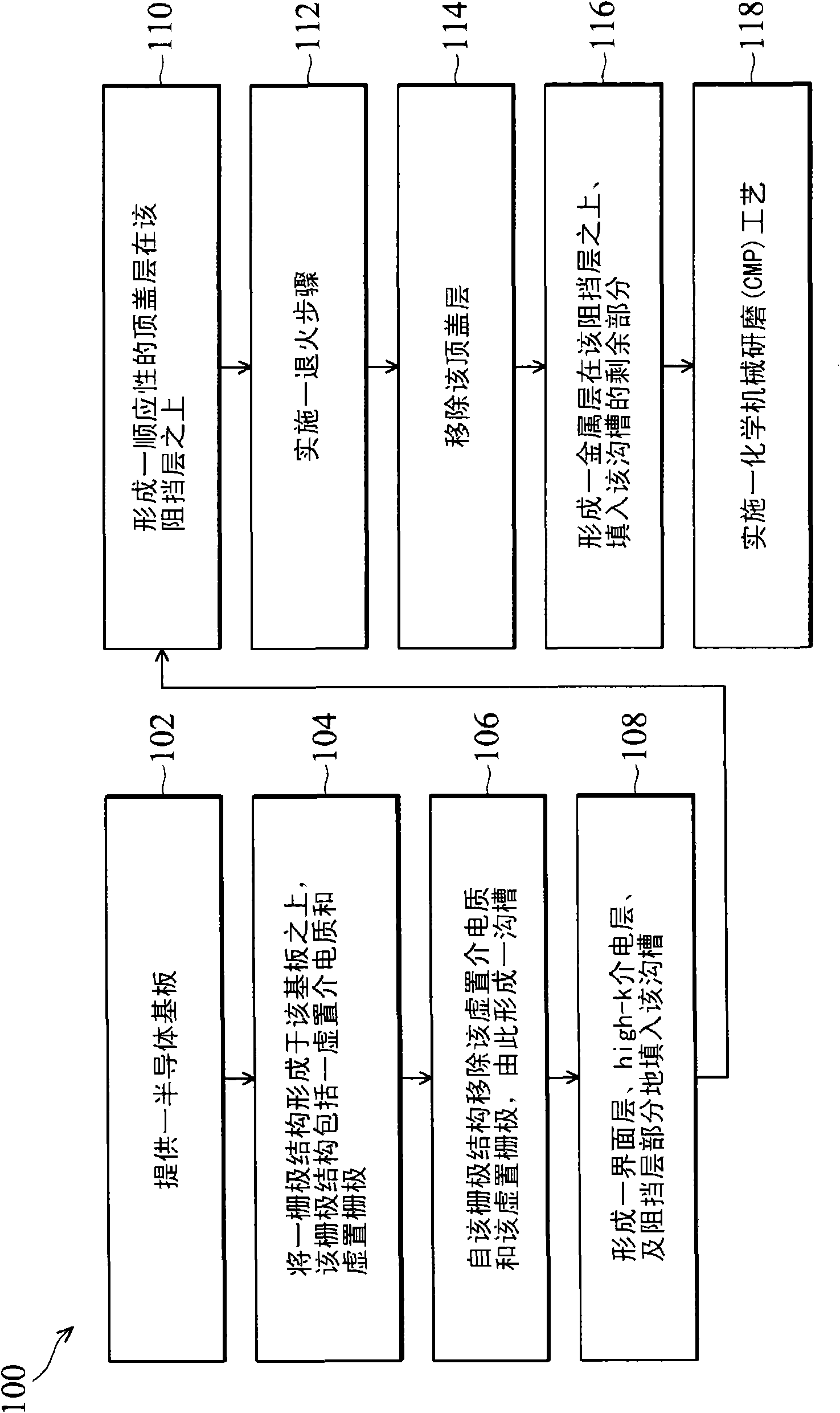

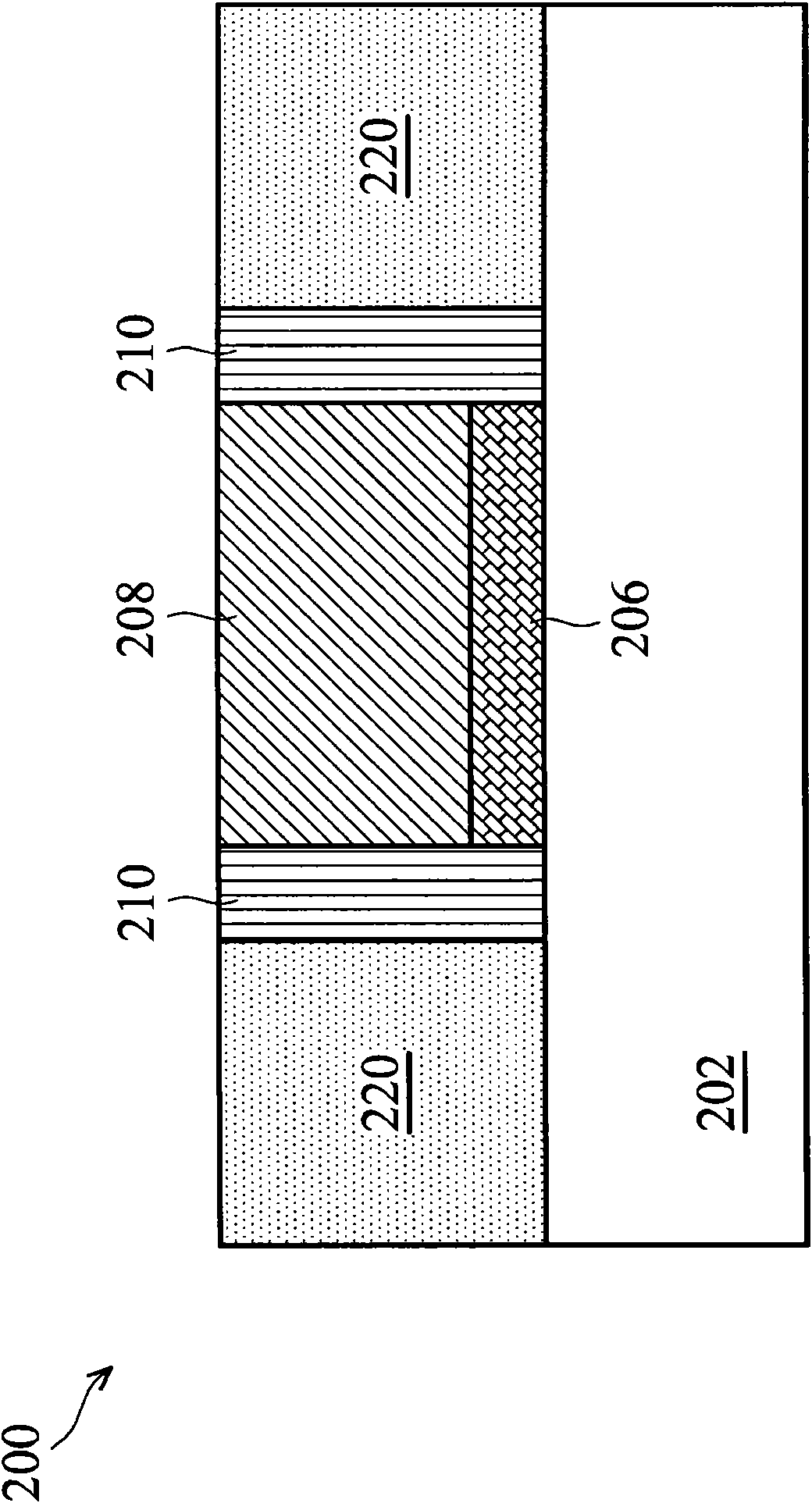

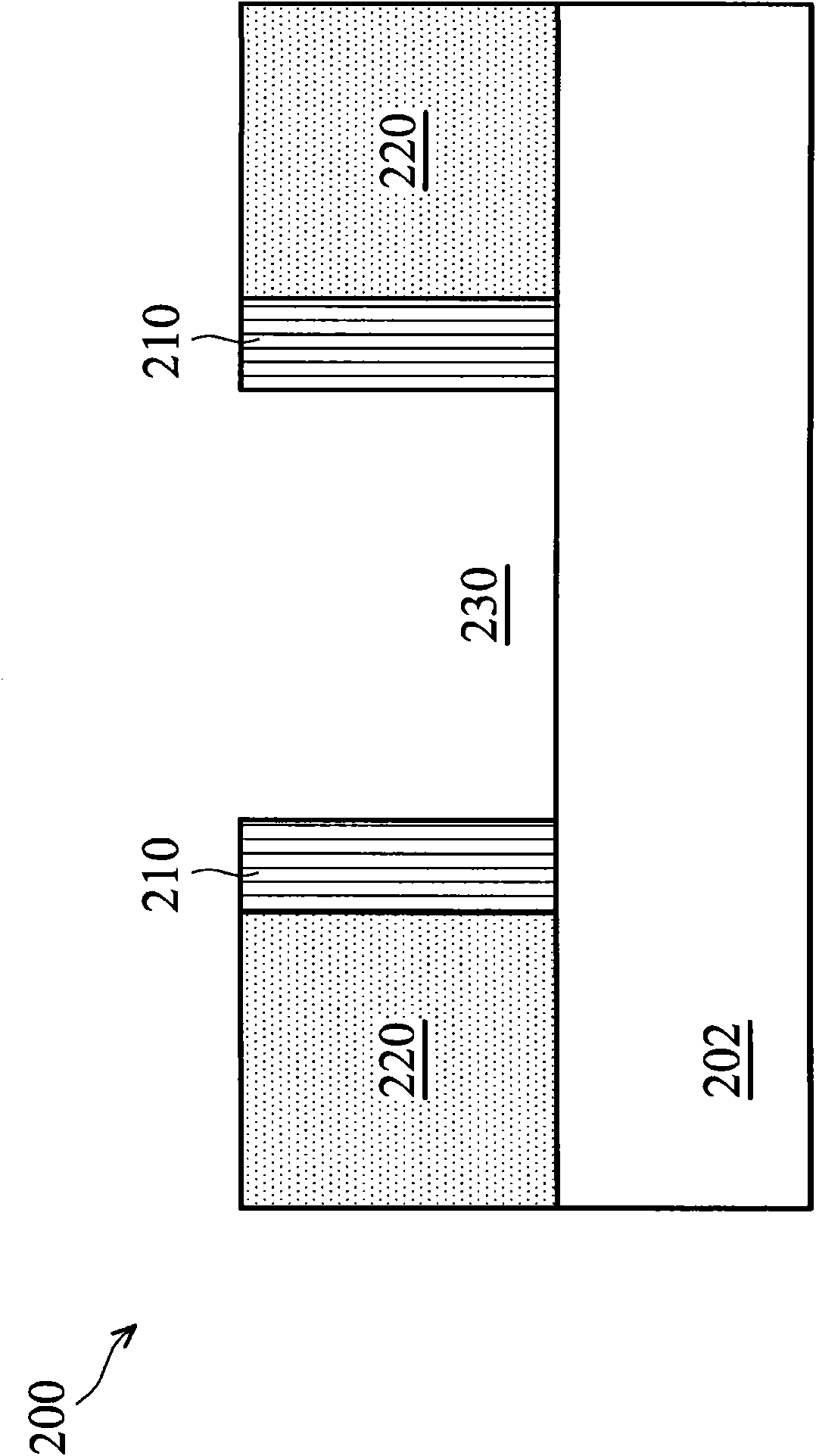

[0037] Hereinafter, each embodiment is described in detail and examples accompanied by drawings are used as a reference basis of the present invention. In the drawings or descriptions of the specification, the same reference numerals are used for similar or identical parts. And in the drawings, the shapes or thicknesses of the embodiments may be enlarged, and marked for simplicity or convenience. Furthermore, the parts of each element in the drawings will be described separately. It should be noted that the elements not shown or described in the drawings are forms known to those skilled in the art. In addition, specific embodiments only The specific method used in the present invention is disclosed, and it is not intended to limit the present invention. Furthermore, embodiments of the "gate-l...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More