High-speed low-power consumption latch device capable of resisting SEU (single event upset)

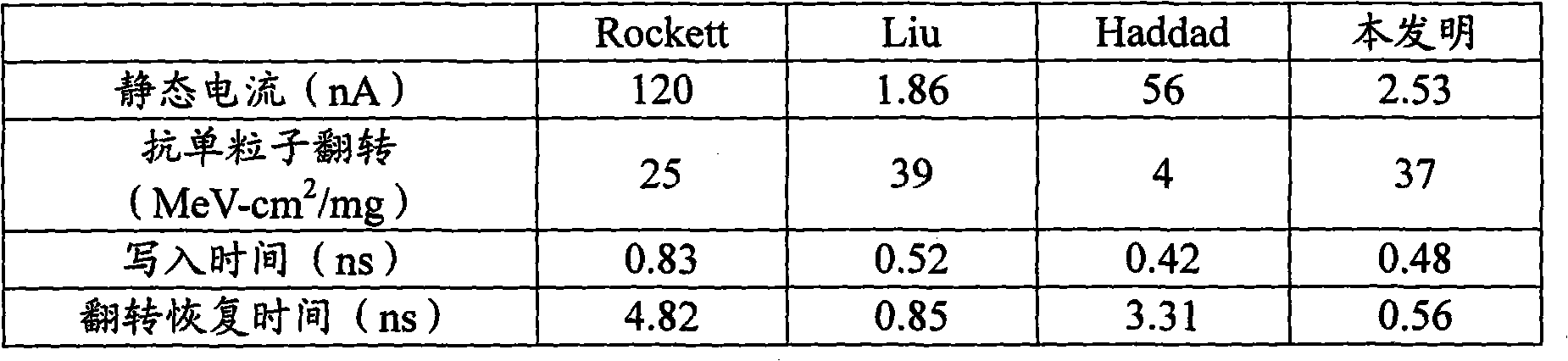

An anti-single event and latch technology, applied in electrical components, logic circuits, pulse technology, etc., can solve the problems of backward integration, lower storage unit writing speed, large quiescent current, etc., and achieve quiescent current and power consumption Small, fast flip recovery time, effect of less transistor count

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0015] In the embodiment of the present invention, under common process conditions, redundant storage nodes are introduced into the latch, and when a node is flipped, the voltage of the node can be recovered from other nodes through feedback.

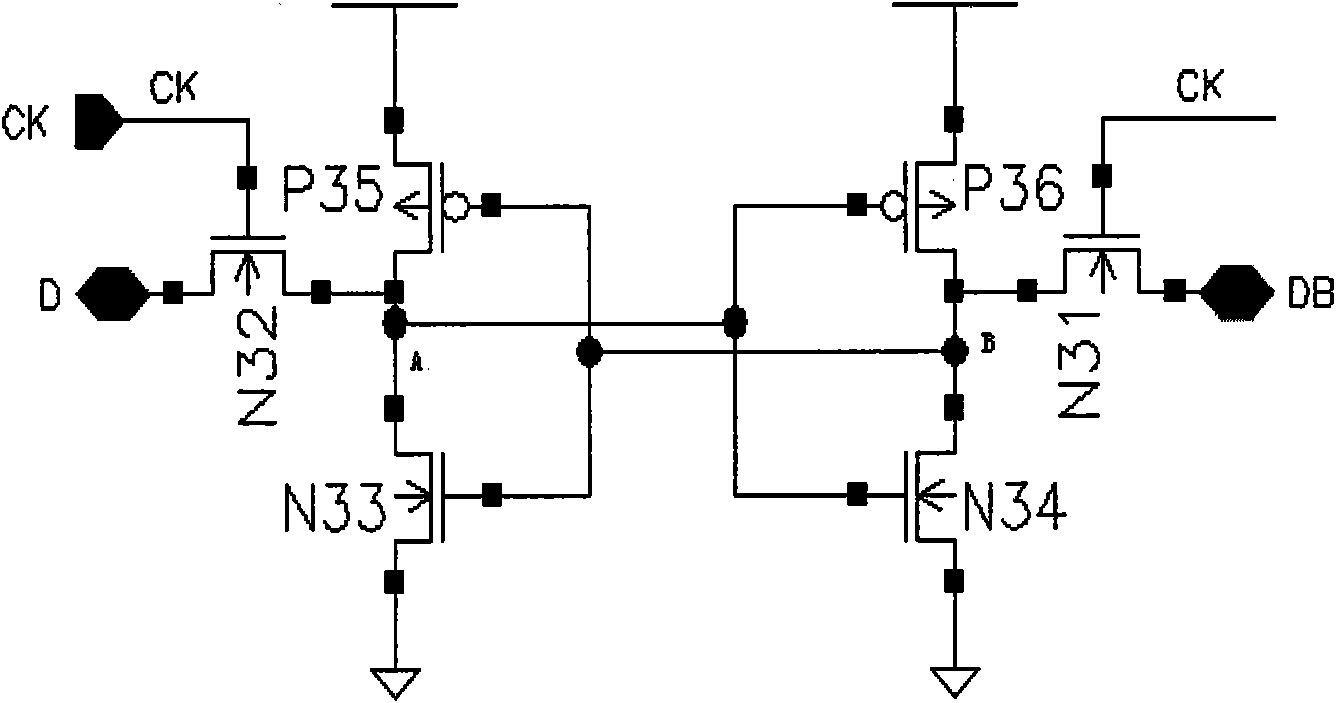

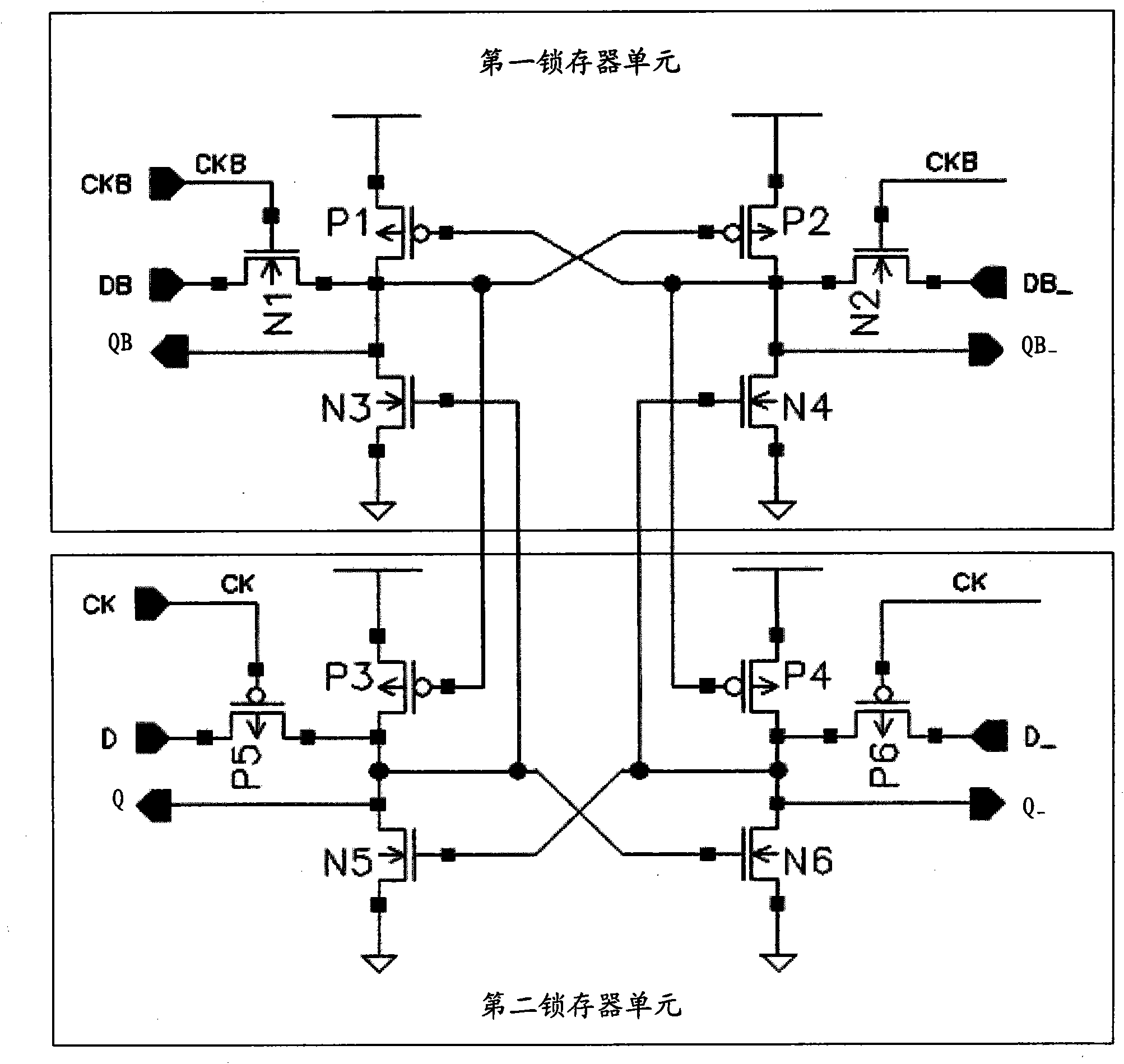

[0016] figure 2 A circuit principle using a design-hardened latch provided by the embodiment of the present invention is shown. Please refer to figure 2 , the latch includes a first latch unit and a second latch unit that are cross-coupled, wherein the clock signal of the first latch unit and the clock signal of the second latch unit are opposite to each...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More