Power MOS transistor of asymmetric structure and array thereof

A MOS transistor and power technology, which is applied in the field of power field effect transistor preparation, can solve the problems of large layout area and achieve the effect of reducing the distance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The present invention will be further described below in conjunction with the examples, but the present invention is not limited to the following examples.

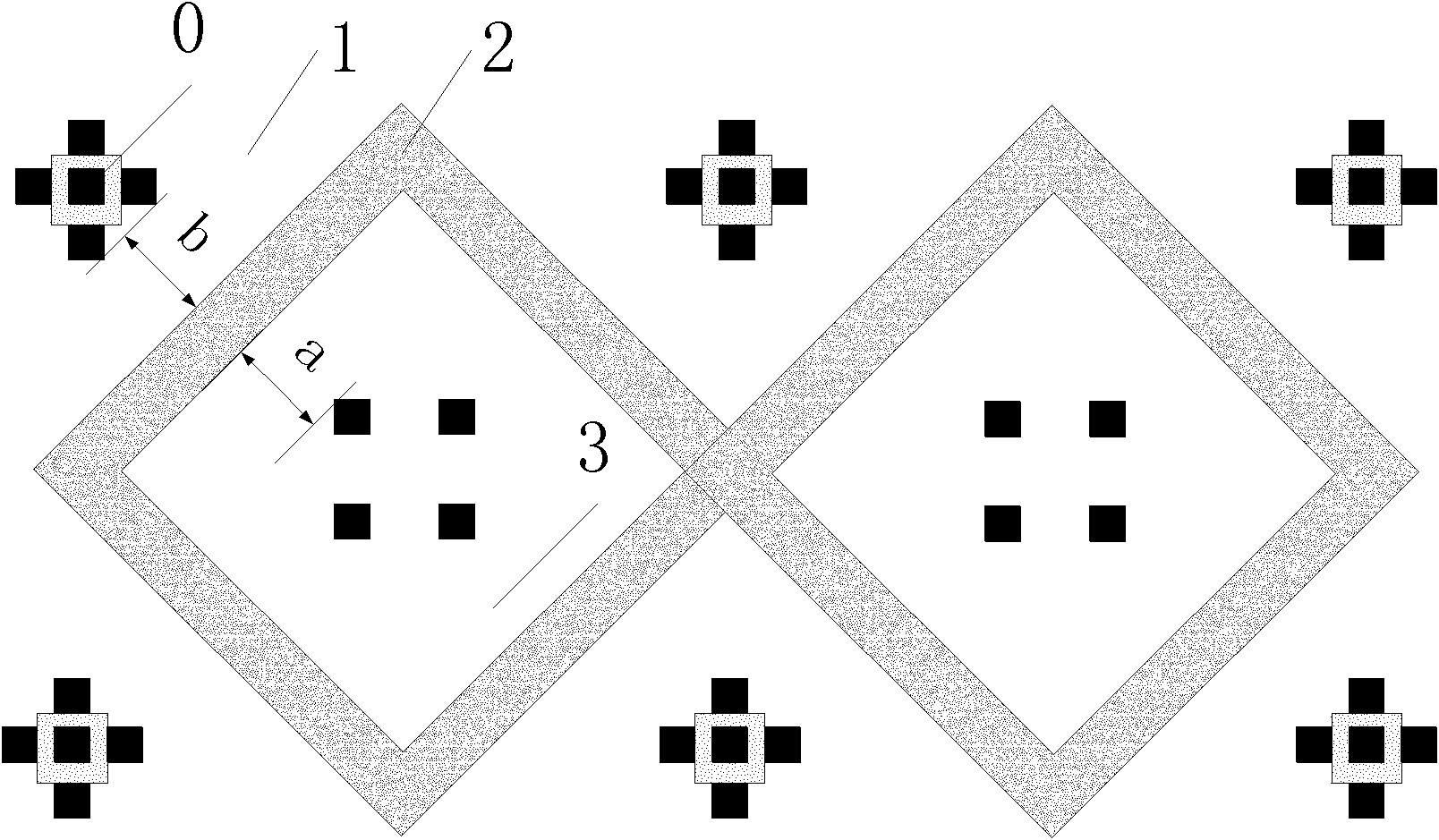

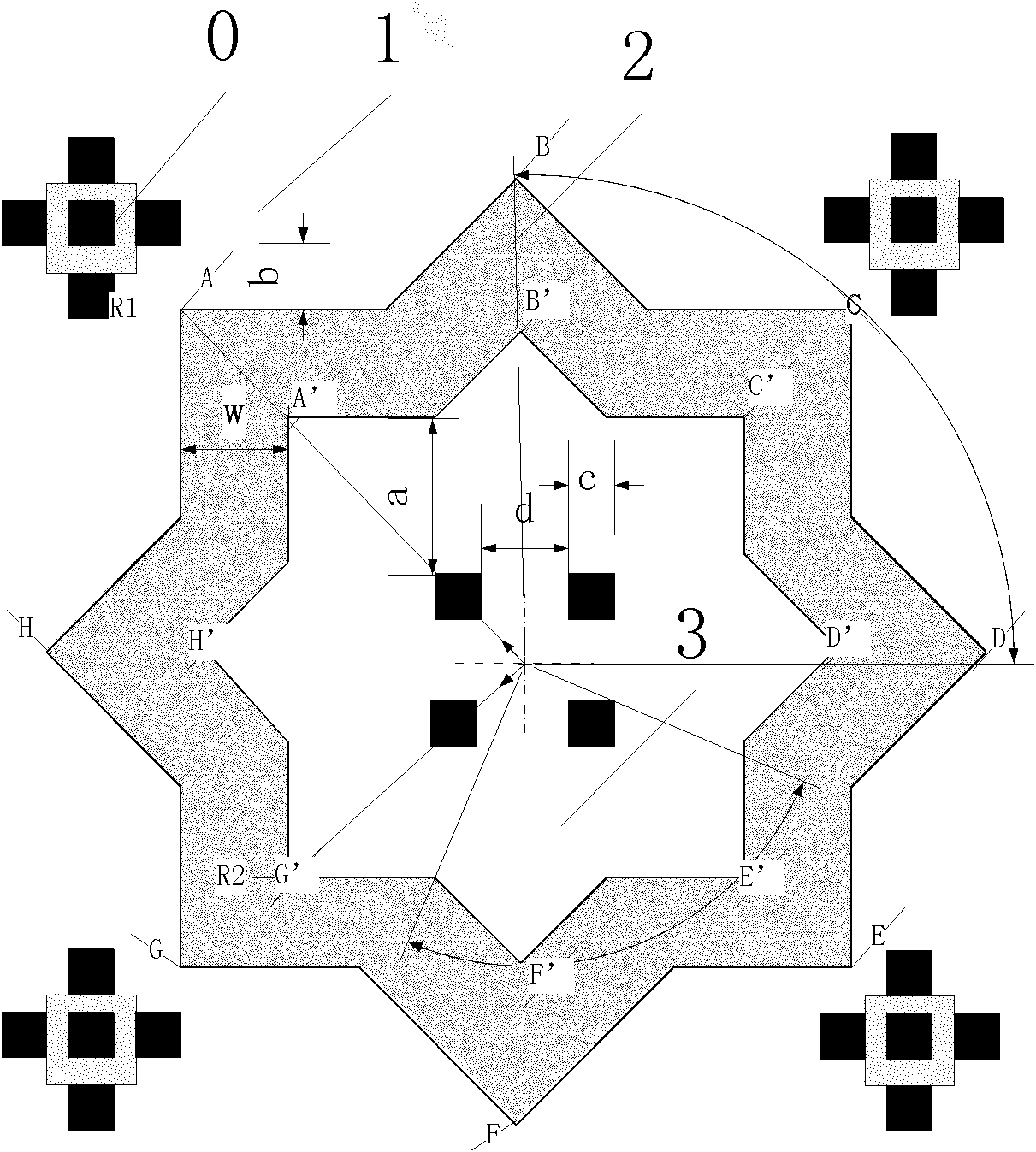

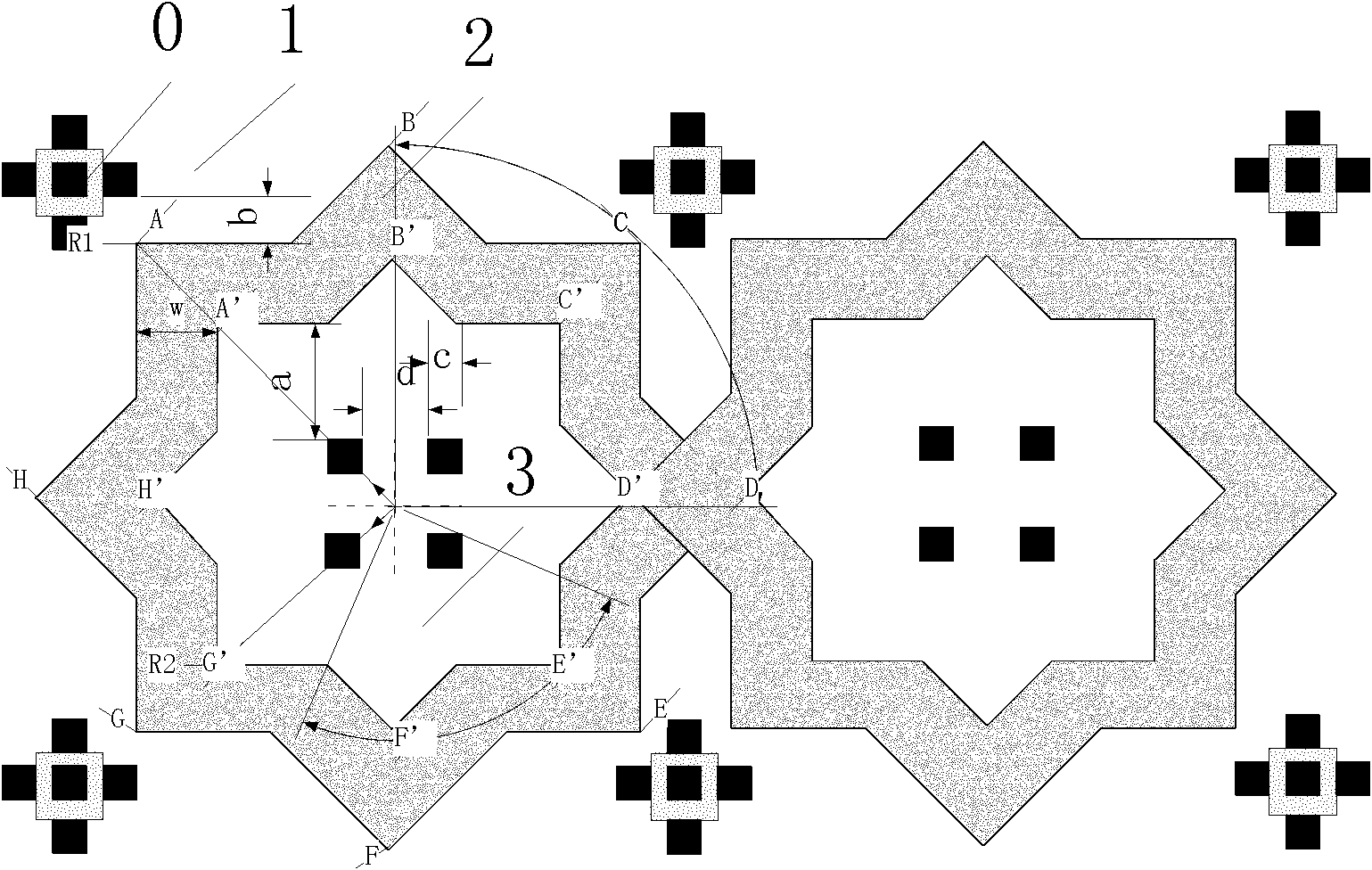

[0016] Take Chartered Semiconductor's 0.35um process as an example. refer to image 3 , Power MOS transistor ESD requirements, the minimum distance from the drain contact hole to the gate structure a=1.7um, the minimum distance from the source contact hole to the gate structure b=0.7um, the width of the gate structure w=0.5um, the drain contact hole The minimum size and minimum pitch is 0.4um.

[0017] Concrete realization of the present invention, by above parameter, with:

[0018] is the radius, and the geometric center of the layout is the center to make a circle. Then do 0 degree, 45 degree, 90 degree, 135 degree straight line and circle intersect to get A, B, C, D, E, F, G and H (135 degree point is A, then marked clockwise), then Respectively connect A, C, E, G and B, D, F, H to form a hexagonal octagon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More