Basic input/output system (bios) and interrupt realizing method for Loongson central processing unit (CPU) mainboard

A technology of Godson and mainboard, applied in the field of mainboard bios and interrupt realization, which can solve problems such as interrupt distribution and achieve the effect of ensuring normal operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

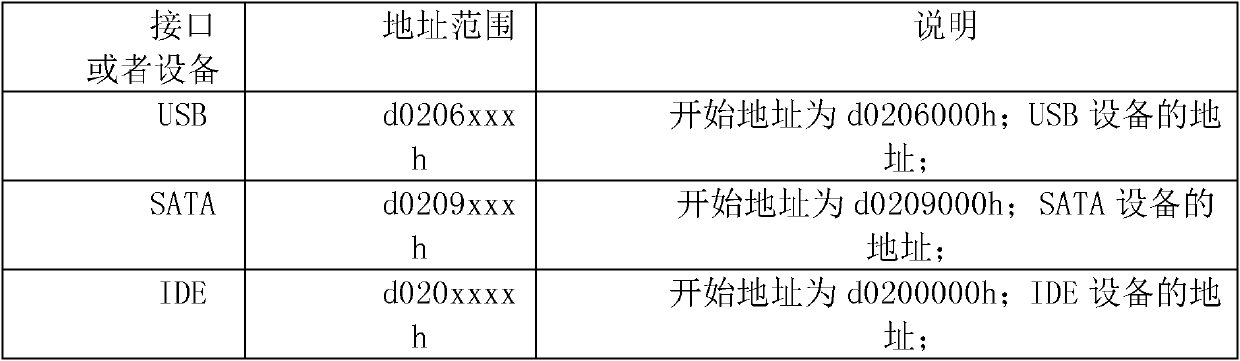

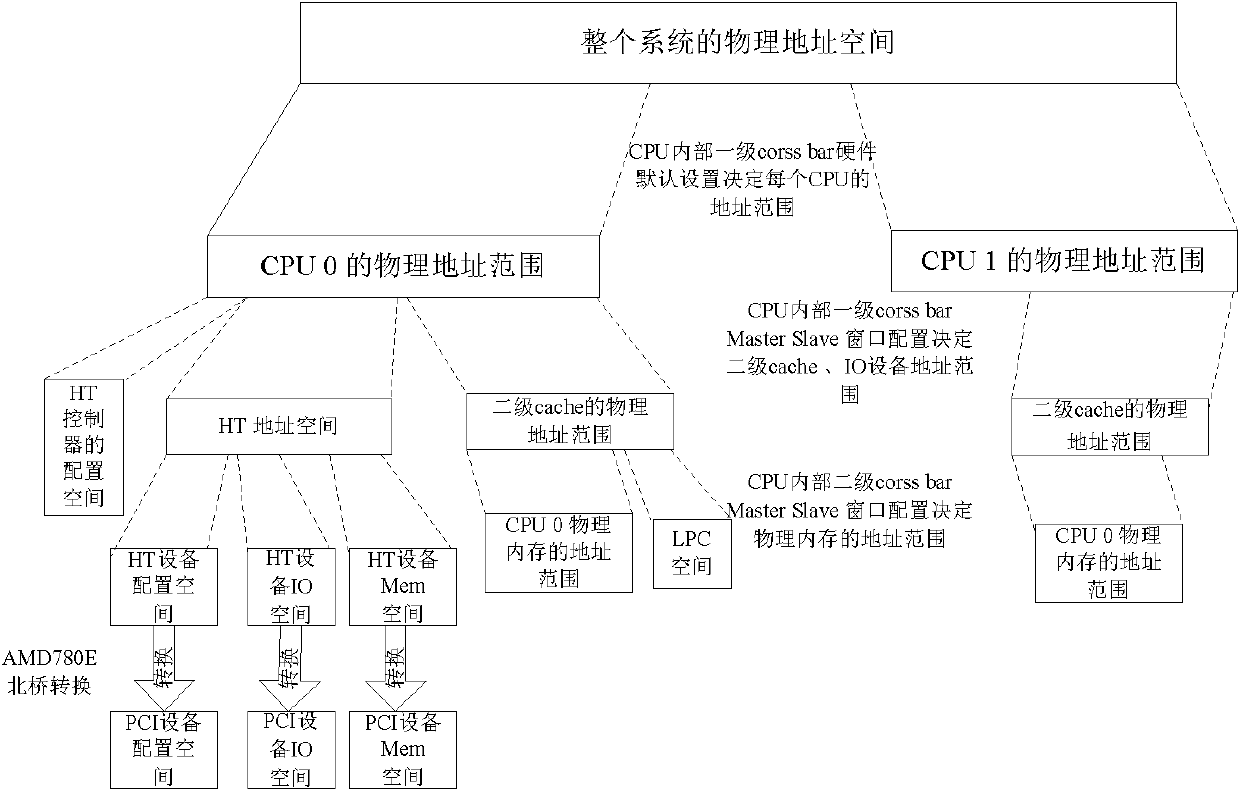

[0040] 1. Conversion of Loongson CPU and Northbridge address mapping

[0041] In the x86 platform, the address of the system is divided into physical address, bus address and virtual address. In Linux, the 4GB (virtual) memory of a process is divided into user space and kernel space. The user space is distributed from 0 to 3GB (that is, PAGE_OFFSET, which is equal to 0xC0000000 in 0X86), and the remaining 1G is the kernel space. Programmers can only use virtual addresses. Each process in the system has its own private user space (0~3G), which is invisible to other processes in the system. The address when the CPU issues an instruction fetch request is the virtual address of the current context, and the MMU then finds the physical address of the virtual address from the page table to complete the instruction fetch. Moreover, the x86 platform uses a technology called memory mapping (MMIO), which is part of the PCI specification. The IO device port is mapped to the memory spac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More