High-reliability power supply clamping ESD (Electronic Static Discharge) protection circuit

An ESD protection and reliability technology, applied in emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, circuit devices, etc., can solve internal circuit damage, incomplete release, and shortened Mbig turn-on time and other problems, to achieve the effect of long opening time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

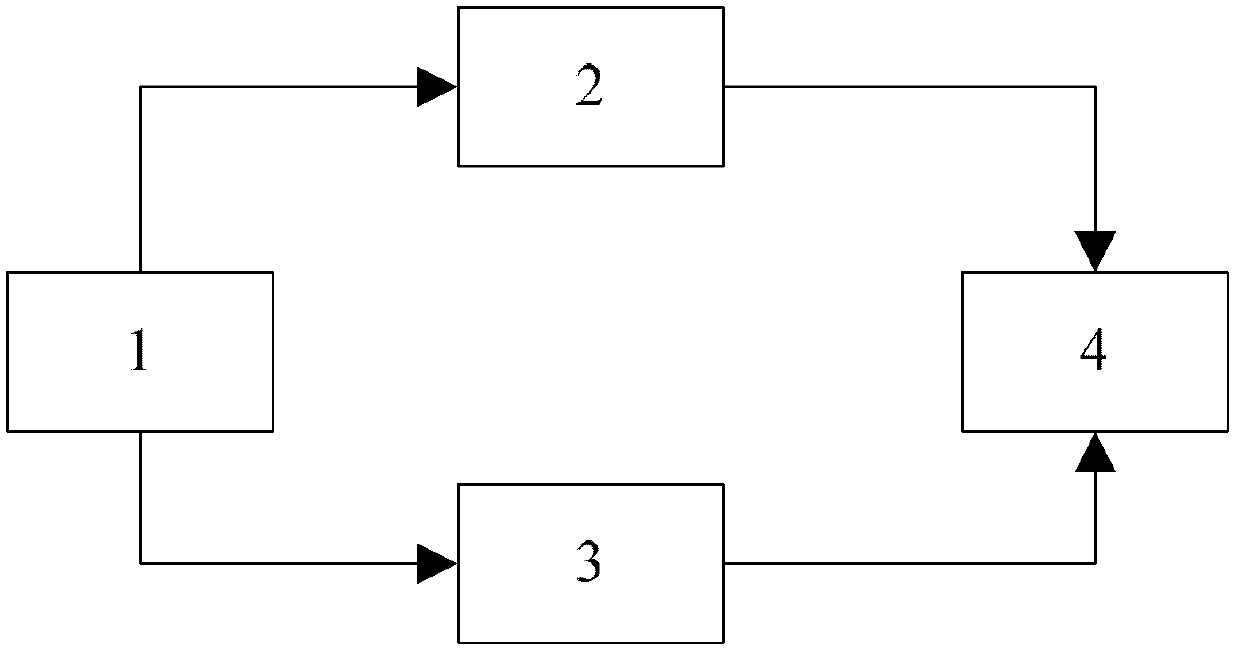

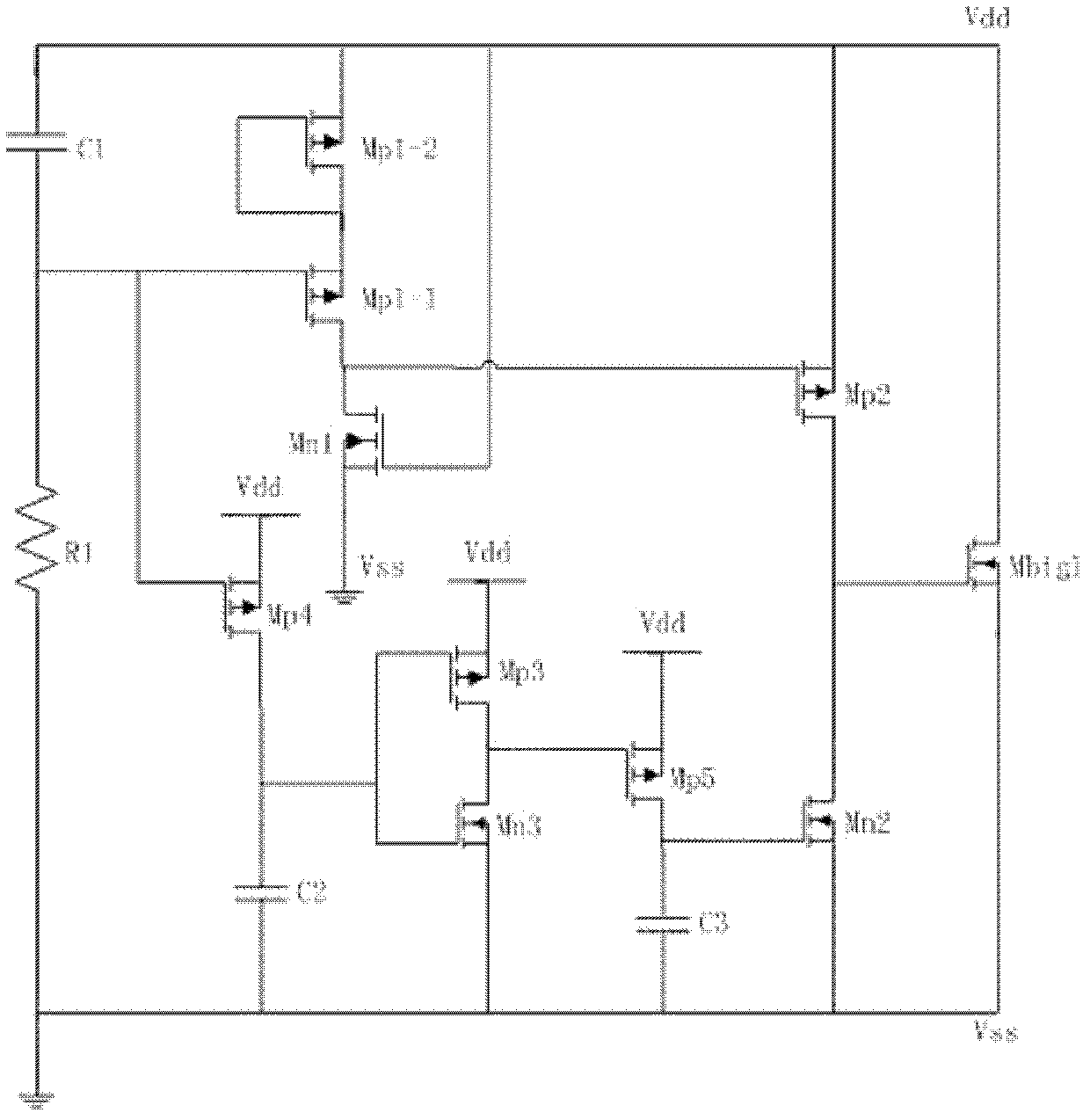

[0028] The core idea of the present invention is: separate the circuit structure for controlling the opening and closing of the clamping transistor, so that the R and C sizes of the detection circuit part can be set from a small time constant to prevent false triggering, and a large time constant to prevent false triggering. Get out of the paradoxical choice of getting enough clamp transistor turn-on time. In the circuit proposed by the present invention, the C-R structure of the detection circuit basically only plays a decisive role in the opening of the clamping transistor, and the closing of the clamping transistor is controlled by the time delay of the C-R time constant plus the two-stage R-C, like this The control effect of the C-R time constant of the detection circuit on the turn-off of the clamp transistor can be weakened by enlarging the time delay of R-C in the clamp transistor turn-off circuit, thereby making a small space for the C-R time constant.

[0029] fig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More