Site yield statistical method for multi-site parallel test

A statistical method and yield rate technology, applied to electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of reducing test efficiency, affecting test output, prolonging downtime, etc., to save standby time and improve test production efficiency , the effect of reducing the floor area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The method of the present invention is described in detail below by example:

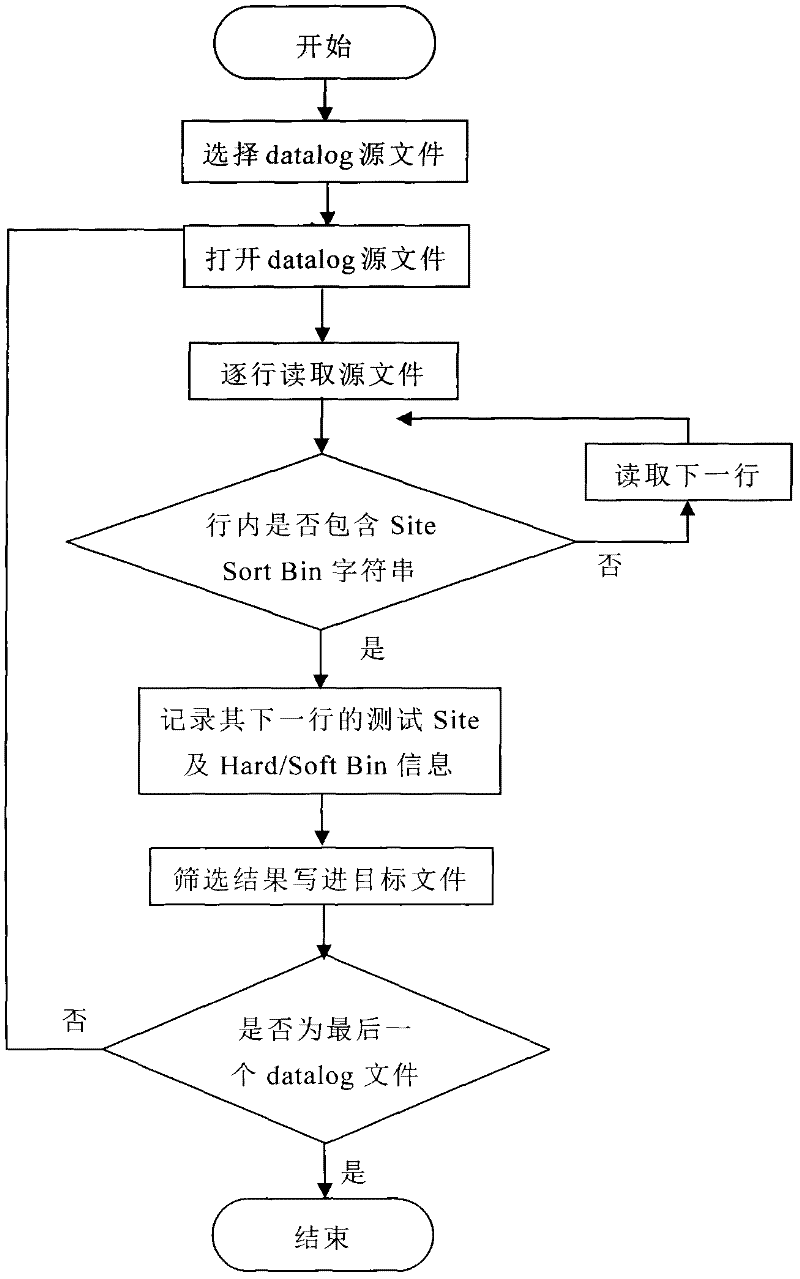

[0026] Take out the number of Bin values in each site from the test data, especially the proportion of Bin 1, such as figure 1 shown.

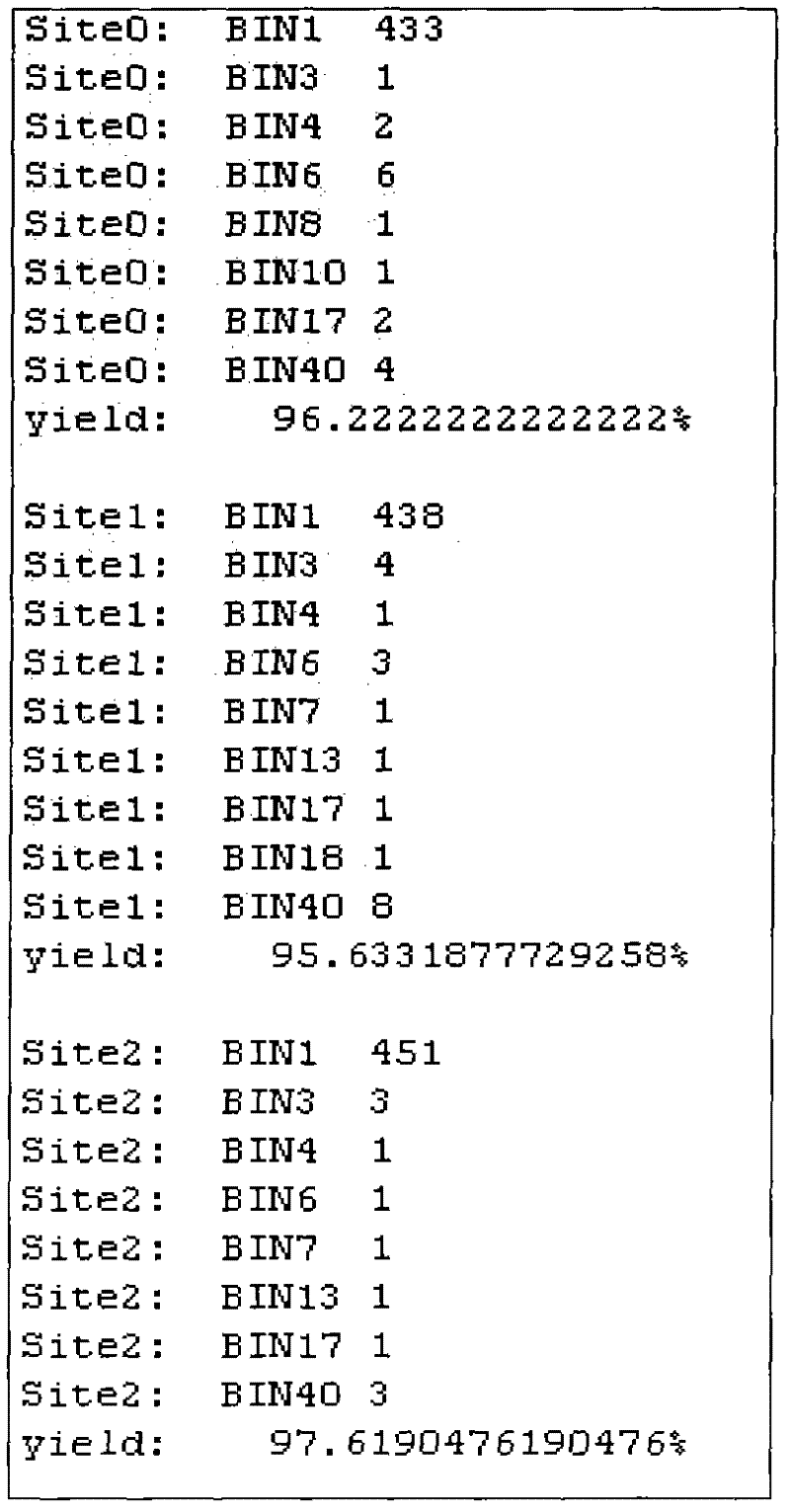

[0027] After the statistical software designed in this step runs, the information contained in the generated file includes Site, bin value and its quantity, and the proportion of bin1 in the site test; figure 2 shown.

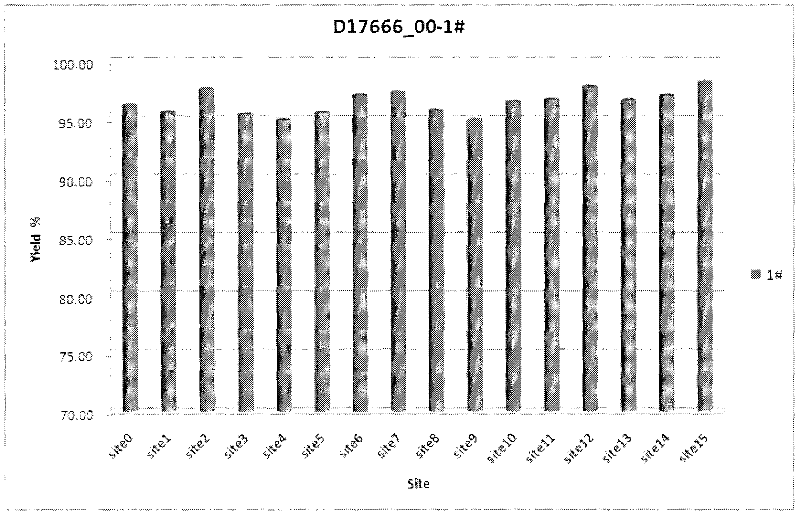

[0028] Draw a histogram according to the proportion of Bin 1 in each site test result, so that you can intuitively compare all sites horizontally. image 3 It is the yield histogram obtained from the statistics of 16site parallel test results. The horizontal axis is the site, and the vertical axis is the yield of each site.

[0029] There is a certain gap between the yield rates of each site. The reasons for these gaps are not only factors such as the random distribution of the chip itself, but also the test hardware that more or less a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More