Method for reducing line edge roughness (LER) and device for implementing method

A semiconductor and feature structure technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as the control of device leakage current and short-channel effect, and affect device performance, so as to avoid device performance degradation and avoid threshold voltage. changes, the effect of increasing the signal-to-noise ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

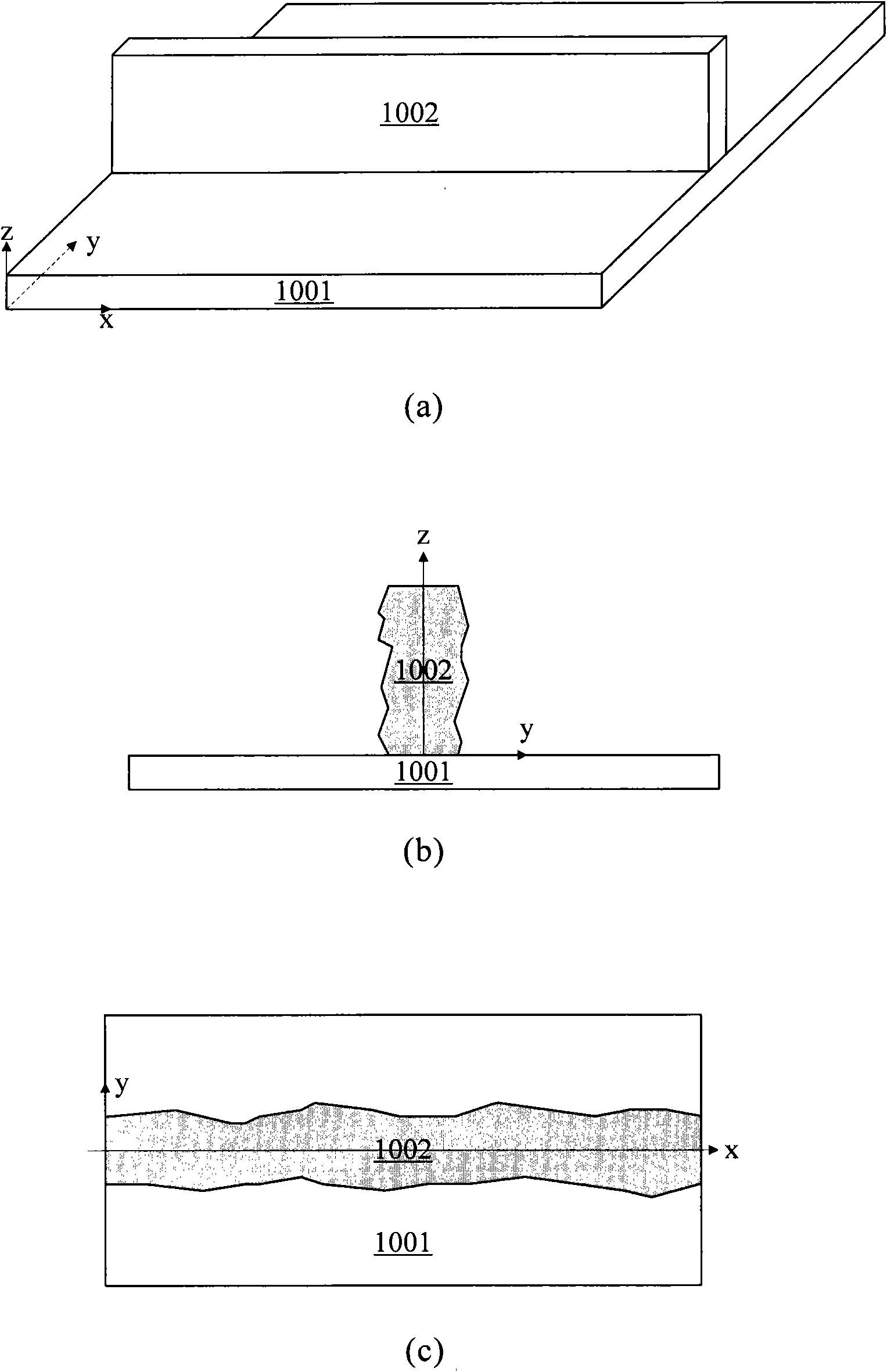

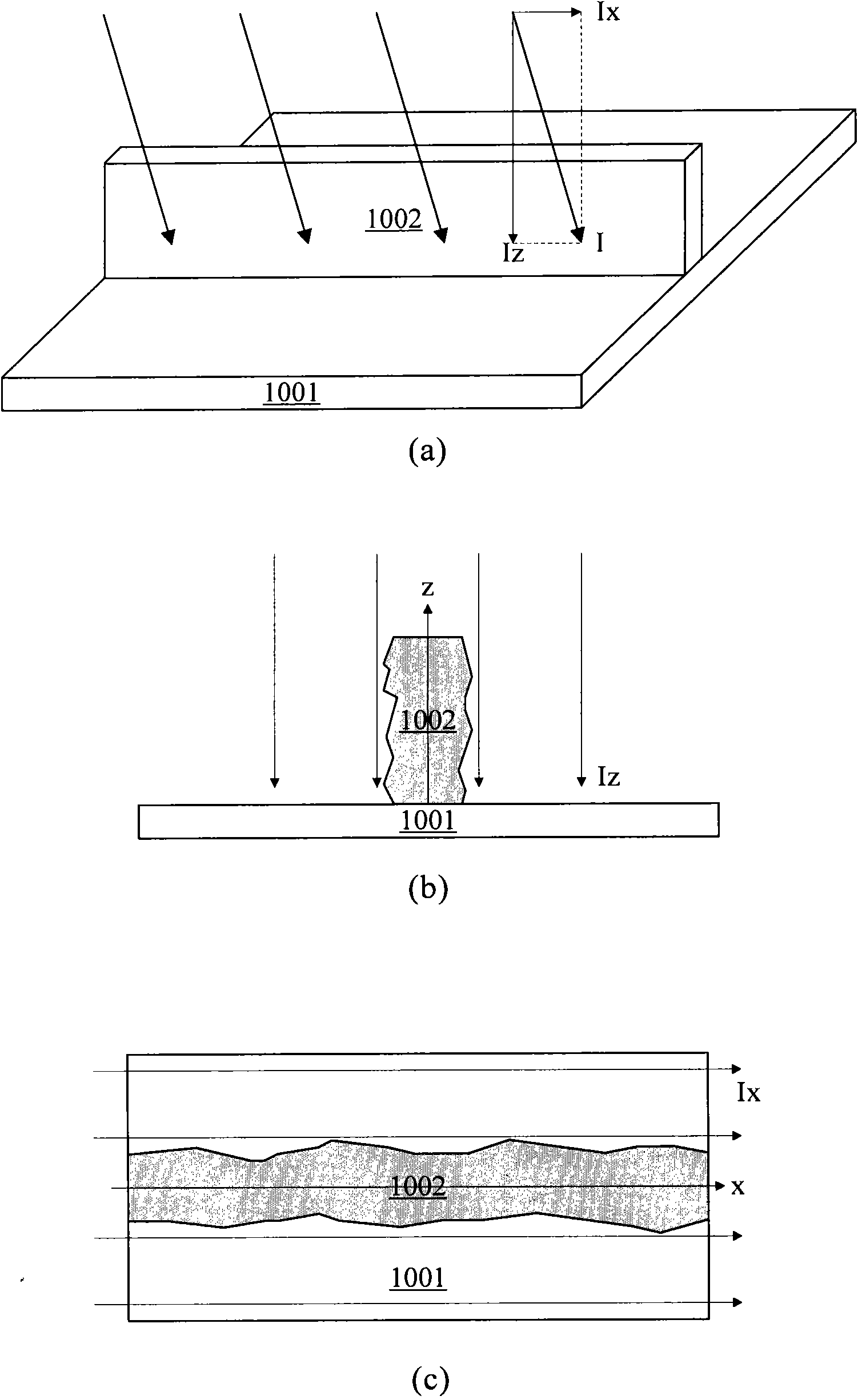

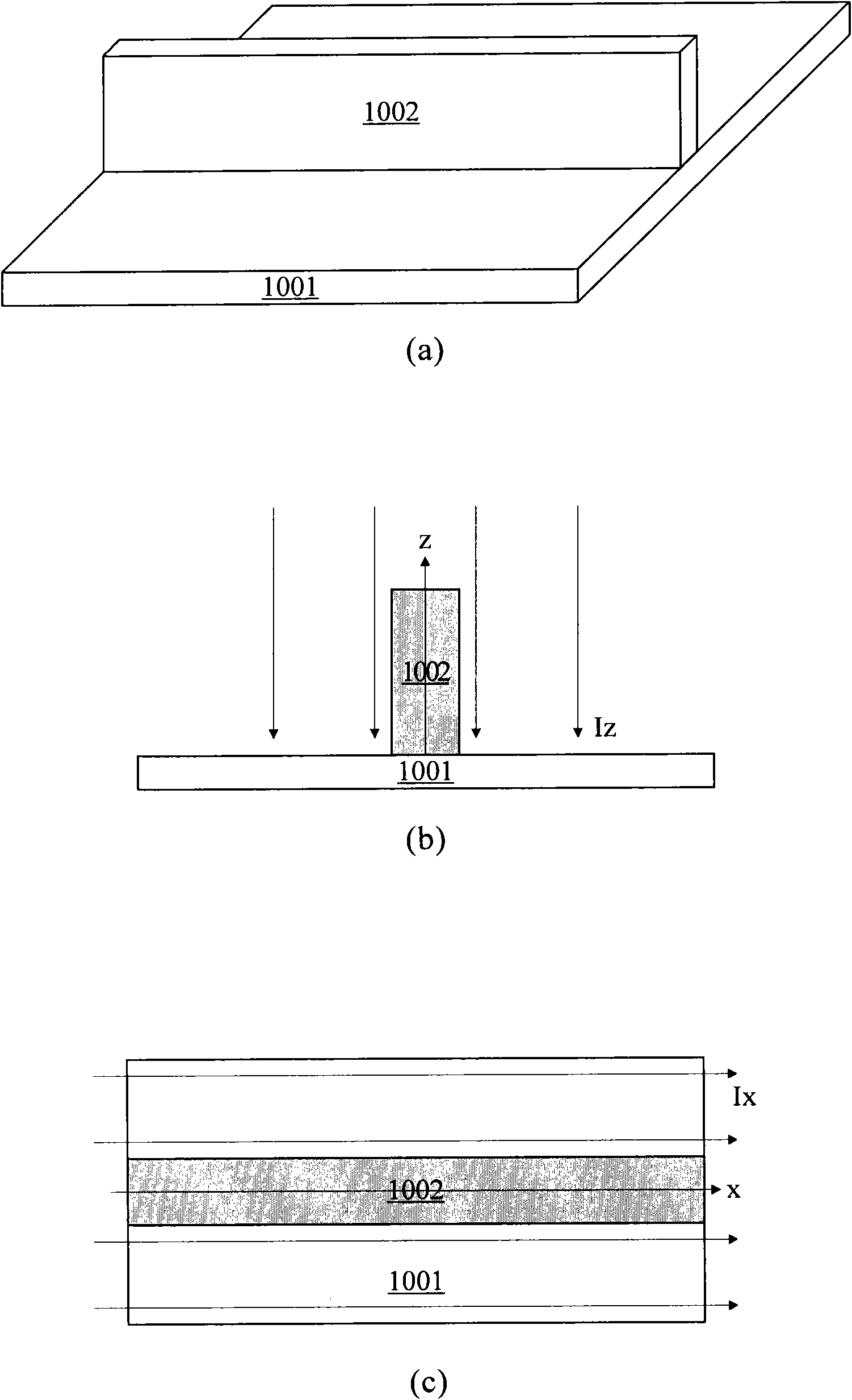

[0021] Hereinafter, the present invention is described by means of specific embodiments shown in the drawings. It should be understood, however, that these descriptions are exemplary only and are not intended to limit the scope of the present invention. Also, in the following description, descriptions of well-known structures and techniques are omitted to avoid unnecessarily obscuring the concept of the present invention.

[0022] A schematic diagram of a layer structure according to an embodiment of the invention is shown in the drawing. The figures are not drawn to scale, with certain details exaggerated and possibly omitted for clarity. The shapes of the various regions and layers shown in the figure, as well as their relative sizes and positional relationships are only exemplary, and may deviate due to manufacturing tolerances or technical limitations in practice, and those skilled in the art will Regions / layers with different shapes, sizes, and relative positions can be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More