A method for quickly judging the test results of a SOC chip

A chip testing and chip technology, which is applied in the field of rapid judgment of SOC chip test results, can solve the problems of high cost, loss of position coordinates, and judging chips, etc., and achieves the convenience of reading test information, the safety of reading test information, and the reduction of test costs. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] In order to have a more specific understanding of the technical content, characteristics and effects of the present invention, now in conjunction with the illustrated embodiment, the details are as follows:

[0022] DFT (Design for Testability, Design for Testability) refers to solving the problem of fast, effective and automatic testing of chips by adding logic, replacing components and adding pins during the design process of integrated circuits.

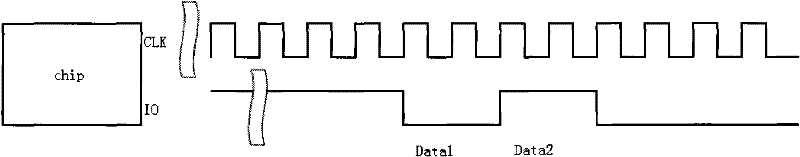

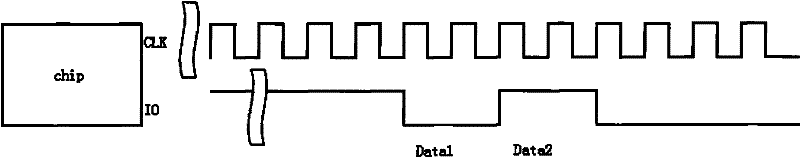

[0023] The method for quickly judging the test result of the SOC chip of the present invention is realized by adding a DFT circuit on the chip during the original design of the SOC chip. Its basic design idea is: after testing the chip, use the memory unit of the chip to store test information such as the test result and status of the chip. After the chip is packaged, when the test information of the chip needs to be read out, a specific The test vector, the I / O port of the chip outputs a specified number of pulses with a s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More