Integrated Circuit Test Methods

A technology of integrated circuits and test systems, which is applied in the field of testing storage components and can solve problems such as time-consuming

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the above-mentioned content and other aspects of this disclosure more obvious and understandable, the preferred embodiments are specifically cited below, together with the accompanying drawings, and are described in detail as follows:

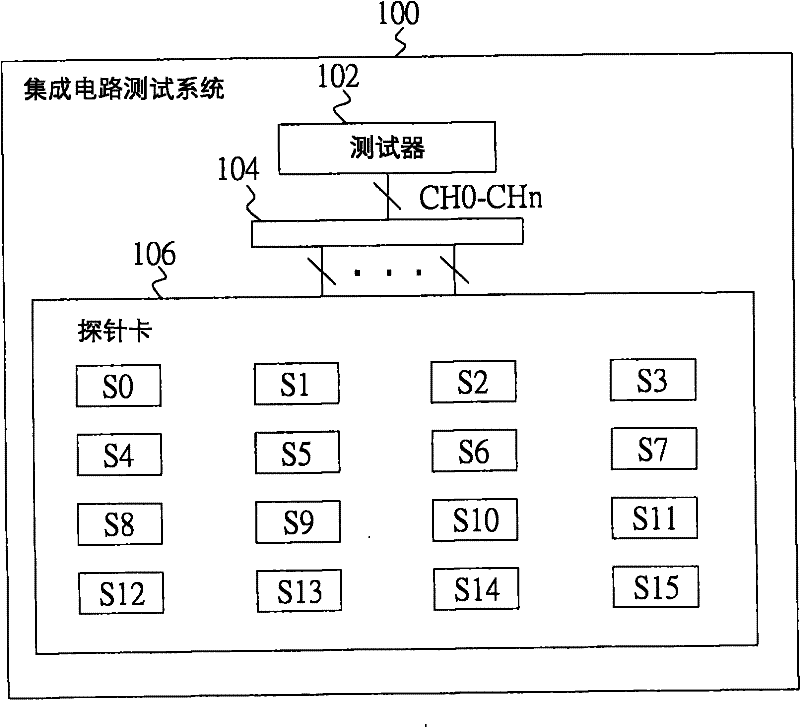

[0034] figure 1 Shown is a partial block diagram of an integrated circuit testing system 100 . Integrated circuit test system 100 includes a commercial test system, such as Kalos 1 . Integrated circuit test system 100 may allow parallel testing of a limited number of test elements. The integrated circuit testing system 100 includes a tester 102 , a multiplexer 104 , and a probe card 106 . In some embodiments, one or both of the tester 102 and the multiplexer 104 may be physically integrated into the probe card 106 . The probe card 106 includes a plurality of test points S0-S15, and each test point S0-S15 can independently test a respective integrated circuit (test element). In particular, if figure 1 In the illustra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com