FPGA (Field Programmable Gate Array)-based single event effect test method for NAND FLASH device

A single event effect and testing method technology, applied in the direction of instruments, static memory, etc., can solve the problems of large capacity of NANDFLASH memory, difficult testing, long reading/writing/erasing time, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

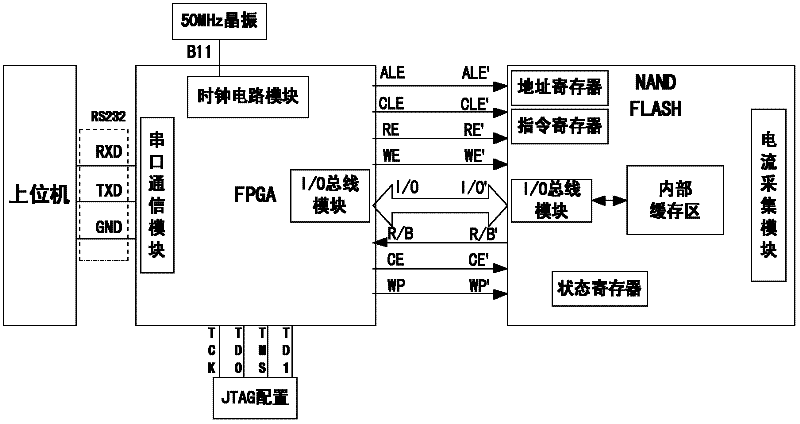

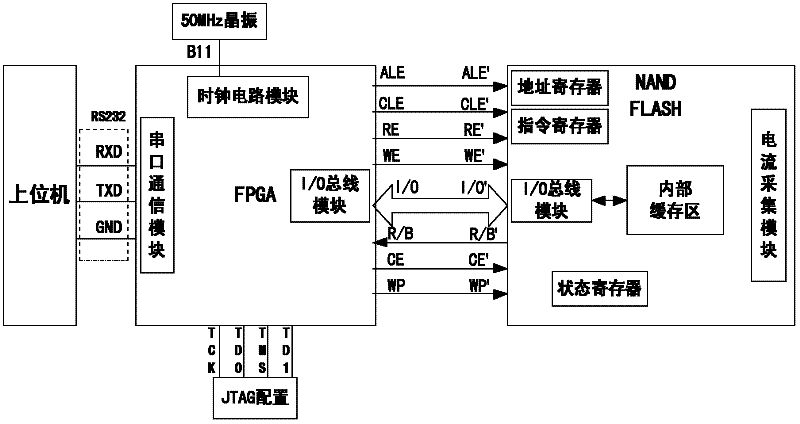

[0124] Such as figure 1 Shown, a kind of FPGA-based NAND FLASH device single event effect test method of the present invention, described method mainly comprises: host computer, 50MHz crystal oscillator, program configuration port JTAG, FPGA control module and NAND FLASH test module; FPGA control module mainly Including serial communication module, clock circuit module and I / O bus module; NAND FLASH test module mainly includes address register, instruction register, internal buffer area, storage unit, status register, I / O bus module and current acquisition module.

[0125] Among them, the upper computer is connected to the FPGA through the data receiving end RXD, the data sending end TXD and the ground wire GND pin of the serial communication RS232 interface; the 50MHz crystal oscillator is connected to the clock signal input end B11 pin of the FPGA to provide an external clock signal for the FPGA; Program configuration port JTAG is connected to FPGA through test clock input s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More