Method for forming flat dielectric layer

A dielectric layer and flat technology, which is applied in the field of forming a flat dielectric layer, can solve the problem of low yield and achieve the effects of increased yield, reduced thickness difference, and reduced thickness difference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

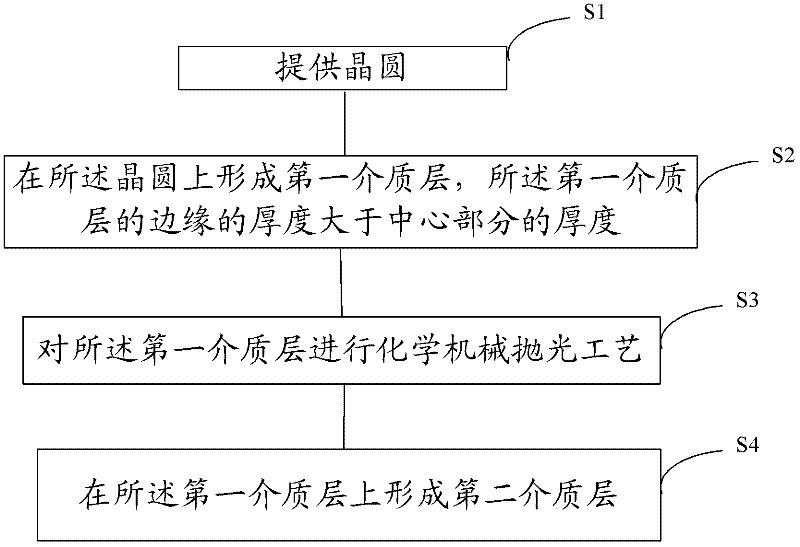

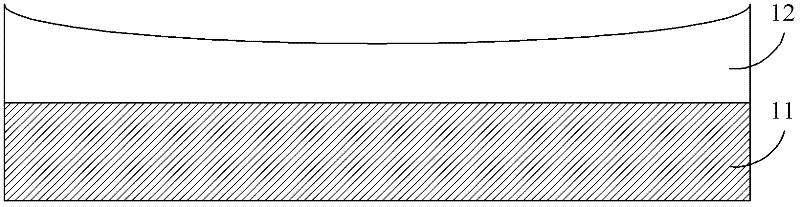

[0034] It can be seen from the background art that the existing method for forming a dielectric layer is to first deposit a dielectric layer by a process such as chemical vapor deposition, and then planarize the surface of the dielectric layer by a chemical mechanical polishing (CMP) process.

[0035] The inventors have found that the yield of final devices formed at the edge of the wafer is generally lower than the yield of final devices formed at the central portion of the wafer. After further research, the inventor found that after polishing the dielectric layer using the prior art, the thickness of the dielectric layer is not uniform, and the thickness of the dielectric layer at the edge of the wafer is smaller than that of the dielectric layer at the center of the wafer. The thickness of the dielectric layer is small. For example, after chemical mechanical polishing of an 8-inch wafer, due to the different pressures exerted by the grinding head on each part of the wafer, ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More