Flow method for automatically verifying correctness of electric rule file

An automatic verification and correctness technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as heavy workload, waste of resources, and long development time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

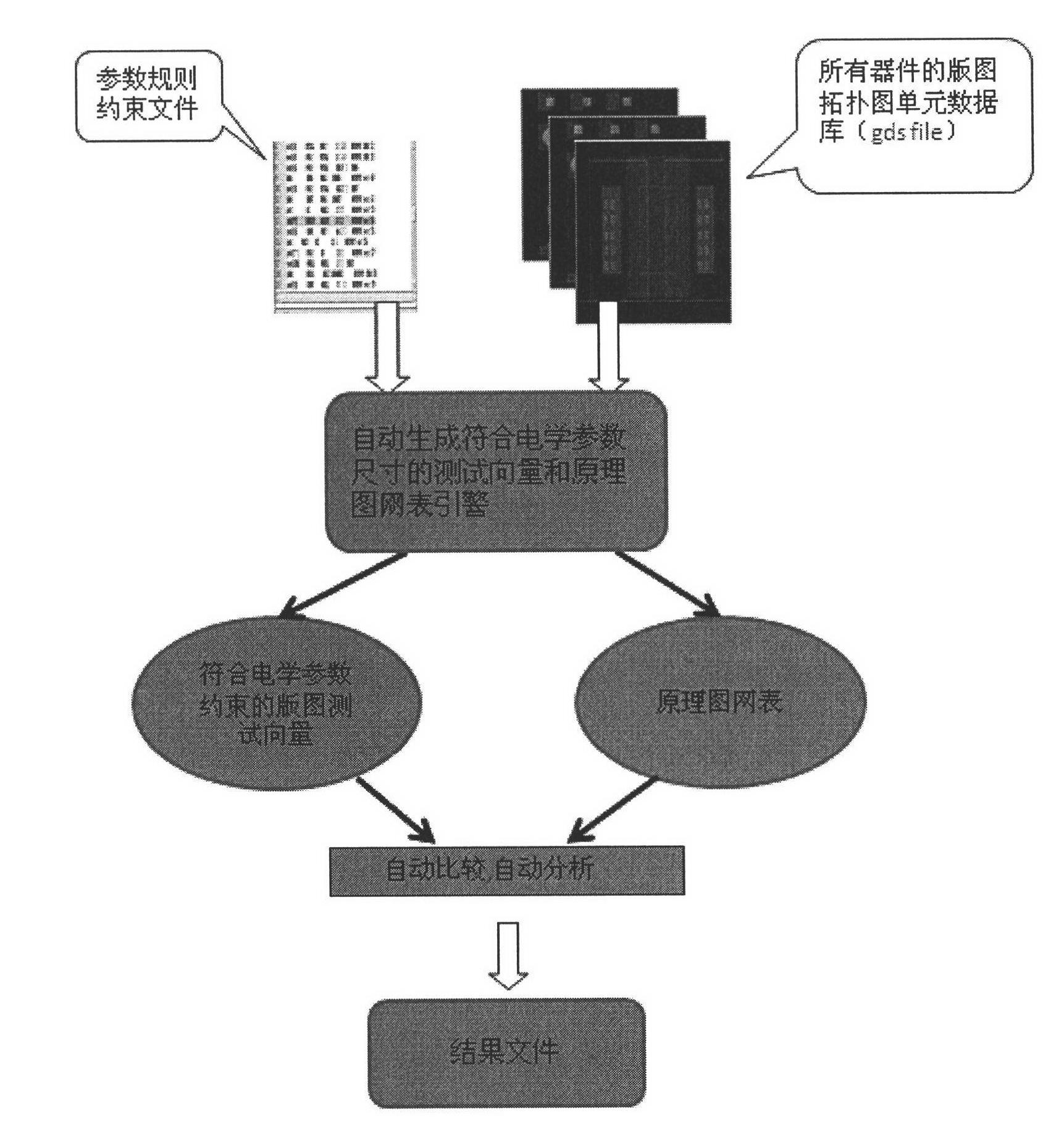

[0068] Step 1: Draw the layout according to the schematic diagram of the complex device model to generate a standard device layout. Export all standard layout device library cells as a data file, namely sample gds. The drawing of the standard device layout only needs to ensure the correct topological relationship of the graph, and does not need to draw the precise value of the device parameters.

[0069] Step 2: Write the parameter rule constraint file to define the specific parameter constraint principle of each device.

[0070] Step 3: call the computer software program proposed by the present invention to automatically generate layout test vectors and schematic netlists, automatically verify and generate corresponding analysis and comparison results. According to the analysis and comparison results, corresponding adjustments and corrections are made to the electrical process rule files.

[0071] For multiple devices under a typical bd1u process, we use the above steps to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More