Semiconductor process processing system and method

A technology for processing systems, semiconductors, applied in the field of defective systems, capable of solving problems such as breakage, wafer breakage, wafer bending, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The following describes embodiments of systems and methods for reducing the generation of defects in semiconductor wafer processing in preparation for a backgrind tape die attach process. The "an embodiment" or the specific features mentioned in the "embodiment" in the description do not mean that this embodiment is only related to the single embodiment described, but its implementation can be shown in the description. In at least one embodiment. Similar technical features generally use similar index numbers, but it does not mean that each embodiment must have the same technical features. In addition, the technical features described in the drawings are not drawn according to specific dimensions, so specific dimensions should not be used to limit the features described in this system.

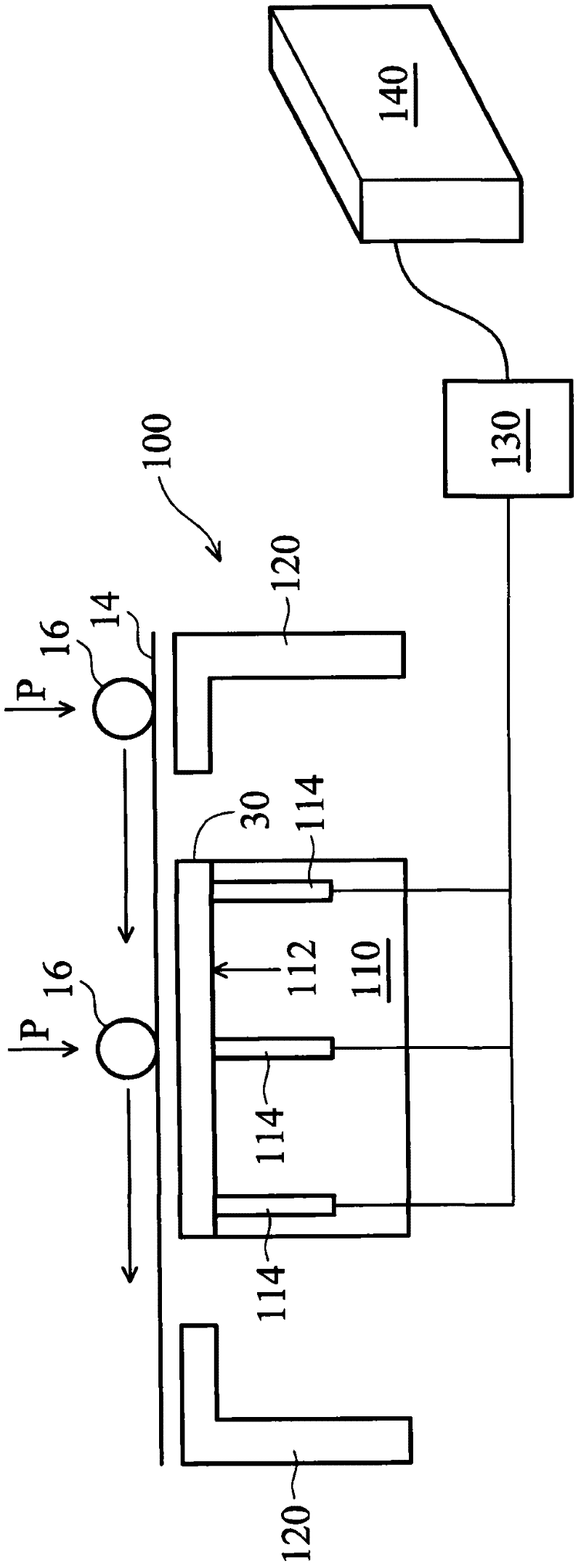

[0039] figure 1 A high level diagram is shown of a flip chip ball grid array system 100 according to an embodiment of the present invention for reducing defects in chip scale packaging...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More