Gate forming method

A gate and dummy gate technology, used in electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as substrate damage, and achieve the effect of reducing voids, avoiding the formation of voids, and avoiding damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

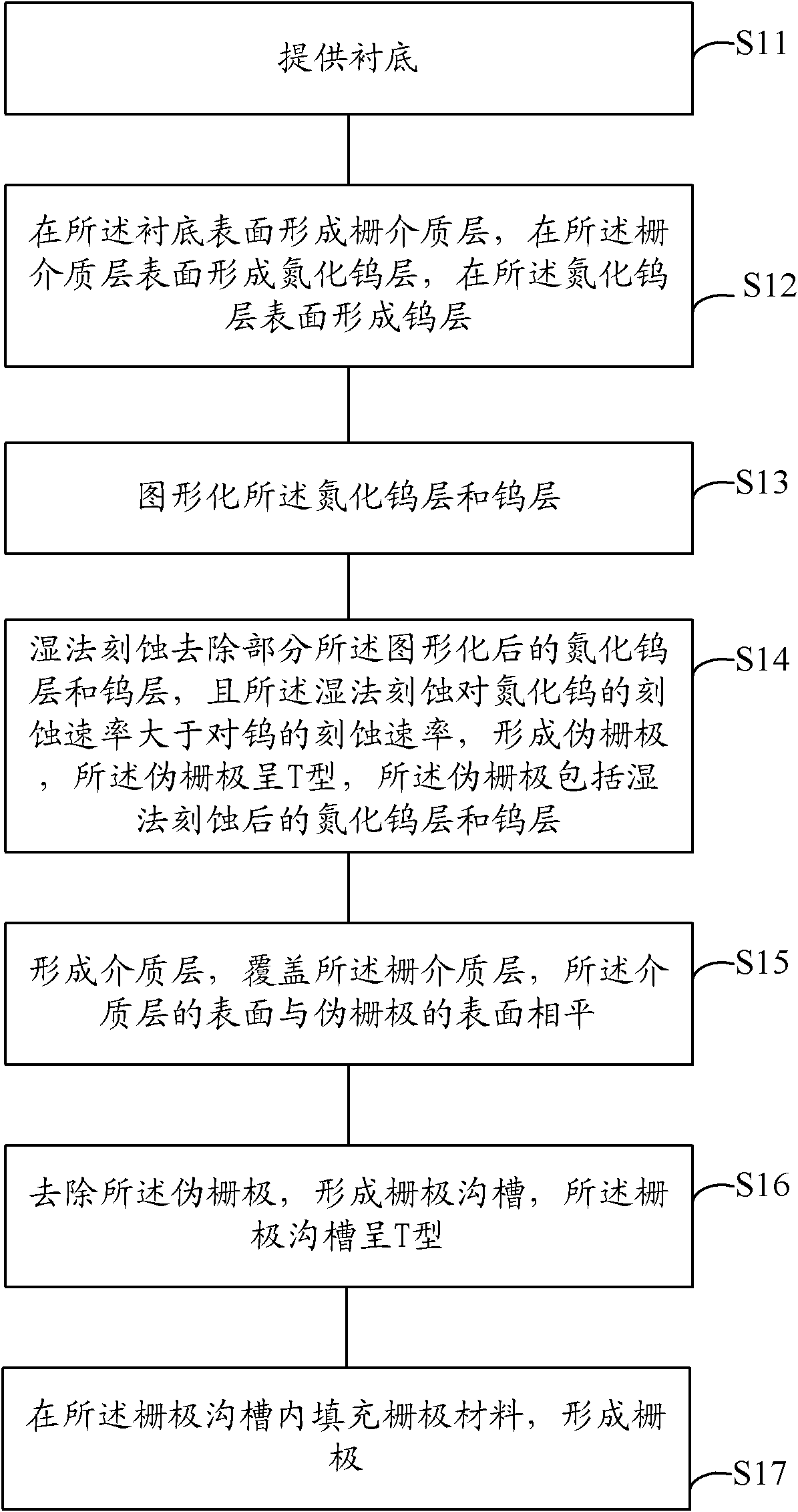

[0029] After long-term research, the inventor hopes to find a simple process to form a gate trench with a width at the top greater than that at the bottom, which is conducive to the filling of the gate material and avoids the formation of voids, or at least reduces the formation of voids; moreover, it can avoid the existing There is the disadvantage of causing damage to the substrate as described in the art. After reading a lot of materials, the inventor unexpectedly discovered that the article "resist removal and cleaning for TANOS metal Gate on volatile memories" discloses that when wet etching tungsten nitride and tungsten, the etching rate of tungsten nitride is greater than that of tungsten.

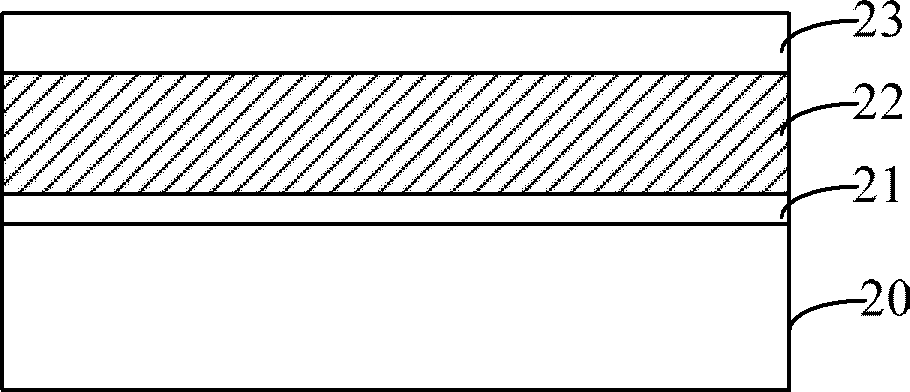

[0030] In the method for forming a grid in a specific embodiment of the present invention, when etching tungsten nitride and tungsten by a wet method, the etching rate of tungsten nitride is higher than that of tungsten, and a patterned grid is formed on the substrate. The tungsten...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More