Graphical test method of semiconductor devices

A test method and semiconductor technology, applied in the direction of instruments, measuring electricity, measuring devices, etc., can solve the problems of low maintainability, long development cycle, poor convenience, etc., to enhance maintainability, shorten development cycle, and develop convenience. improved effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Specific embodiments of the present invention will be described below in conjunction with the accompanying drawings, so that those skilled in the art can better understand the present invention. It should be noted that in the following description, when detailed descriptions of known functions and designs may dilute the main content of the present invention, these descriptions will be omitted here.

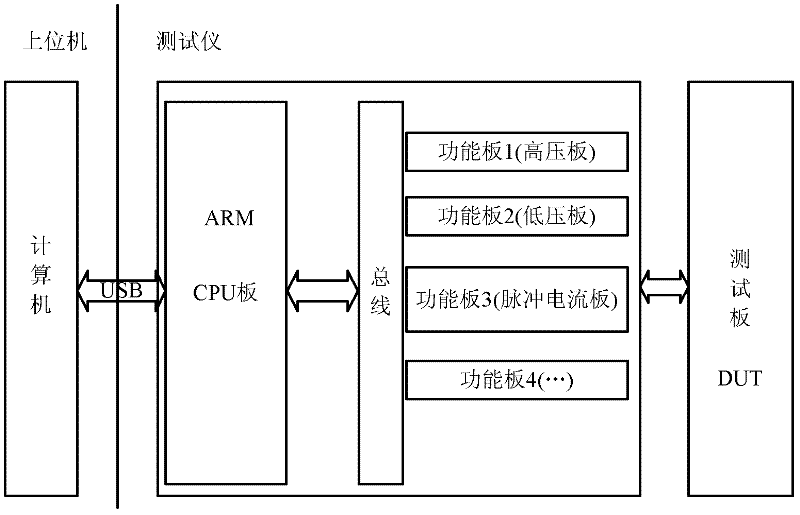

[0033] figure 1 It is a schematic block diagram of semiconductor device testing.

[0034] The semiconductor device graphical testing method of the present invention relies on a semiconductor device tester, adopts a host computer and a tester framework, makes the development environment and the operating environment independent of each other, and improves the safety and stability of the test.

[0035] Such as figure 1 As shown, the tester includes a core control board, namely the CPU board, a high-voltage board that generates high-voltage excitation, a low-voltage board th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More