Method and device for filtering high-speed sampling signal in real time based on digital signal processor (DSP)

A high-speed sampling and signal technology, applied in the direction of impedance network, adaptive network, electrical components, etc., can solve the problems of increased calculation amount, extended operation time, and increased storage space, and achieve the goal of reducing the amount of calculation and shortening the operation delay Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

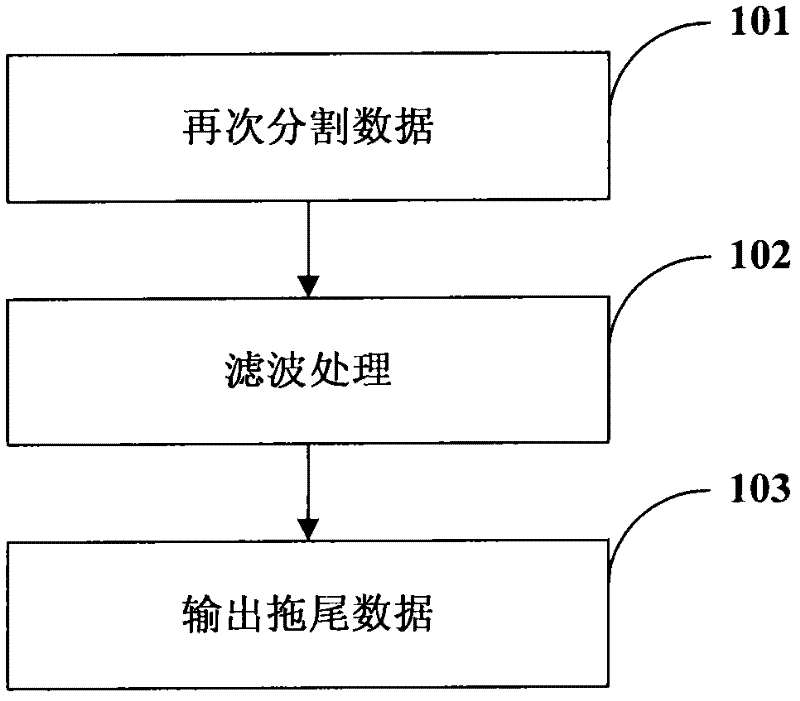

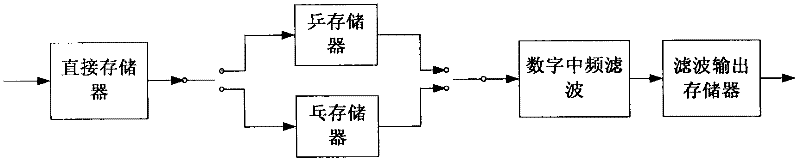

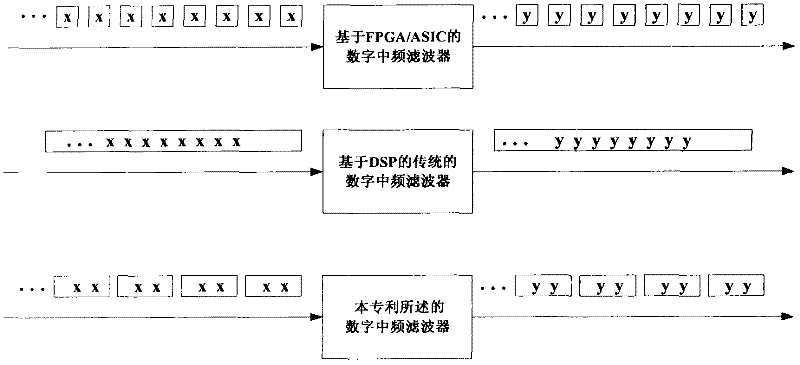

[0038] See attached figure 2 It is a schematic structural diagram of a real-time filtering device for high-speed sampling signals based on a DSP platform. Direct memory (DMA) controls the reception and ping-pong storage of the intermediate frequency signal from the ADC, and starts a digital intermediate frequency filtering process after completing a ping buffer storage, and then transfers to the pang buffer to continue data storage, and then restarts after completion A digital intermediate frequency filtering process. After the ping buffer stores the data, start the pang buffer to store the data, and at the same time start the data intermediate frequency filtering process. Data IF filtering is performed intermittently. The filter processing time of the data is shorter than the storage time of the ping buffer or pong buffer data, so that the above process can be guaranteed to proceed normally. If the filtering processing time of the data by the filter is greater than or equ...

Embodiment 2

[0046] See attached Figure 4 It is a schematic diagram of the device structure for real-time filtering of high-speed sampling signals, including:

[0047] The ping-pong buffer 401 is used to store the data of a frame of high-speed sampling signal after the first division;

[0048] Segmentation module 402, is used for carrying out the first division to the data of one frame high-speed adopting signal, divides the data in the ping-pong buffer again to obtain the data element

[0049] The filtering module 403 is used to filter the data micro-elements output by the segmentation module, and use the final state after filtering processing of each data micro-element as the initial state during the next data micro-element filtering processing, and continuously output the filtered data micro-elements For each data element: further use the final state of the data element after the convolution operation of the buffer after the filtering process as the initial state of the data element o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More