Layout and schematic diagram consistency comparison method for multi-voltage chip design

A chip design, multi-voltage technology, applied in the direction of electrical digital data processing, calculation, special data processing applications, etc., can solve the problems that LVS cannot reflect the real situation, LVS cannot reflect the situation, and the efficiency of LVS is low, so as to save physical verification The effect of shortening time, shortening time, improving efficiency and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

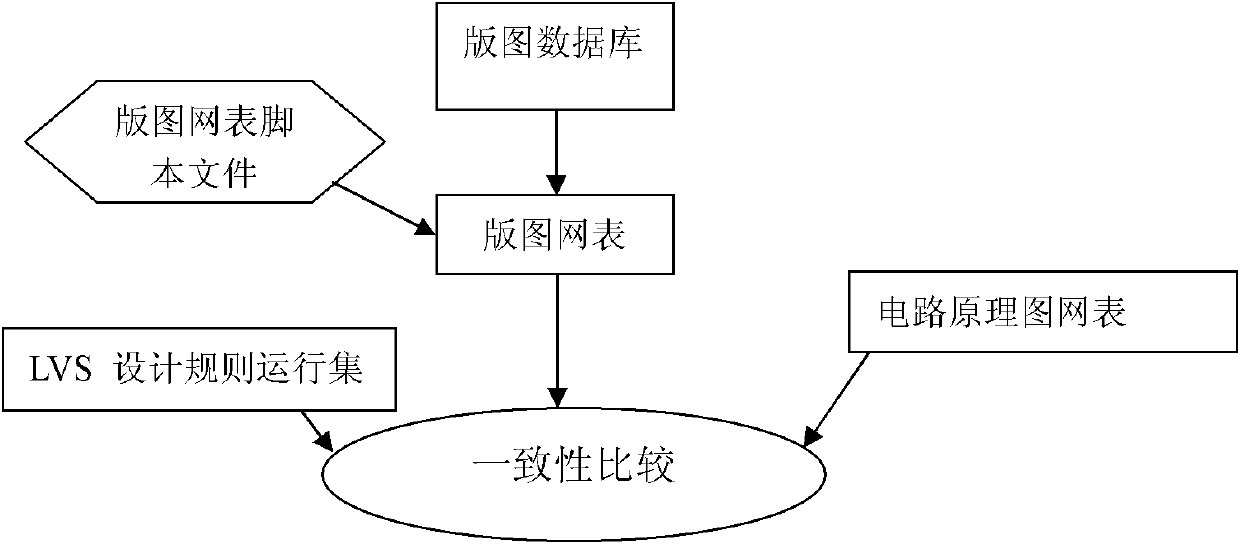

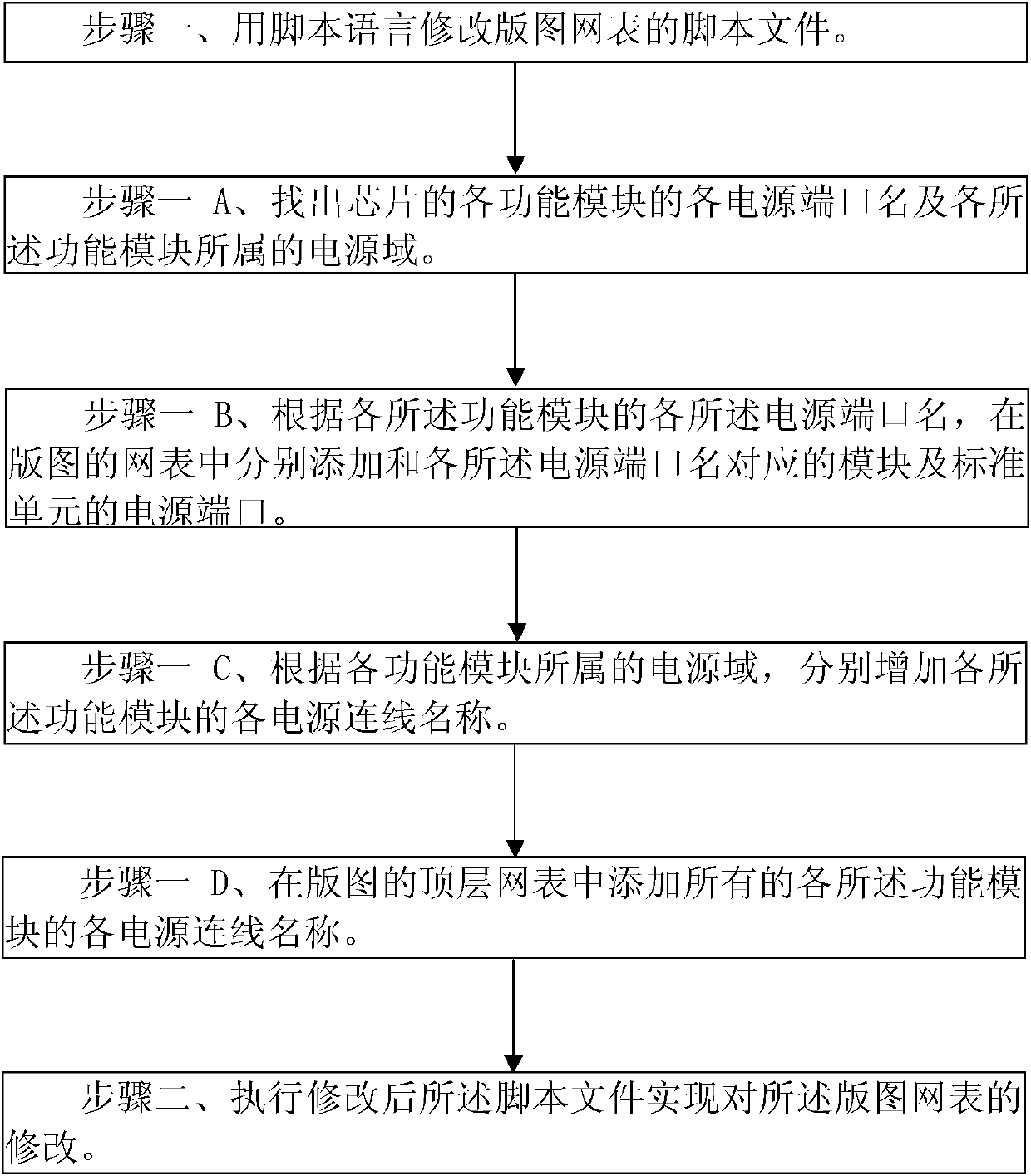

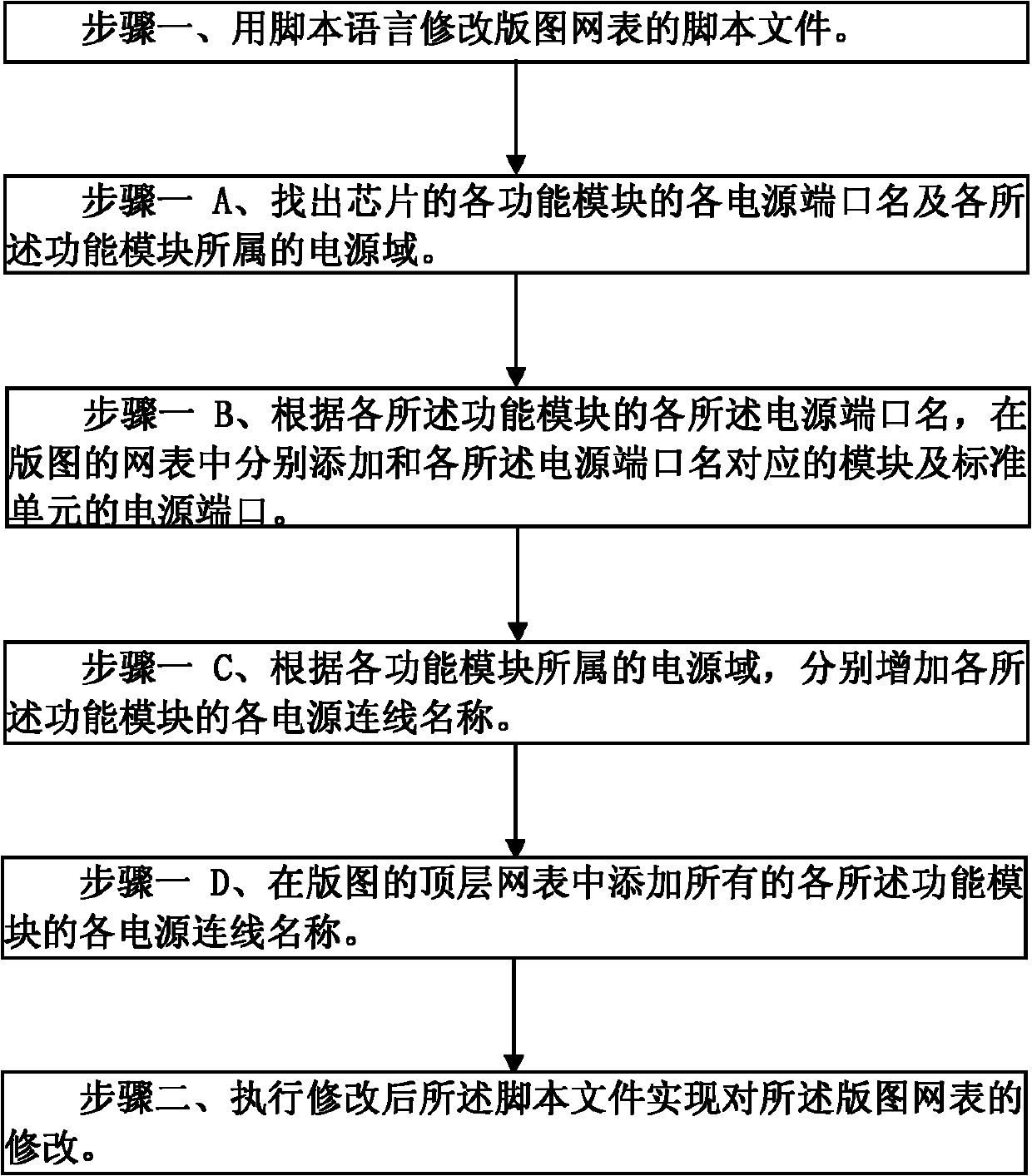

[0022] Such as figure 2 Shown is the flowchart of the method of the present invention, the layout and principle of the multi-voltage chip design of the embodiment of the present invention Figure 1 The consistency comparison method includes the following steps:

[0023] Step 1: Use PERL language to modify the script file MPower.pl of the layout netlist. The following steps are included when modifying the MPOwer.pl:

[0024] Step 1A. Find out the name of each power port of each functional module of the chip and the power domain to which each power port belongs. Each of the functional modules includes two types of power normally-on modules and power-off modules.

[0025] Step 1B. According to the names of the power ports of the functional modules, add the modules corresponding to the names of the power ports and the power ports of the standard cells in the layout netlist.

[0026] Step 1C. According to the power domain to which each functional module belongs, add the name of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More