Digital burr filtering circuit for clock pins of smart card

A smart card and circuit technology, applied in the direction of electrical components, pulse processing, pulse technology, etc., can solve the problem of anti-interference of smart card clock pins

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] specific implementation plan

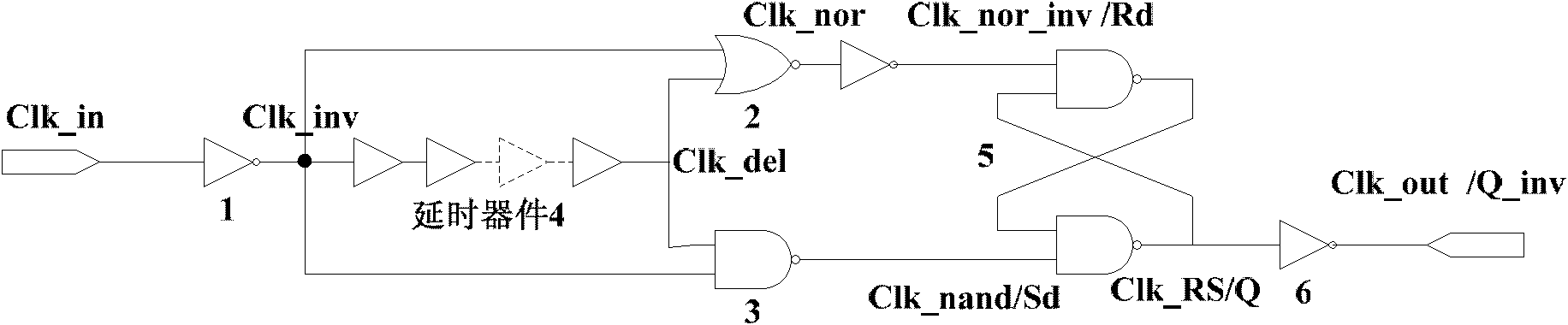

[0013] The content proposed by the present invention will be described in detail below in conjunction with the accompanying drawings. figure 1 For the circuit diagram of the present invention:

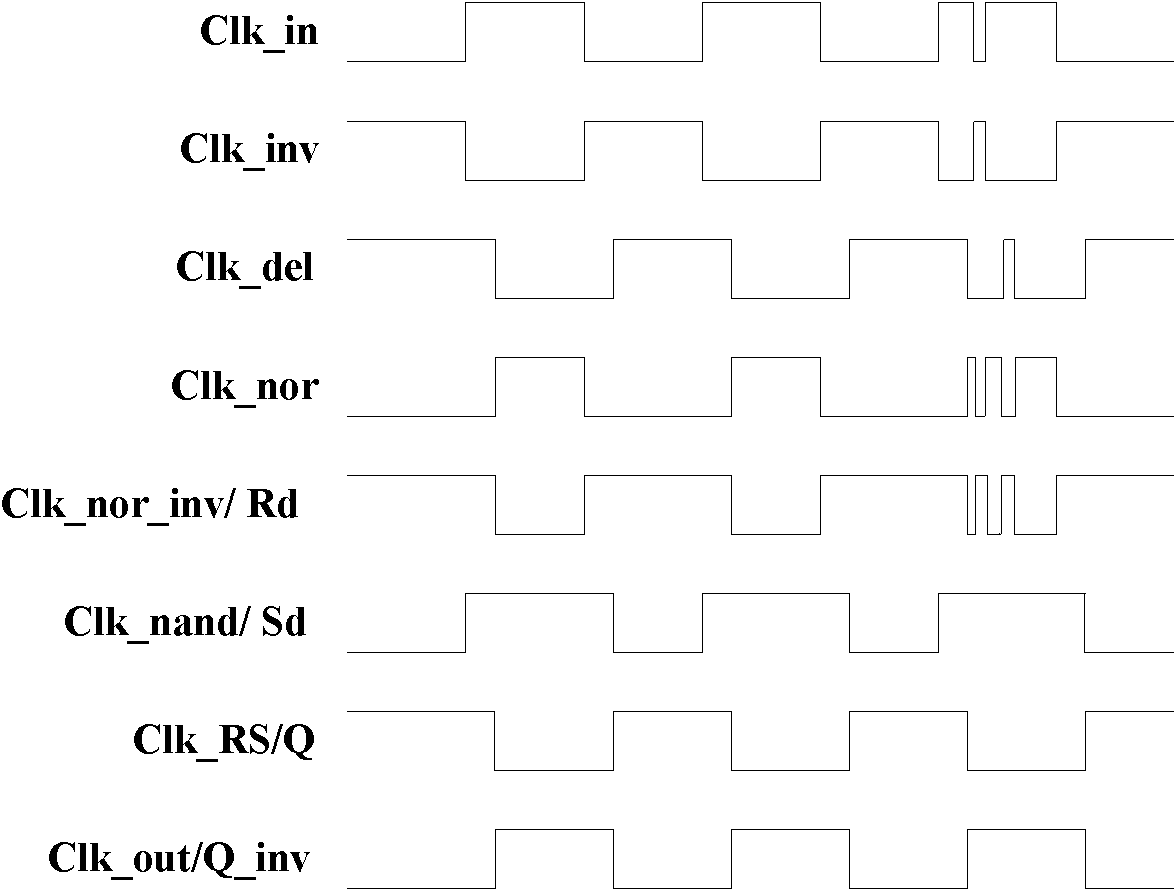

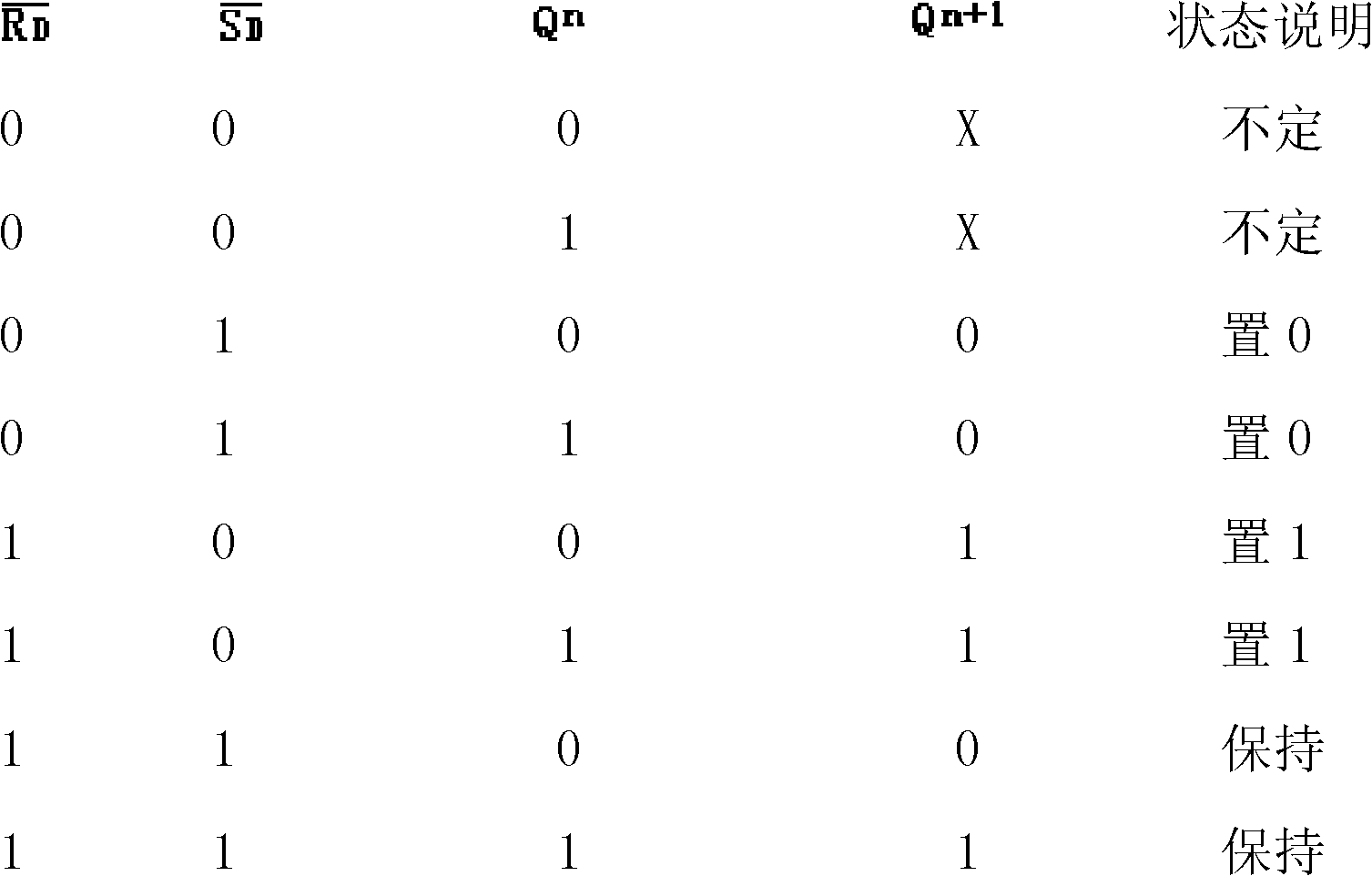

[0014] The input clock of the clock pin of the smart card chip circuit is Clk_in, which is Clk_inv after passing through the primary inverter 1 . According to the test data of the smart card product test, determine the nanosecond range of the interference glitch on the clock pin. For the specific implementation process of the product, check the standard cell library documentation provided by the relevant foundry. Find the delay device that provides the delay function, analyze between the area and the delay capability, select the delay device 4 of the corresponding type and the corresponding driving capability, and form a delay device chain. The delay time width generated by this delay device chain is just larger than the width of the interferenc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More