Chip register information management method

A technology for chip register and information management, applied in the fields of instruments, electrical digital data processing, special data processing applications, etc. Work efficiency, achieve multiple utilization, reduce the effect of complicated work

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

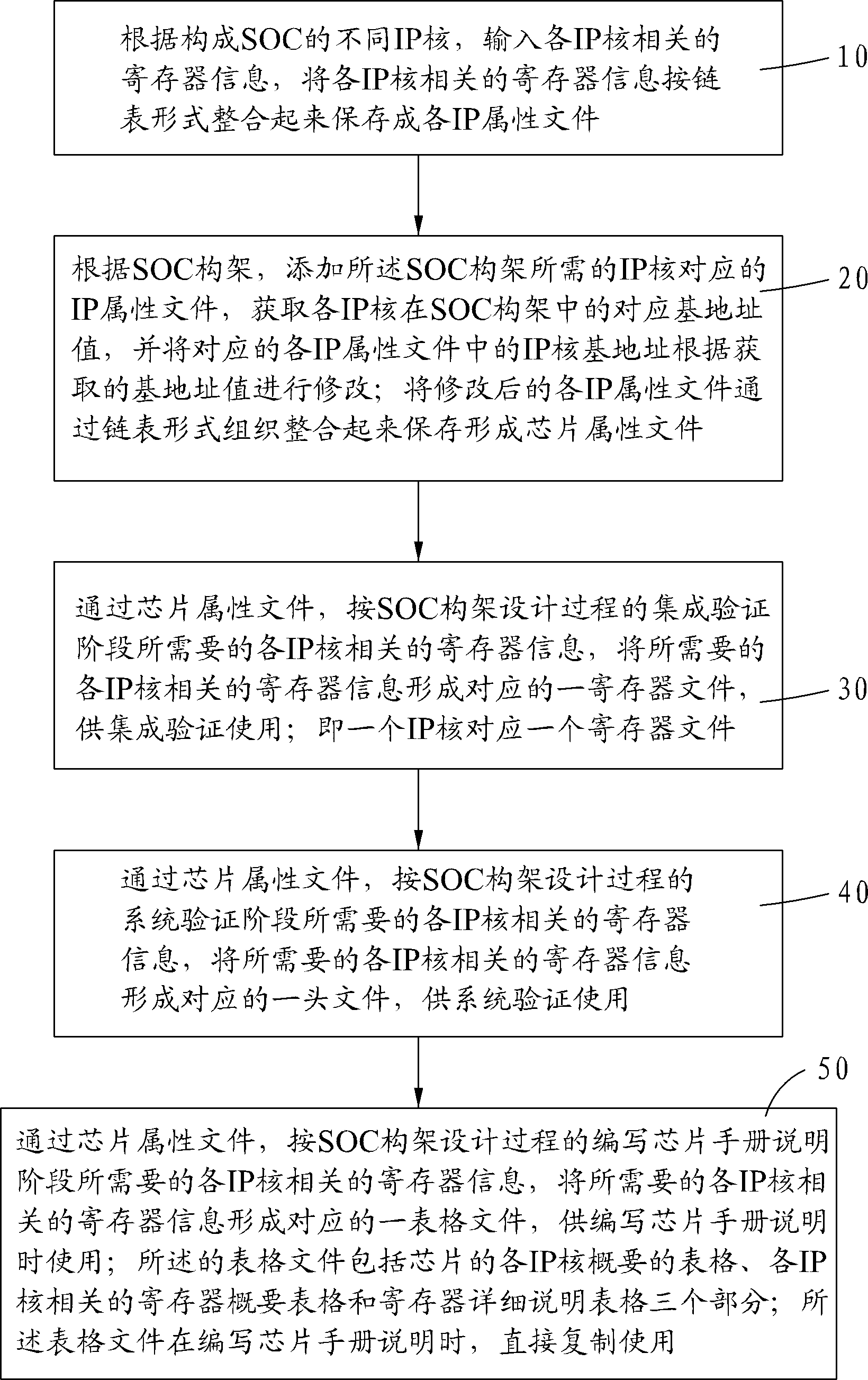

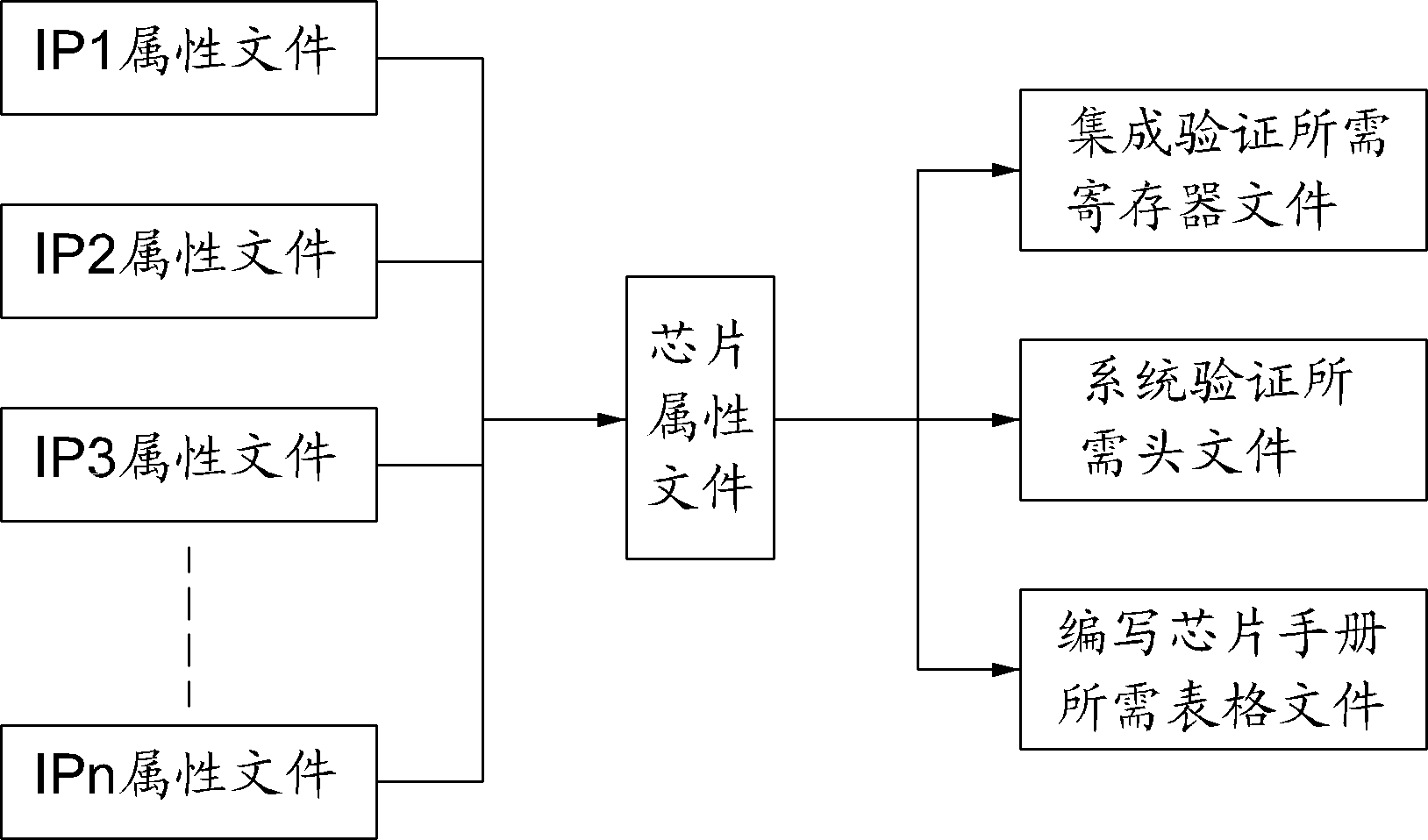

[0017] see figure 1 and figure 2 Shown, a kind of chip register information management method of the present invention comprises the following steps:

[0018] Step 10, according to the different IP cores that constitute the SOC, input the relevant register information of each IP core, and the register information includes: IP core name, IP core base address, IP core summary, IP core use description; register name, register summary, Register usage description, register space size, register offset address; register segment name, register segment start and end range, register segment read and write attributes, register segment reset value, register segment summary, and register segment usage description ;Integrate the register information related to each IP core in the form of a linked list and save it as each IP attribute file;

[0019] Step 20, according to the SOC framework, add the IP attribute file corresponding to the IP core required by the SOC framework, obtain the cor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More