Method for reducing power consumption of electric energy metering chip

A technology of electric energy metering chip and power consumption, which is applied in the direction of measuring electric variables, measuring devices, instruments, etc., to achieve the effect of reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

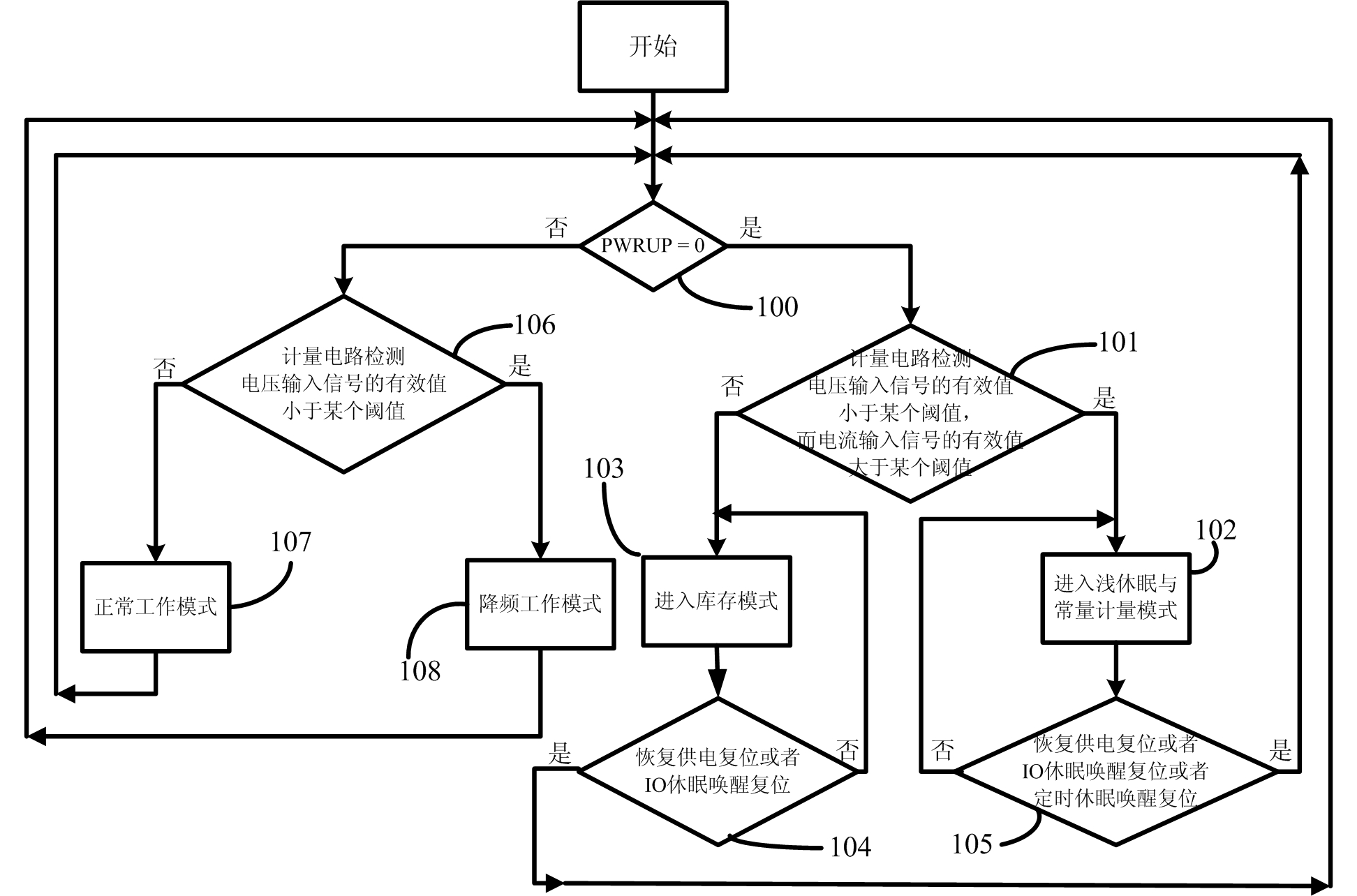

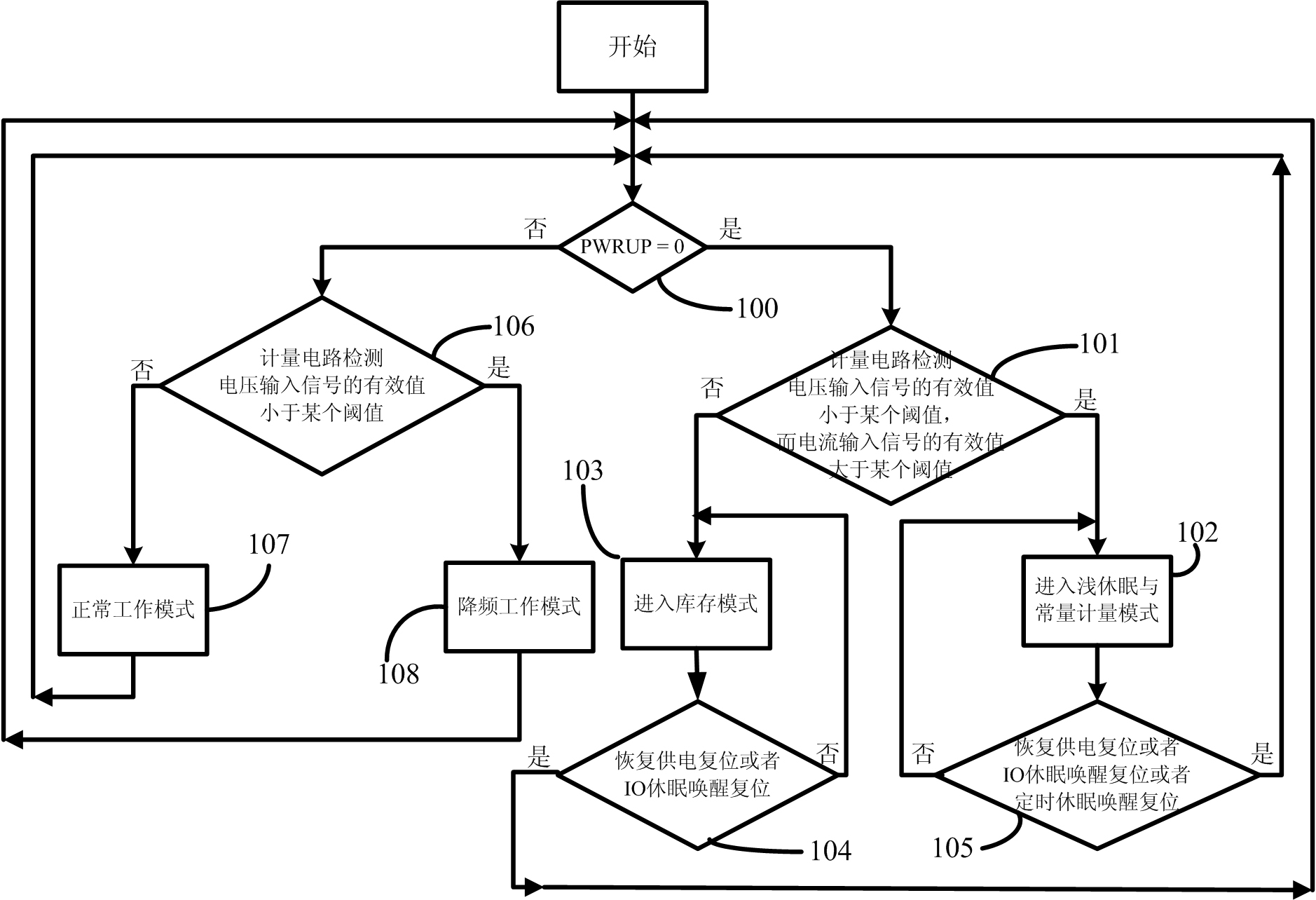

[0023] In order to achieve the purpose of reducing power consumption, the present invention sets multiple clock states for the power metering system chip, and performs clock state conversion according to the current power supply state of the system chip and the generation source of sleep wake-up reset.

[0024] In this embodiment, an input pin of the system chip is used to determine the current power supply state, and the PWRUP signal is defined as the power supply state obtained from this input pin. PWRUP=0 means that the chip is powered by a battery, and PWRUP=1 means that the chip Powered by the power line, that is, the normal power supply.

[0025] Two clock domains are set inside the system chip, the CPU is located in clock domain 1, and the metering circuit includes a power effective value calculation circuit and an energy accumulation circuit, both of which are located in clock domain 2, and the two clock domains use independent clocks. The clock of each clock domain ca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More