Patents

Literature

159 results about "Underclocking" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Underclocking, also known as downclocking, is modifying a computer or electronic circuit's timing settings to run at a lower clock rate than is specified. Underclocking is used to reduce a computer's power consumption, increase battery life, reduce heat emission, and it may also increase the system's stability and compatibility. Underclocking may be implemented by the factory, but many computers and components may be underclocked by the end user.

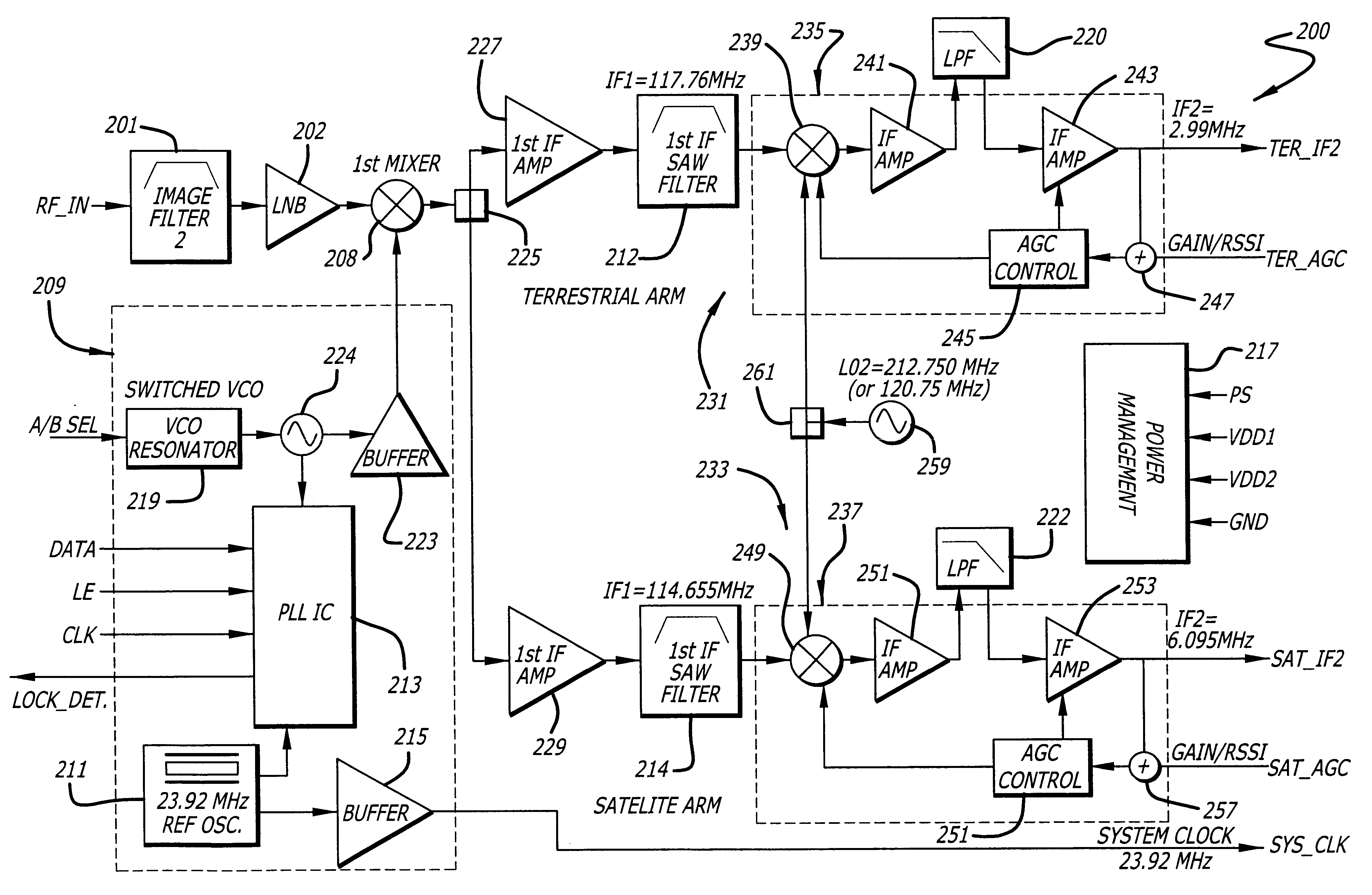

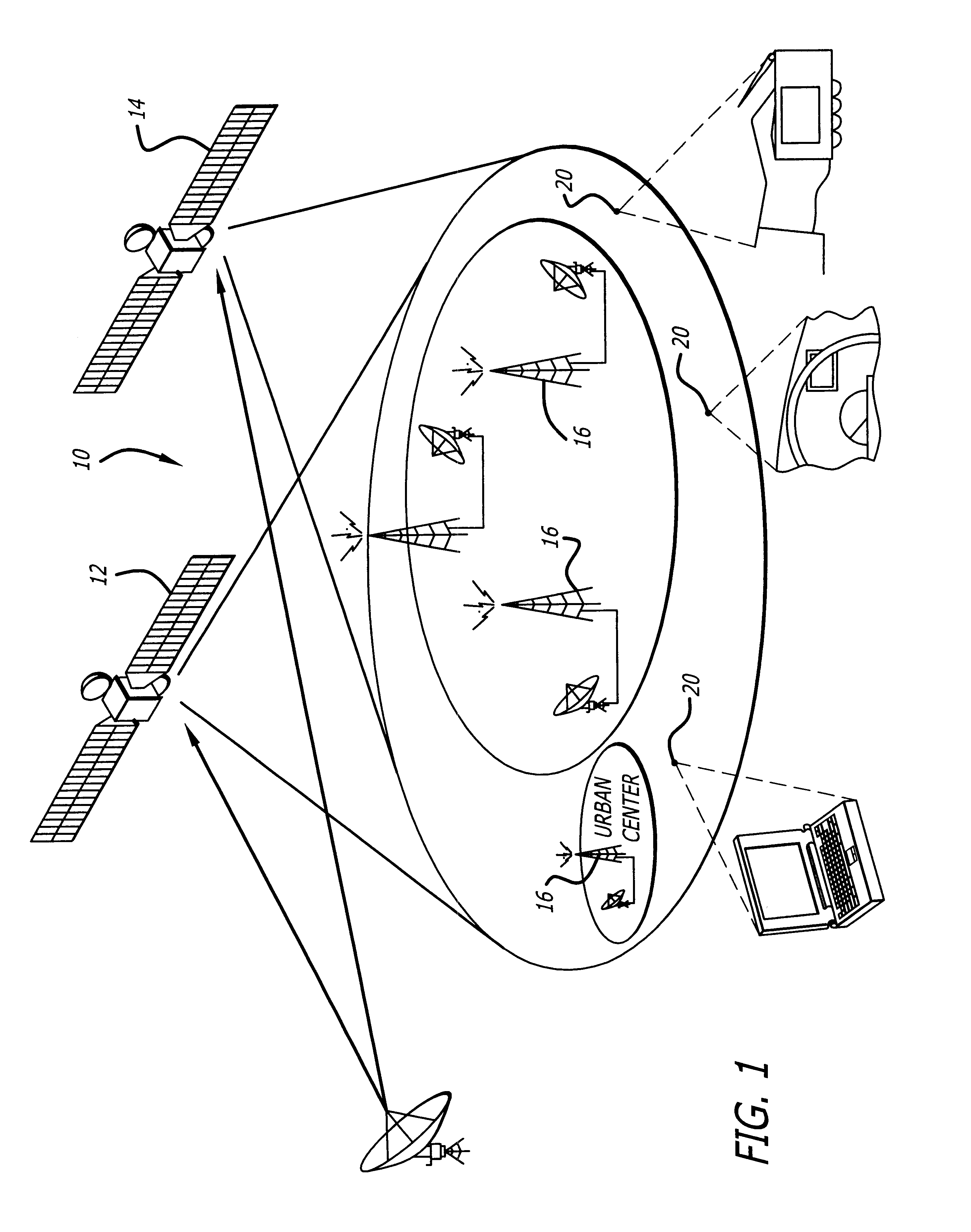

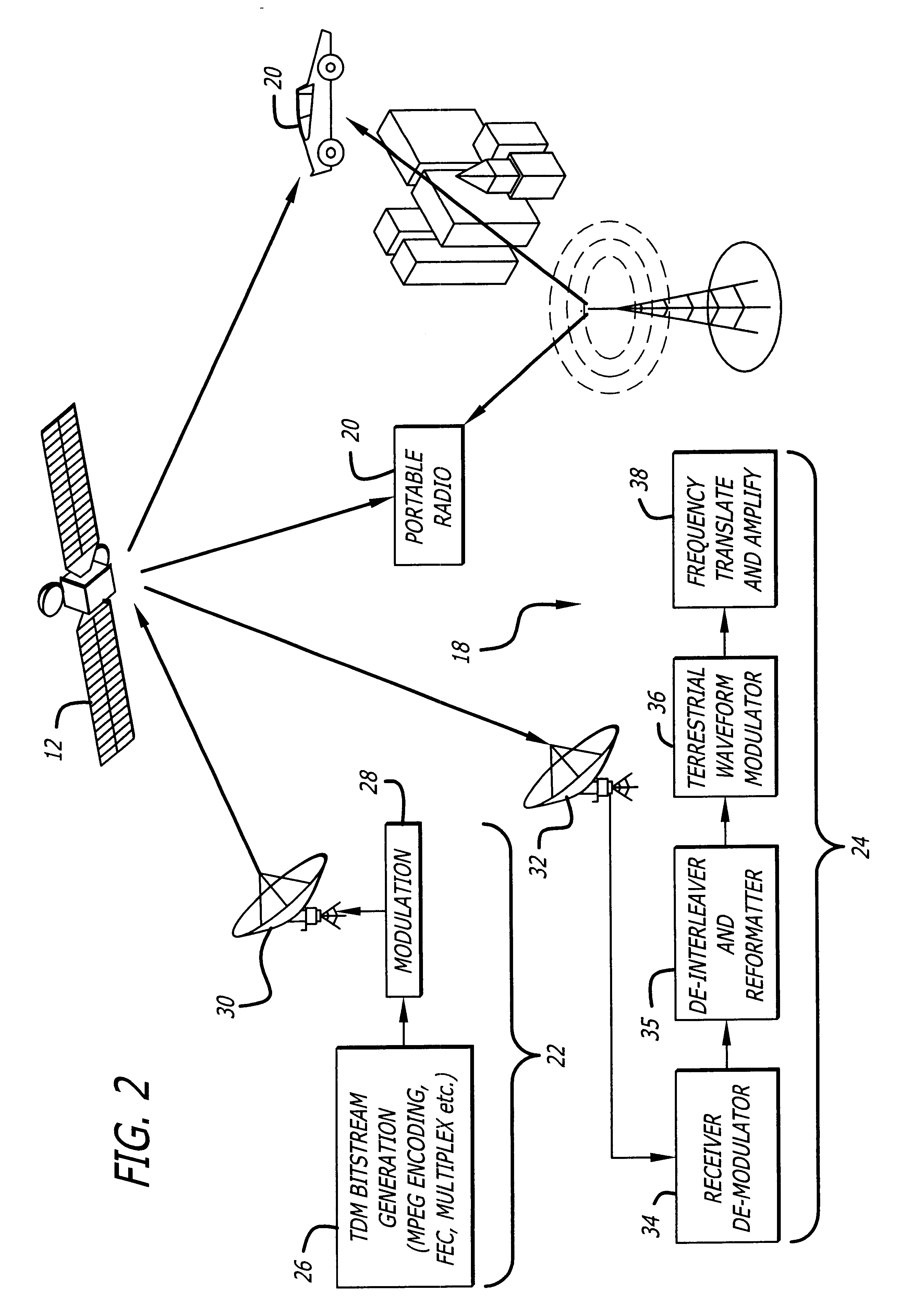

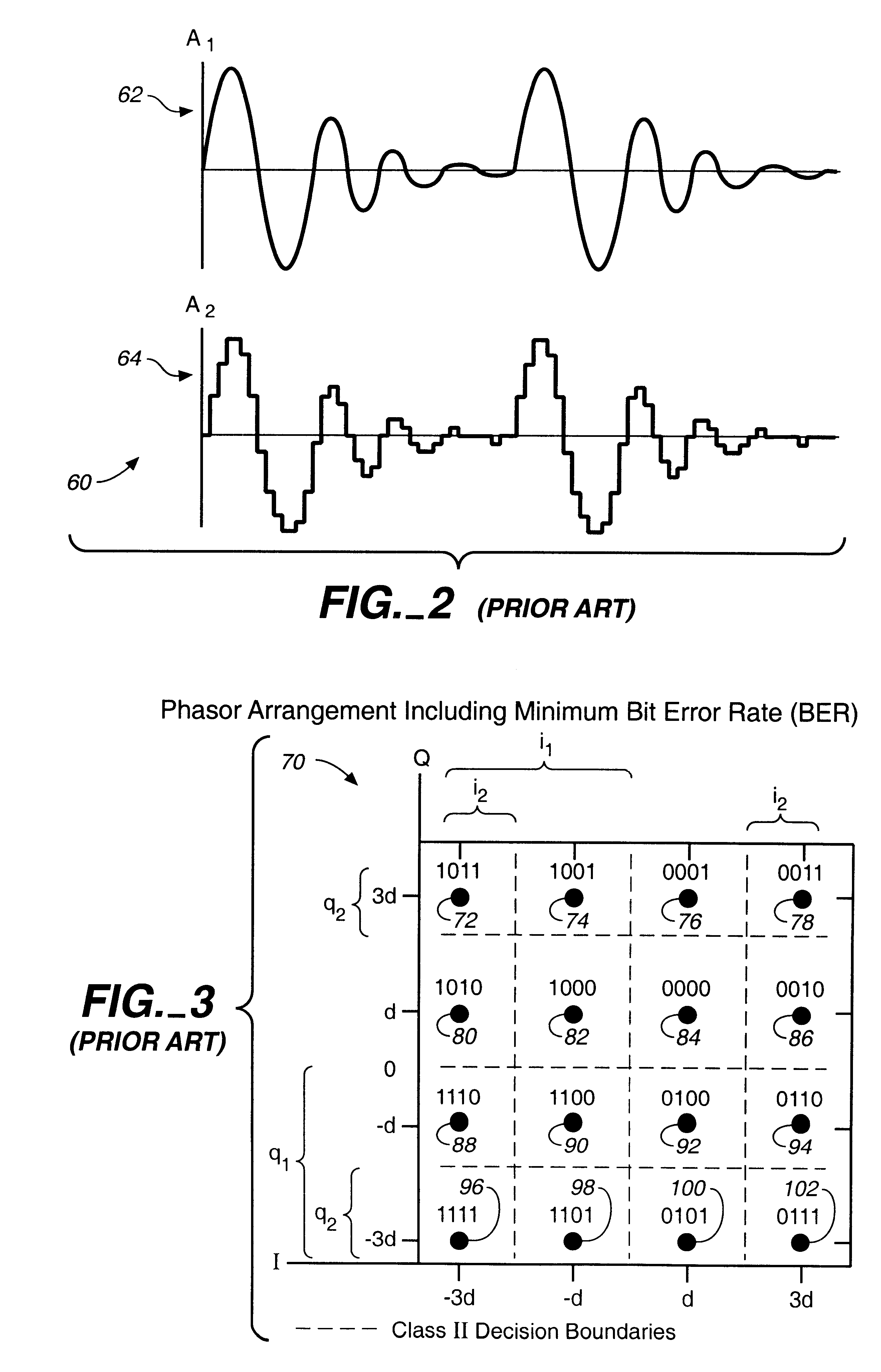

Satellite digital audio radio service tuner architecture for reception of satellite and terrestrial signals

InactiveUS6510317B1Broadcast transmission systemsRadio transmissionIntermediate frequencyRadio receiver

A satellite digital audio radio receiver system and method. The inventive receiver includes a circuit for down-converting a first ensemble in a received combined signal in a first mode of operation and for down-converting a second ensemble from the received combined signal in a second mode of operation. The first ensemble includes a first signal received from a first transmitter, a second signal received from a second transmitter, and a third signal received from a third transmitter. The second ensemble includes a second signal from the first transmitter, a second signal from the second transmitter, and a second signal from the third transmitter. A controller is included to selectively switch the circuit from the first mode to the second mode. The first ensemble comprises first, second and third frequency slots and the second ensemble comprises fourth, fifth, and sixth frequency slots. In the illustrative embodiment, the first and second transmitters are mounted on first and second satellites and the third transmitter is a terrestrial repeater. Both ensembles are transmitted in accordance with the XM frequency plan. The first ensemble is down-converted using low side injection and the second ensemble down-converted using high side injection. The inventive circuit includes a synthesized frequency source. The circuit further includes a first intermediate frequency down-conversion stage with a first mixer for mixing the received combined signals with the output of synthesized frequency source. The circuit further includes first and second surface acoustic wave filters for separating the first and second signals received from the third signals. The inventive circuit further includes a second intermediate frequency down-conversion stage having second and third mixers for mixing the outputs of the first and second filters, respectively, with the output of a local oscillator.

Owner:SIRIUS XM RADIO INC

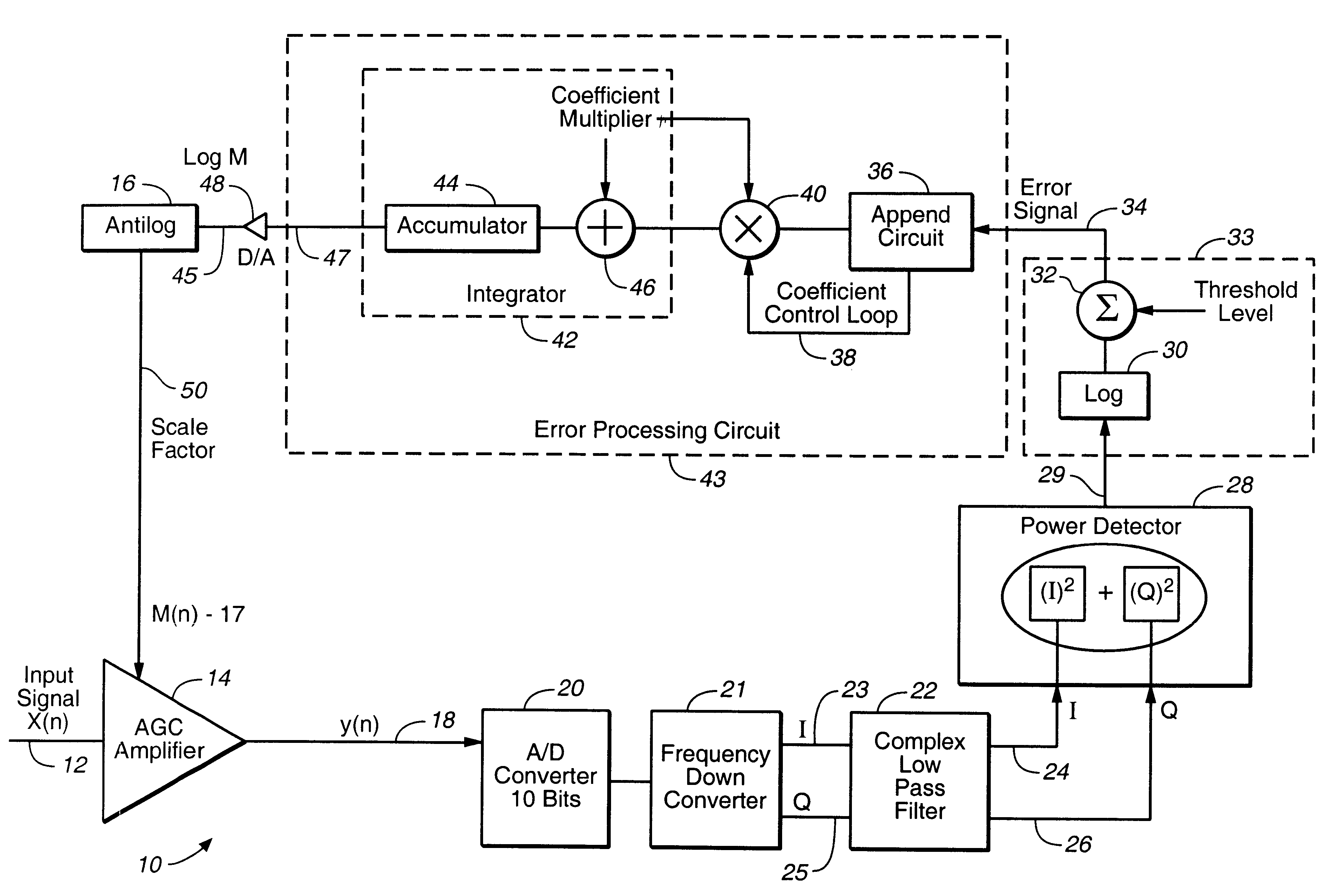

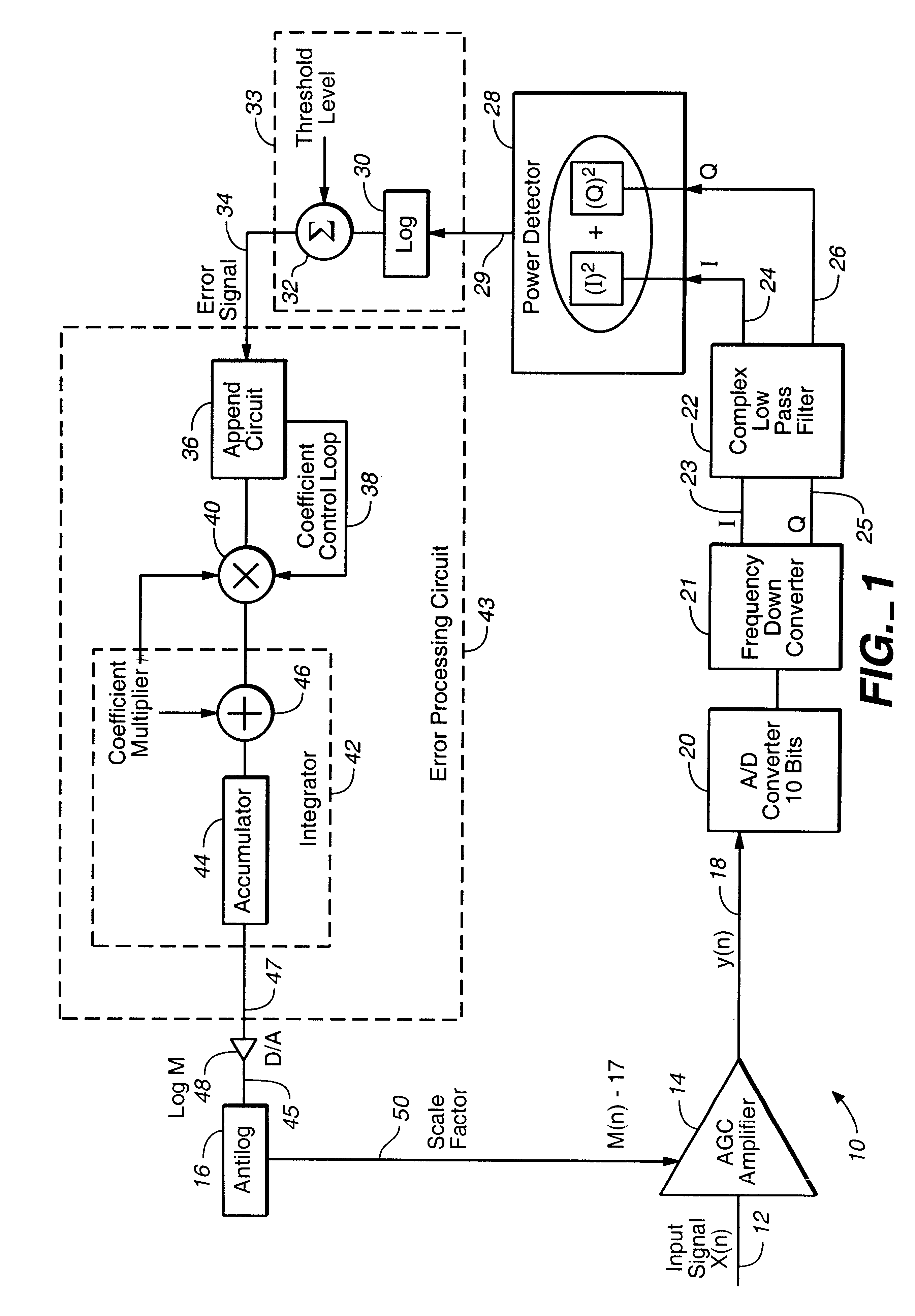

All digital automatic gain control circuit

A digital automatic gain control (AGC) system comprising an AGC amplifier configured to scale an input signal by a scale factor, and configured to generate an analog scaled input signal. An analog-to-digital (A / D) converter is configured to sample and convert the analog scaled input signal into a digital scaled input signal. The frequency down converted digital scaled input signal is processed by a power level detector circuit to detect its power level. The logarithmic comparison circuit (LCC) is configured to compare the detected power level of the digital scaled input signal to a predetermined reference signal and configured to generate a digital error signal. Finally, an error processing circuit is configured to process the digital error signal and configured to determine the scale factor of the AGC circuit. The test results show that for any applicable QAM constellation the AGC circuit of the present invention can control the broadest fades (or decreases) in the power level of the input signal with an accuracy up to 200 dB / per second.

Owner:REMEC BROADBAND WIRELESS NETWORKS LLC

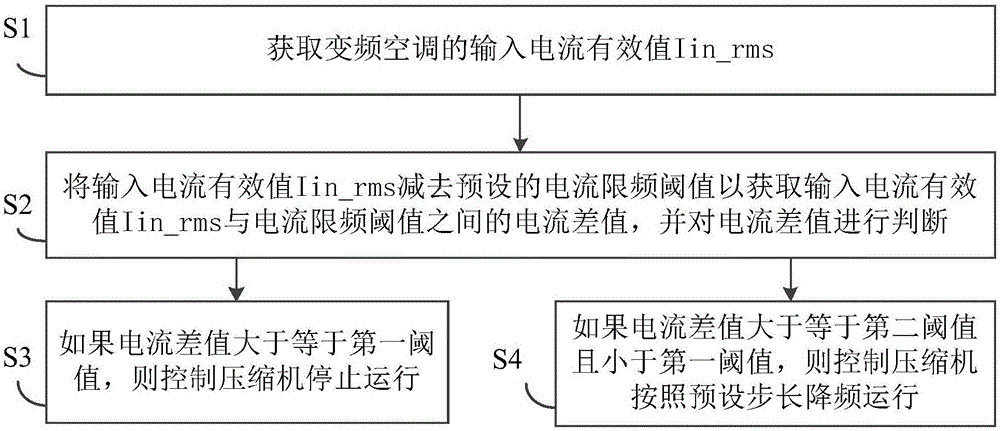

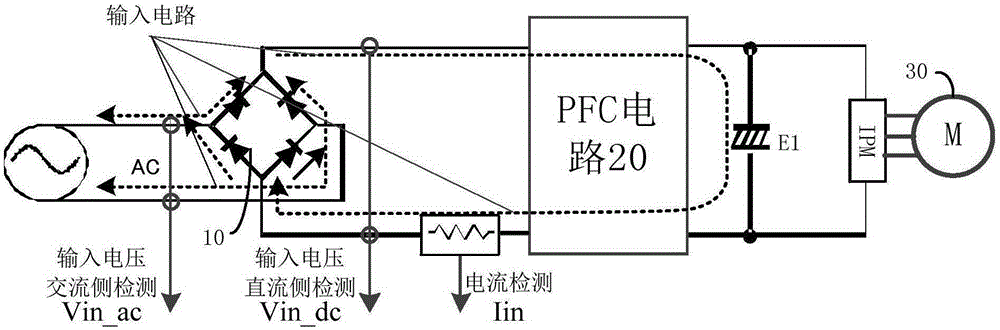

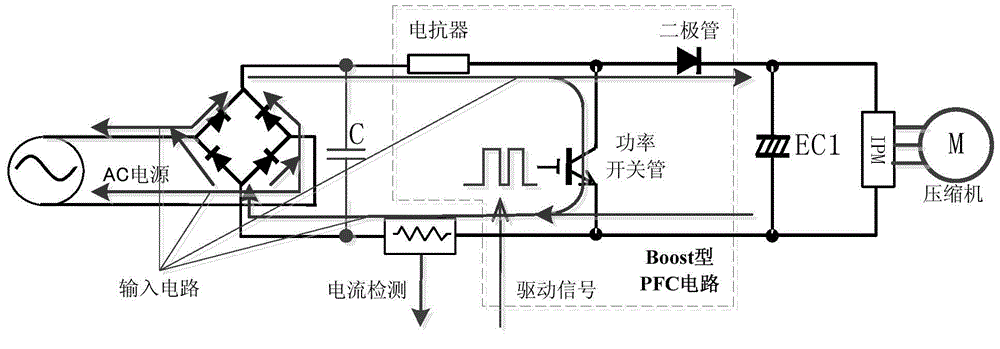

Variable-frequency air-conditioner current frequency limiting method and device

The invention discloses a variable-frequency air-conditioner current frequency limiting method and device. A variable-frequency air-conditioner comprises a rectification circuit, a power factor correction PFC circuit and a compressor. The input end of the PFC circuit is connected with the output end of the rectification circuit. The output end of the PFC circuit is connected with the compressor. The method comprises the following steps that the input current effective value Iin_rms of the variable-frequency air-conditioner is acquired; the preset current frequency limiting threshold is subtracted from the input current effective value Iin_rms so that a current difference value of the input current effective value Iin_rms and the current frequency limiting threshold is acquired, and the current difference value is judged; if the current difference value is greater than or equal to a first threshold, the compressor is controlled to stop operation; and if the current difference value is greater than or equal to a second threshold and less than the first threshold, the compressor is controlled to perform underclocking operation according to the preset step length, wherein the second threshold is less than the first threshold so that output power is reduced by controlling operation frequency of the compressor and then an objective of reducing input current is achieved, the heating condition of an input circuit is improved and an over-current fault can be avoided.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD +1

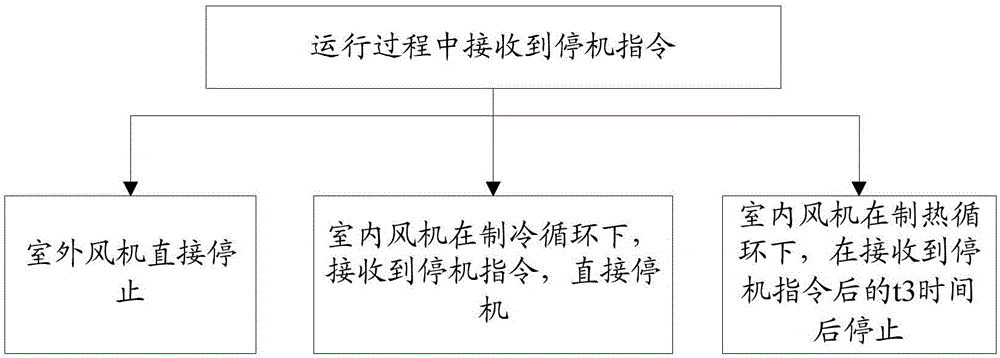

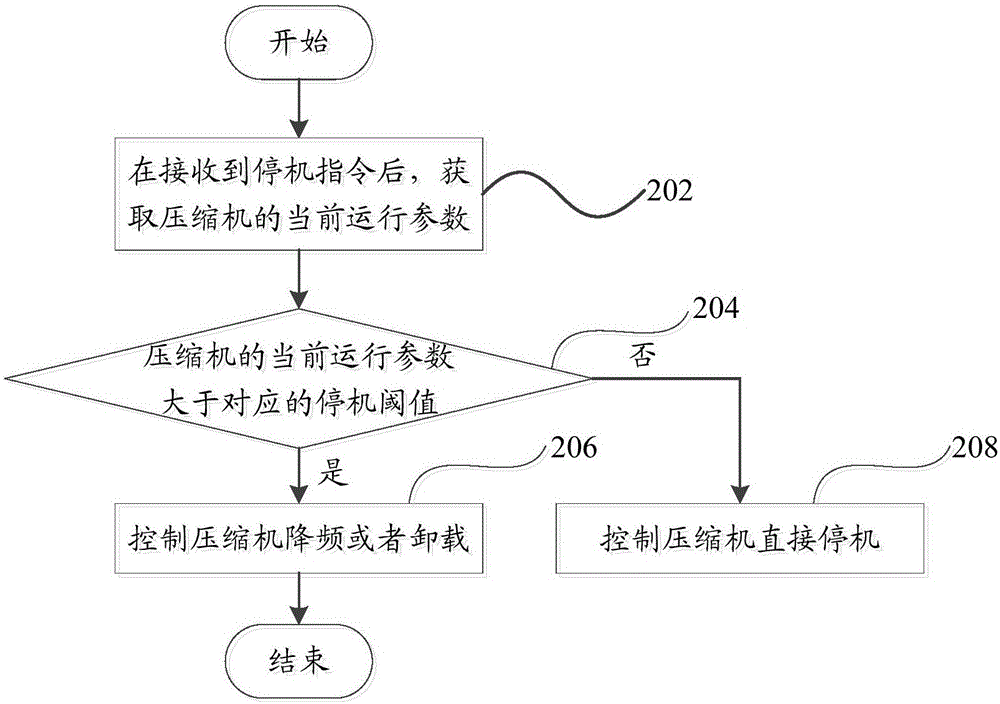

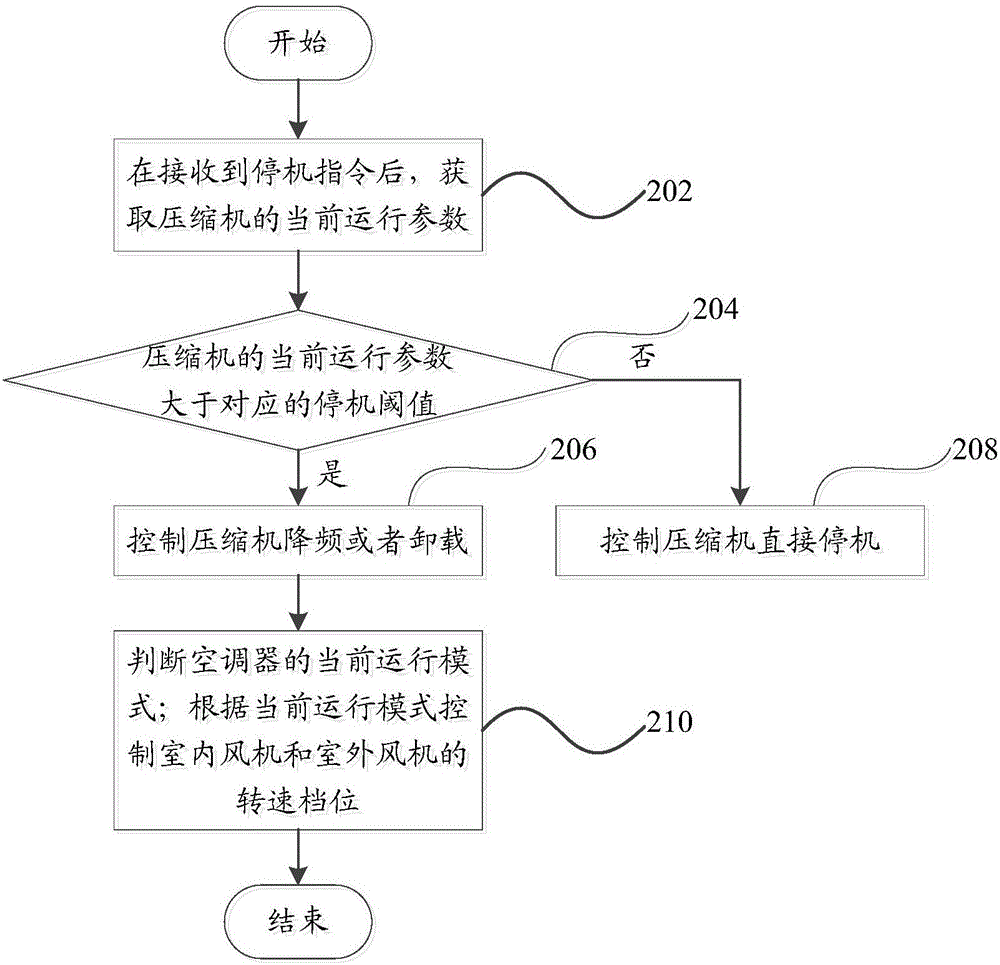

Air conditioner halt control method and device and air conditioner

ActiveCN106500241AImprove use reliabilityIncrease stop speedMechanical apparatusSpace heating and ventilation safety systemsControl theoryUnderclocking

The invention provides an air conditioner halt control method and device and an air conditioner. The air conditioner halt control method includes the steps that after a halt instruction is received, a current operation parameter of a compressor is obtained; the relationship between the current operation parameter of the compressor and a corresponding halt threshold value is judged; when it is judged that the current operation parameter of the compressor is larger than the corresponding halt threshold value, the compressor is controlled to be subjected to underclocking or unloading; when it is judged that the current operation parameter of the compressor is smaller than or equal to the corresponding halt threshold value, the compressor is controlled to be subjected to direct halt. By means of the air conditioner halt control method and device and the air conditioner, it can be guaranteed that the compressor is halted only under the situations that he load is small, and operation frequency is low, severe joggle, caused by sudden halt of the compressor, of the compressor and piping of the compressor is avoided, standard exceeding of the compressor piping is effectively prevented, pipe stress and deformation are reduced, the piping service life is prolonged, and use reliability of the air conditioner is improved.

Owner:WUHU MATY AIR CONDITIONING EQUIP CO LTD +1

Control method and system for preventing frequency fluctuation of air conditioner compressor

ActiveCN106152382AGuaranteed uptimeImprove reliabilitySpace heating and ventilation safety systemsSpace heating and ventilation control systemsUnderclockingHot Temperature

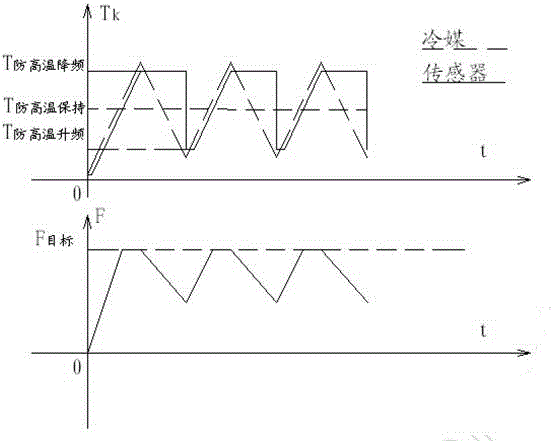

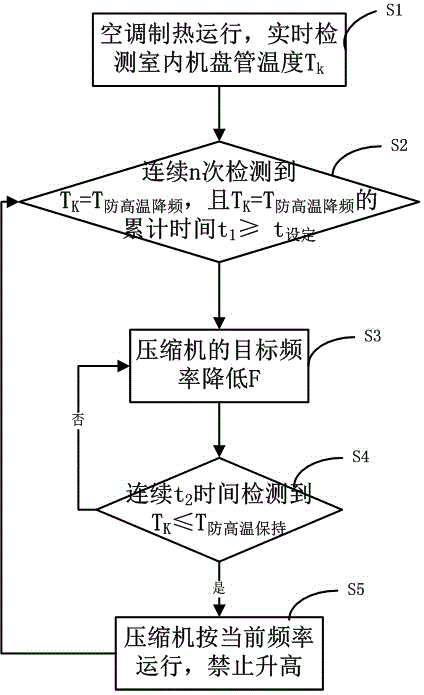

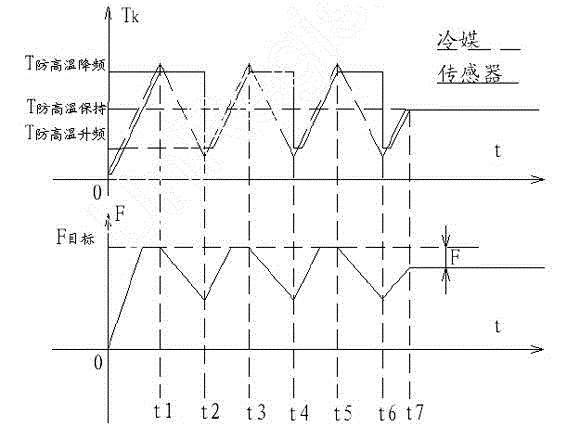

The invention relates to a control method and system for preventing the frequency fluctuation of an air conditioner compressor, which detects the coil temperature T of the indoor unit in real time during the heating operation of the air conditioner k ;If T is detected n consecutive times K = T 防高温降频 , and T K = T 防高温降频 cumulative time t 1 ≥t 设定 ;Reduce the target frequency of the compressor by F. When the present invention detects that the temperature of the coil of the indoor unit fluctuates frequently, the target frequency of the compressor in the anti-high temperature protection is lowered and corrected successively until the compressor can run stably at the target frequency to ensure the use effect of the air conditioner.

Owner:QINGDAO HAIER AIR CONDITIONER GENERAL CORP LTD

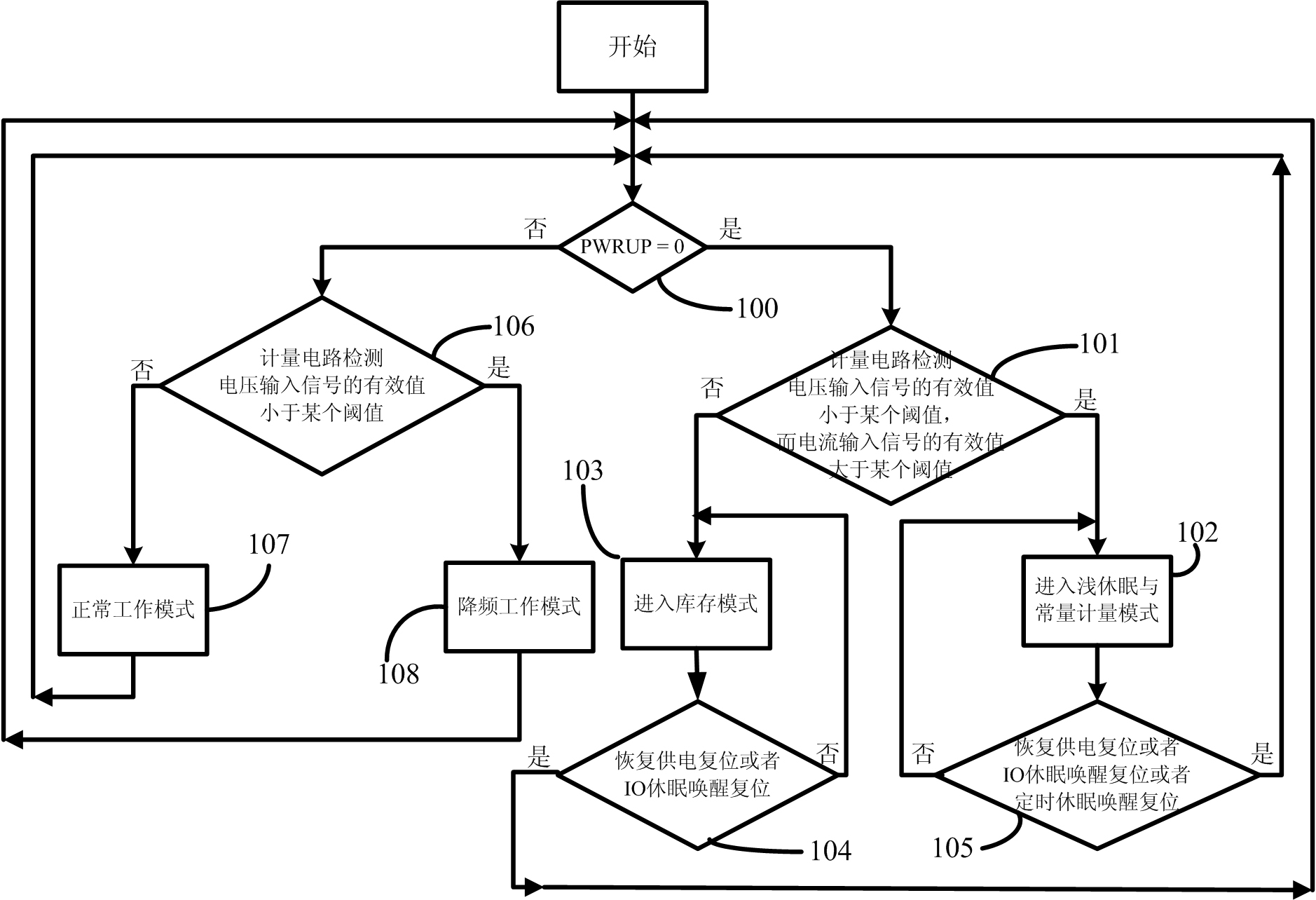

Method for reducing power consumption of electric energy metering chip

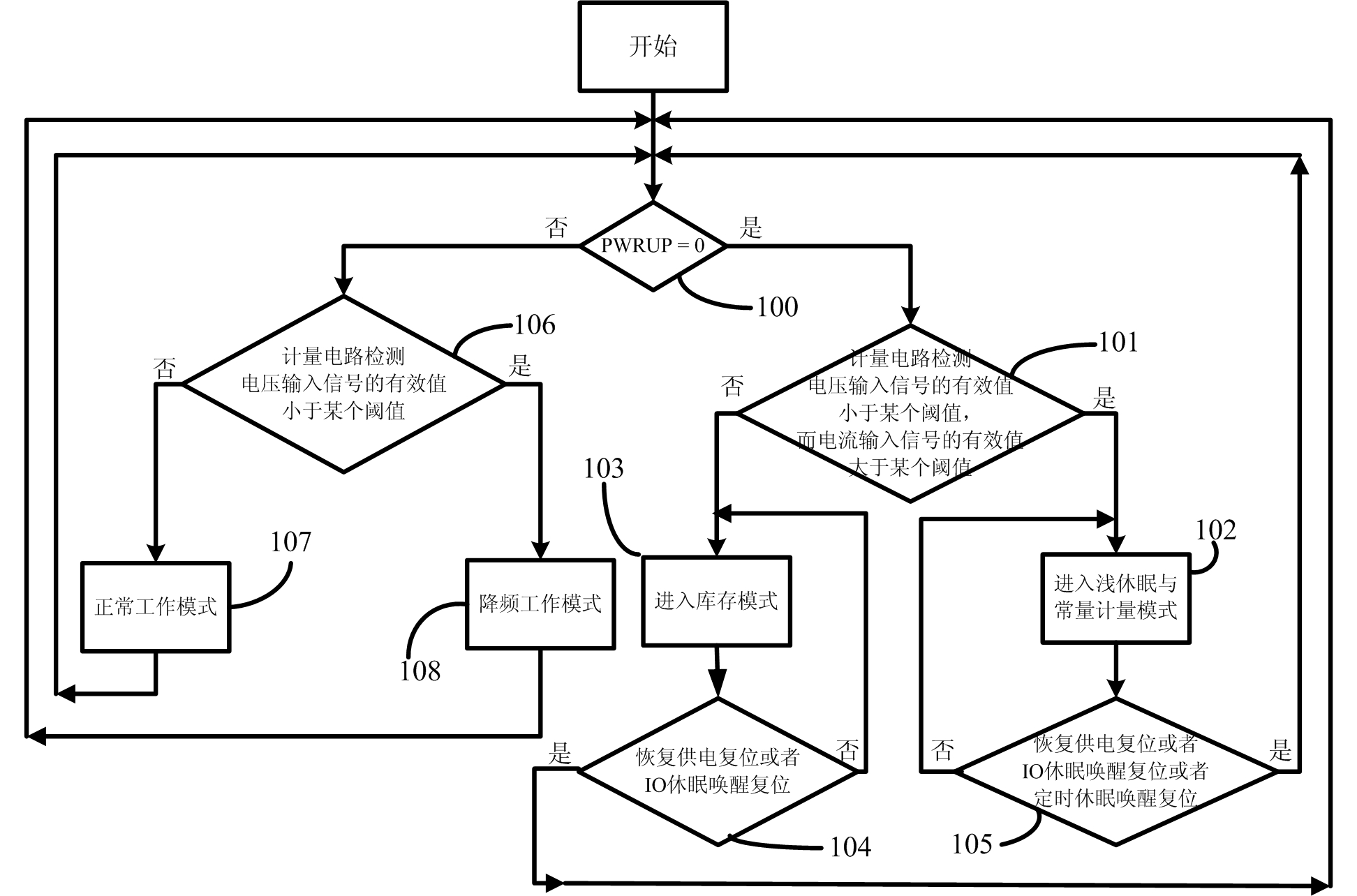

The invention provides a method for reducing power consumption of an electric energy metering chip. The electric energy metering chip is provided with two clock domains, wherein a CPU (Central Processing Unit) of the electric energy metering chip is located at a clock region I and a metering circuit is located at a clock region II; the clock region I selectively utilizes a low-frequency clock and high-frequency clock; for the clock region I, the movement can be stopped to keep a constant electrical level; the clock region II selectively utilizes a low-frequency clock, a frequency-reducing clock and a high-frequency clock and for the clock region II, the movement can be stopped to keep the constant electrical level; and the electric energy metering chip can be selectively powered by a battery or a power line. According to the method disclosed by the invention, a plurality of clock combinations are arranged for a chip of an electric energy metering system and the switching of the clock combinations is carried out according to current power supply states of the chip of the system and a resetting generation source is dormant or awakened, so that the method is good for reducing the power consumption of the chip of the electric energy metering system.

Owner:HANGZHOU VANGO TECH

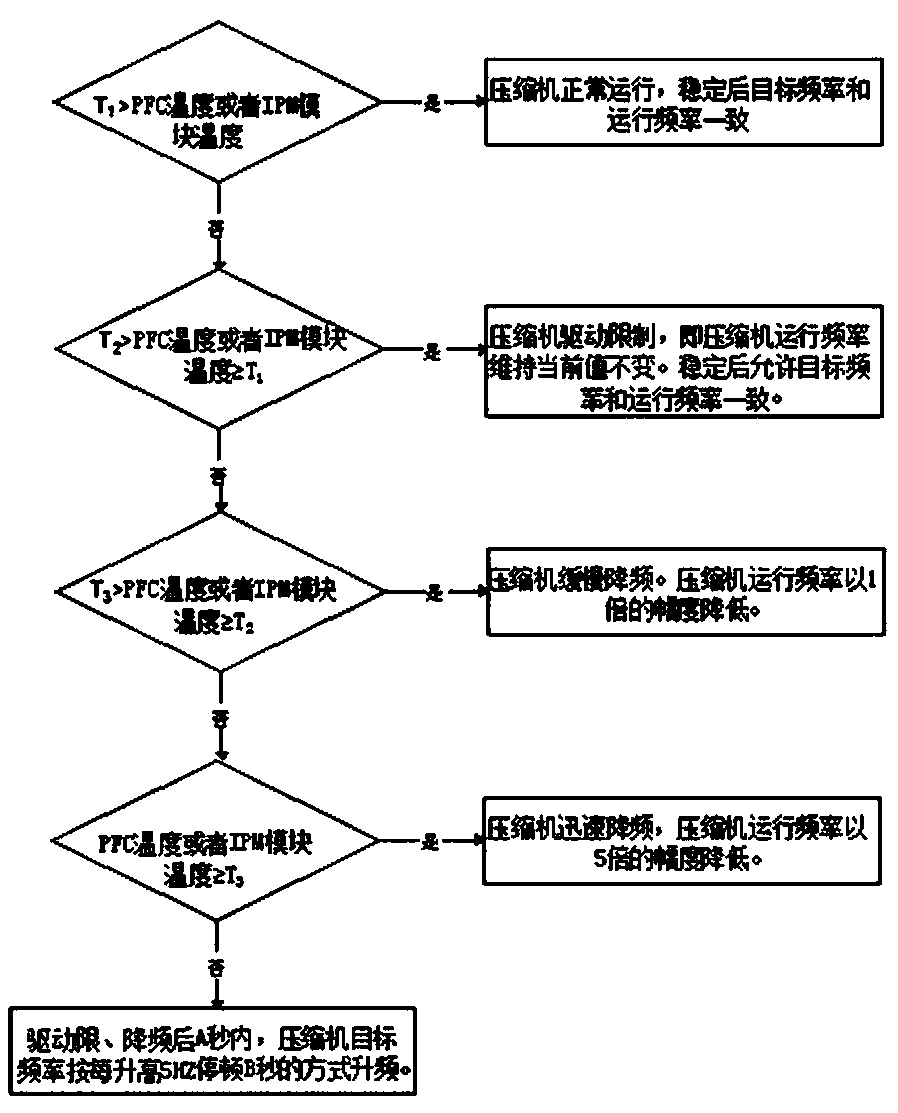

Control method of frequency limiting and reducing of compressor and inverter air conditioner

InactiveCN109163430ARun continuouslyAvoid safety accidentsMechanical apparatusSpace heating and ventilation safety systemsUnderclockingEngineering

The invention discloses a control method of frequency limiting and reducing of a compressor and an air conditioner using the method. The control method of frequency limiting and reducing comprises thesteps of detecting running parameters of the compressor, judging the interval range of the running parameters, and according to the judgment result, carrying out frequency limiting and reducing control over the compressor. Through monitoring of the current of the compressor and the temperature of a drive board, the running frequency of the compressor is controlled, elements of the compressor, thedrive board and the like can run within the normal range, happening of electric appliance safety accidents can be avoided, meanwhile, a unit can continuously run, frequent shutdown is not needed, andindoor temperature stability is ensured.

Owner:GREE ELECTRIC APPLIANCES INC

Drive method for display panel, and display device

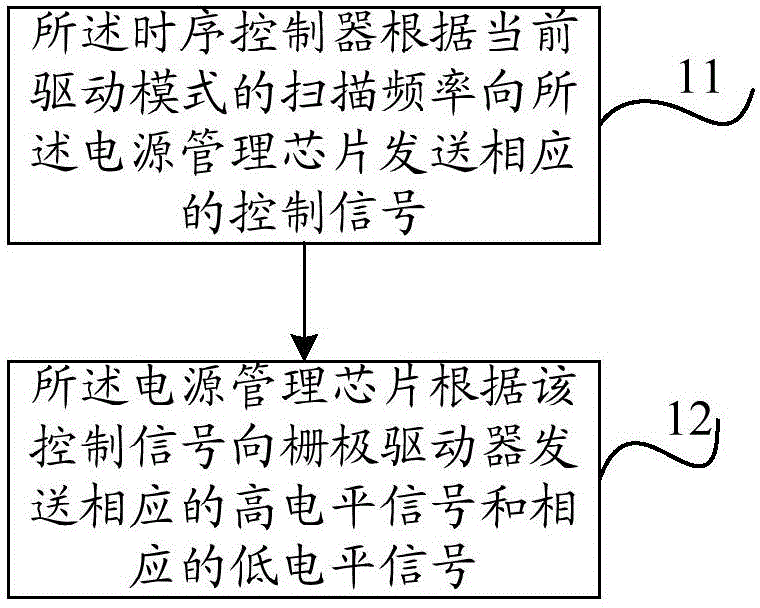

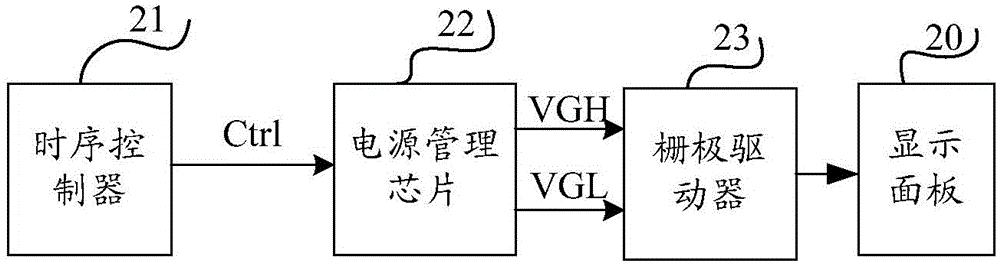

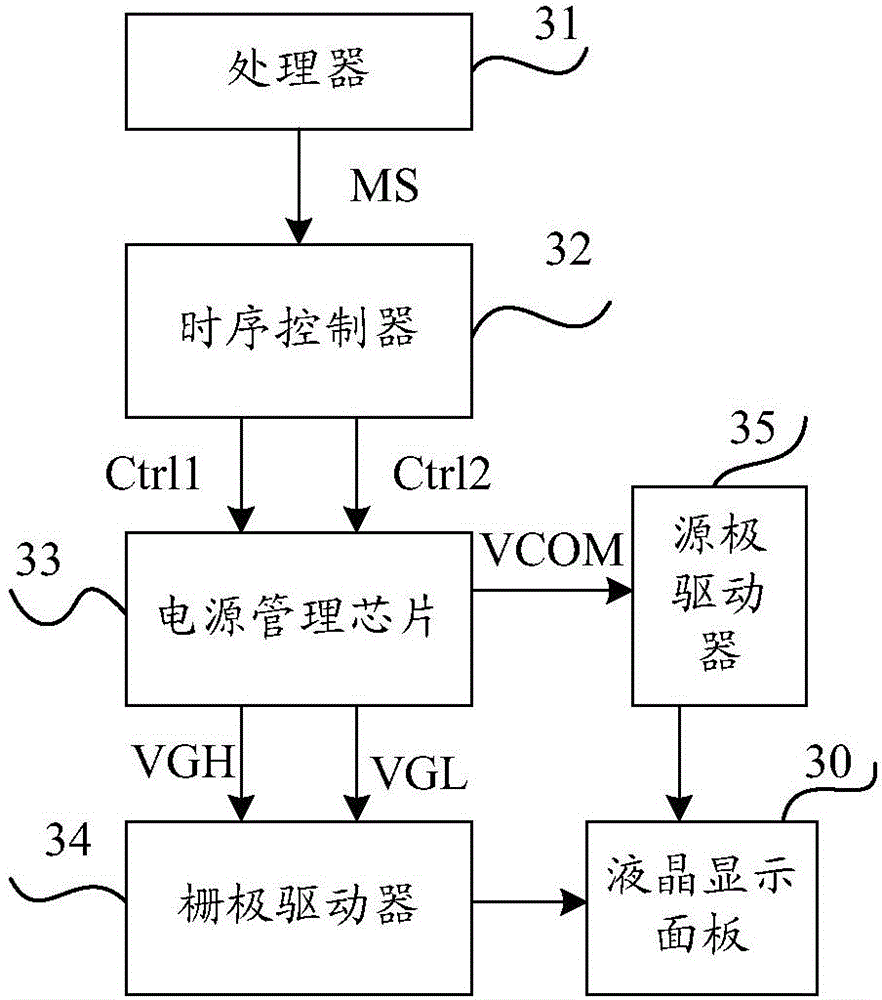

The invention provides a drive method for a display panel, and a display device. The drive method for the display panel is applied to driving the display device which comprises the display panel, and further comprises a time schedule controller, a power supply management chip and a gate electrode driver for providing a gate electrode drive signal for the display panel. The drive method comprises the following steps: sending a corresponding control signal to the power supply management chip according to the screening frequency of a current drive mode through the time schedule controller; sending a corresponding high electric-level signal and a corresponding low electric-level signal to the gate electrode driver according to the control signal through the power supply management chip; and along with the reduction of the scanning frequency, reducing voltage of the corresponding high electric-level signal, and reducing an absolute value of voltage of the corresponding low electric-level signal. When the drive method is used for driving the display panel in a frequency-reducing mode, the power consumption of the liquid crystal display panel is reduced by reducing the voltage of the high electric-level signal and the voltage of the low electric-level signal.

Owner:HEFEI BOE OPTOELECTRONICS TECH +1

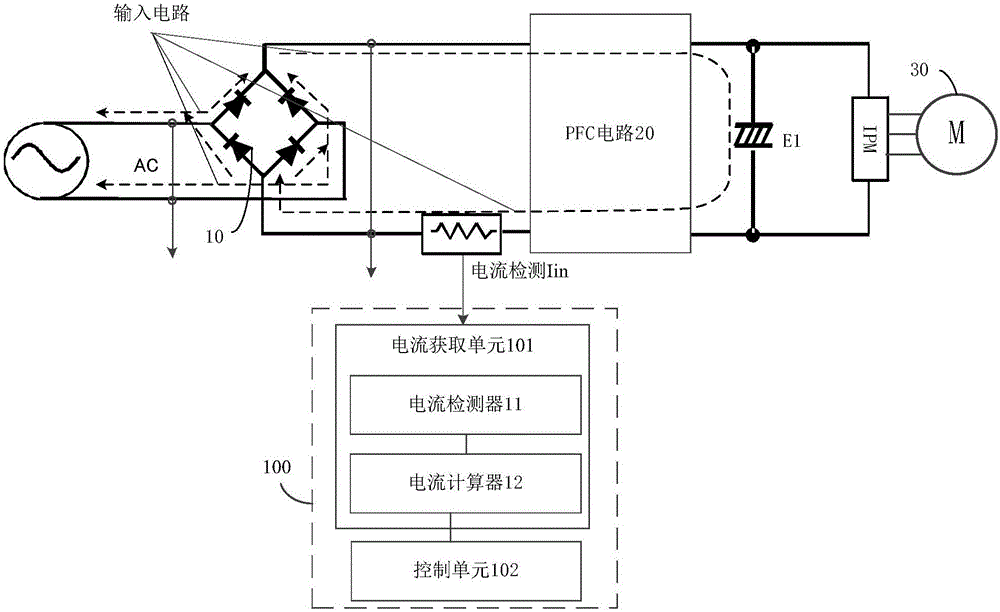

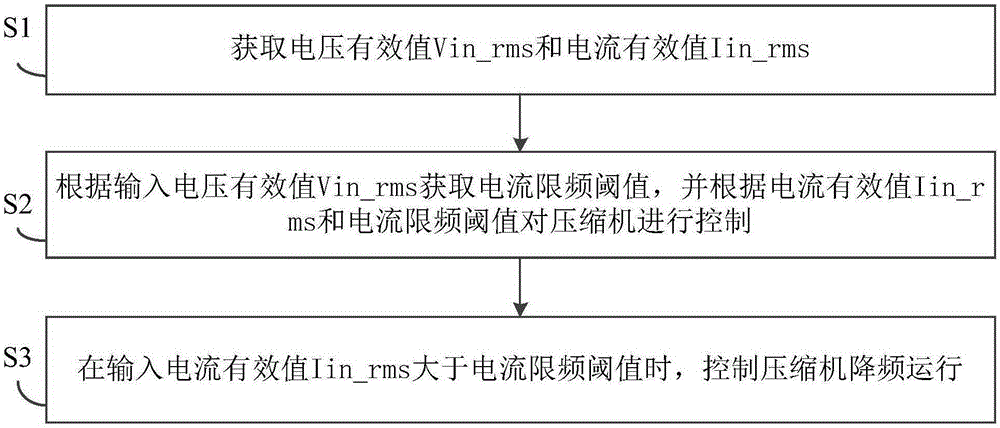

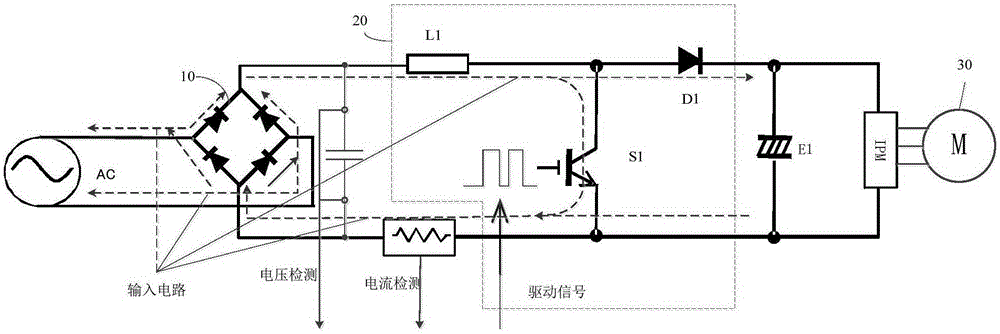

Input-voltage-self-adaption-based current frequency limiting method and apparatus of PFC circuit

ActiveCN105186842AImprove feverReduce output powerEfficient power electronics conversionPower conversion systemsPower flowPower factor

The invention discloses an input-voltage-self-adaption-based current frequency limiting method and apparatus of a power factor correction (PFC) circuit in a variable-frequency air conditioner. The output terminal of the PFC circuit is connected with a load being a compressor. The method comprises the following steps: obtaining a voltage effective value Vin_rms and a current effective value Iin_rms; obtaining a current frequency-limiting threshold value based on the input voltage effective value Vin_rms and controlling the compressor according to the current effective value Iin_rms and the current frequency-limiting threshold value; and controlling the compressor to carry out frequency-reduction operation when the current effective value Iin_rms being larger than the current frequency-limiting threshold value. Therefore, the output power is reduced; an objective of input current reduction is achieved; the heating situation of the input circuit is improved; and the system reliability is enhanced.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD +1

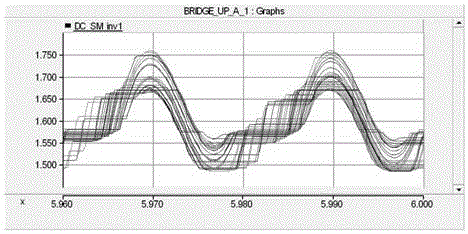

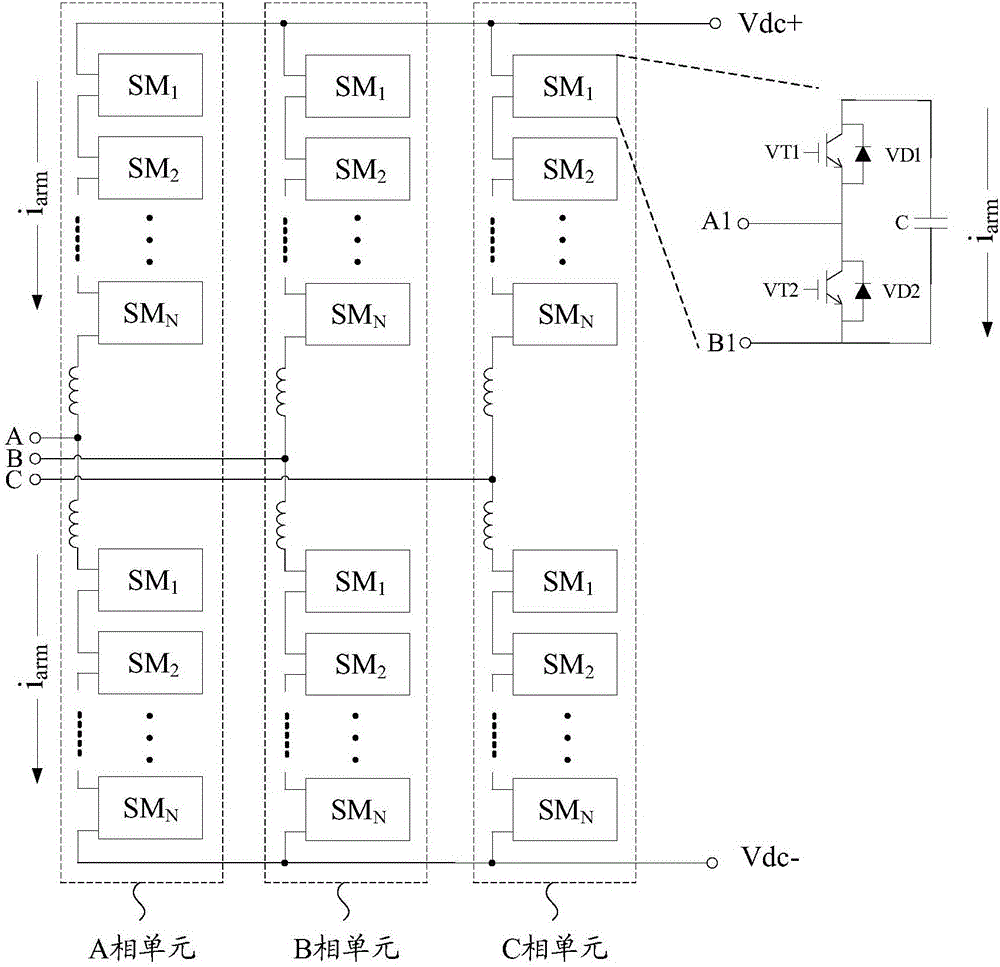

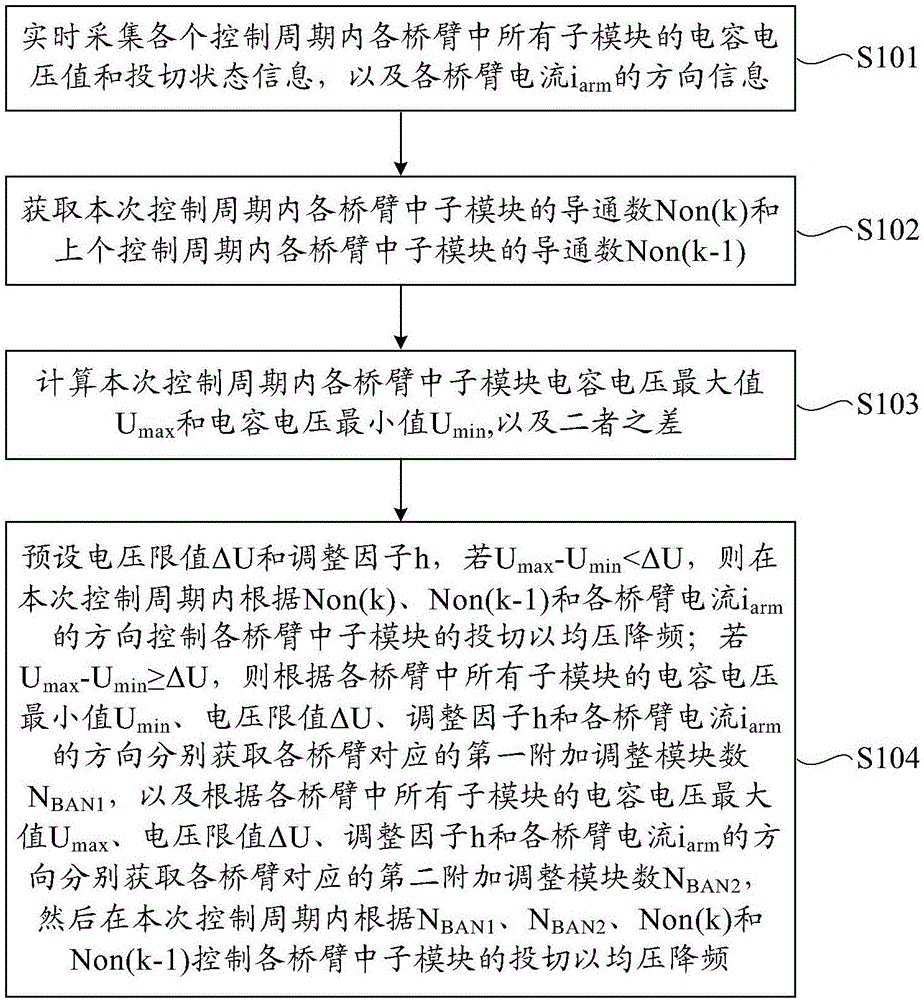

Voltage balance modulation method and device based on nearest level approximation

ActiveCN106787883AGuaranteed capacitor voltageGuaranteed Capacitor Voltage ControlAc-dc conversionCapacitanceCapacitor voltage

The invention provides a voltage balance modulation method based on nearest level approximation. The voltage balance modulation method based on nearest level approximation comprises the following steps: presetting a voltage limitation value delta U and an adjusting factor H; if Umax-Umin is less than delta U, controlling switching of submodules in various bridge arms in the control period at this time according to Non(k), Non (k-1) and direction of current iarm of the various bridge arms to implement voltage balance underclocking; if Umax-Umin is greater than or equal to delta U, respectively acquiring first additional adjusting module numbers NBAN1 corresponding to the bridge arms according to capacitor voltage minimum values Umin of submodules in the various bridge arms, the voltage limitation value delta U, the adjusting factor h and the directions of current iarm of the various bridge arms, and respectively acquiring second additional adjusting module number NBAN2 corresponding to the various bridge arms according to capacitor voltage maximum values Umax of the submodules in the various bridge arms, the voltage limitation value delta U, the adjusting factor h and the directions of the current iarm of the various bridge arms; and controlling switching of the submodules in the various bridge arms in the control period at this time according to NBAN 1, NBAN 2, Non (k) and Non (k-1) to implement voltage balance underclocking. Correspondingly, the invention provides a voltage balance modulation device. On the premise of meeting requirements of voltage balance, switching frequency of a power device is reduced, and switching loss is reduced.

Owner:TBEA SUNOASIS

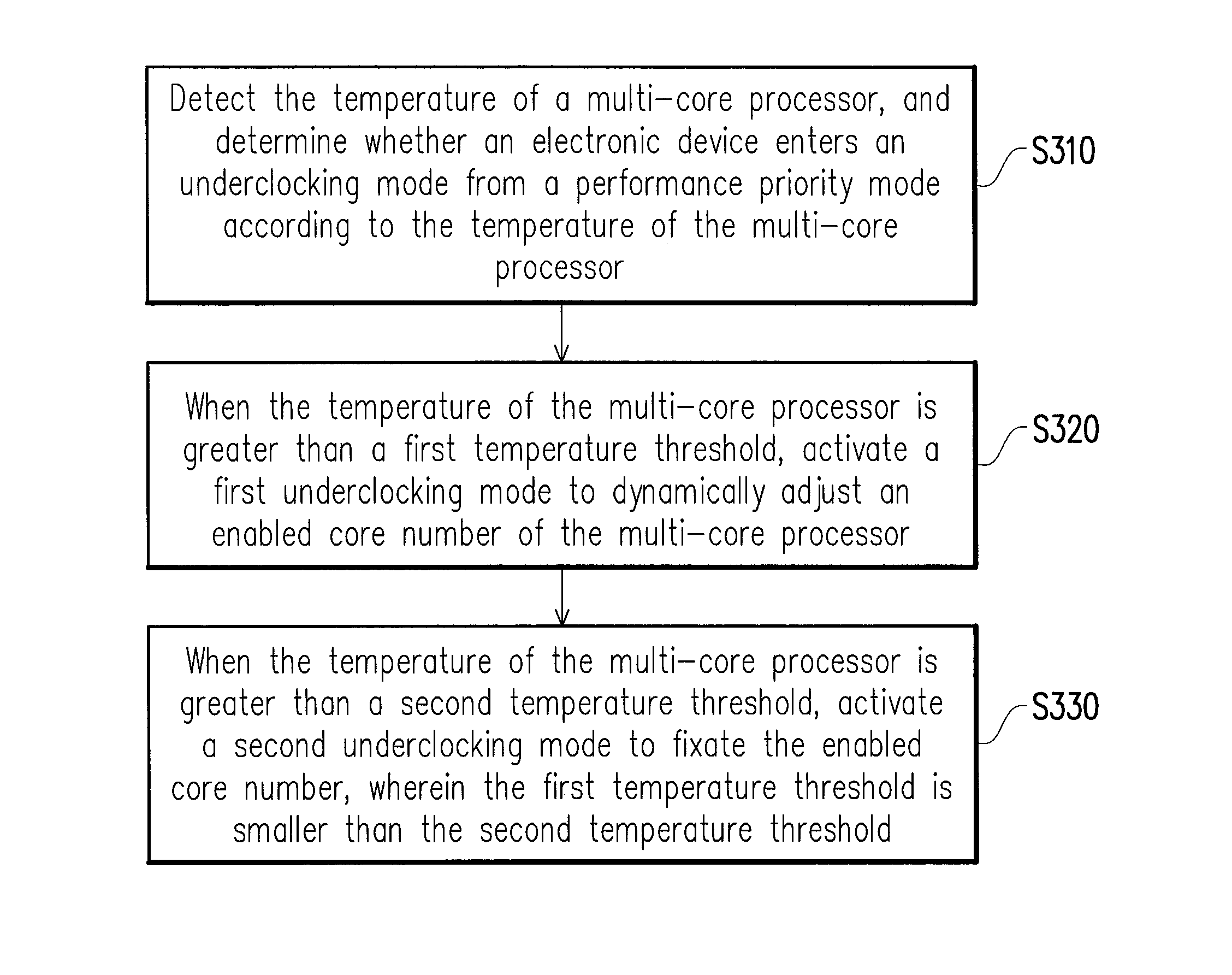

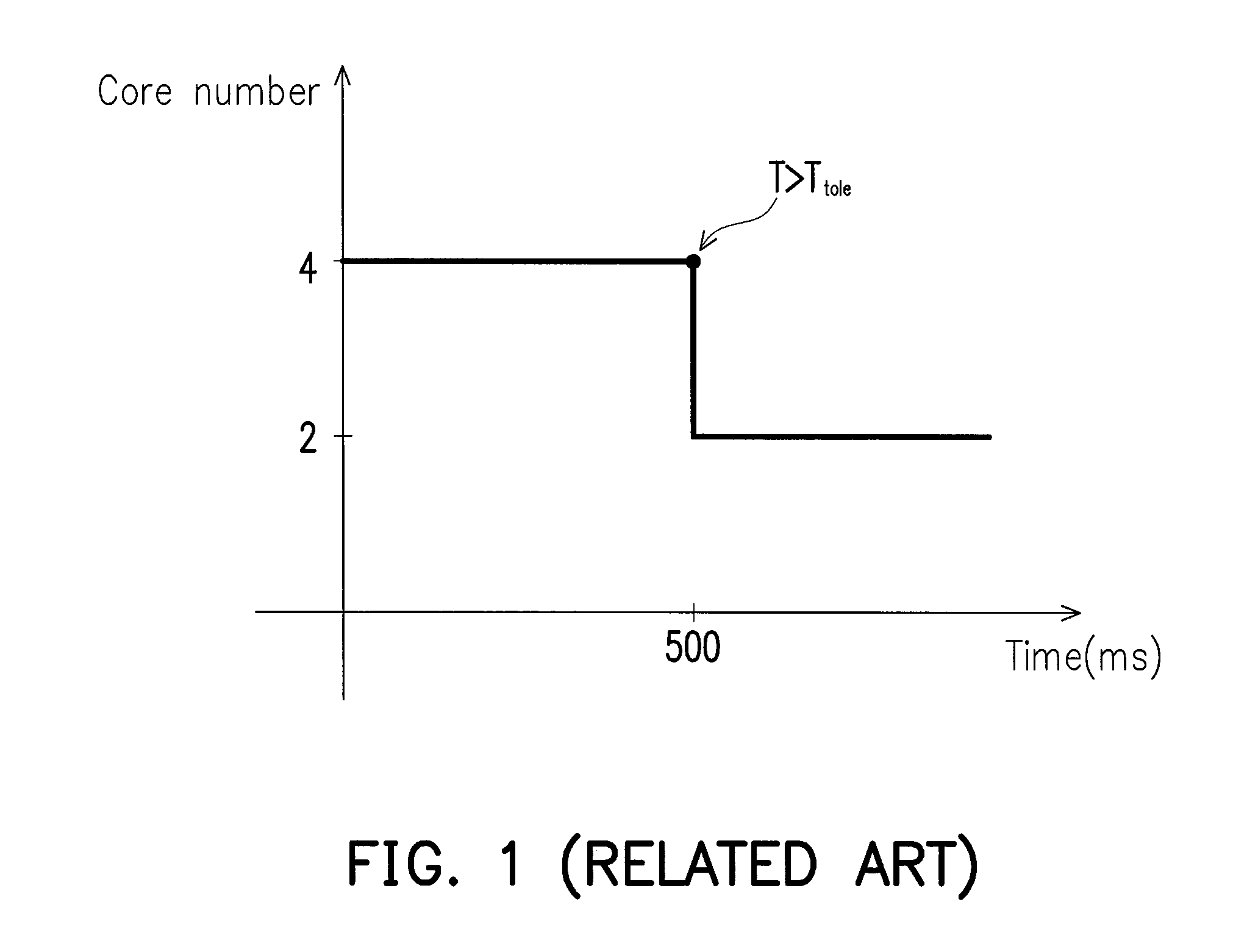

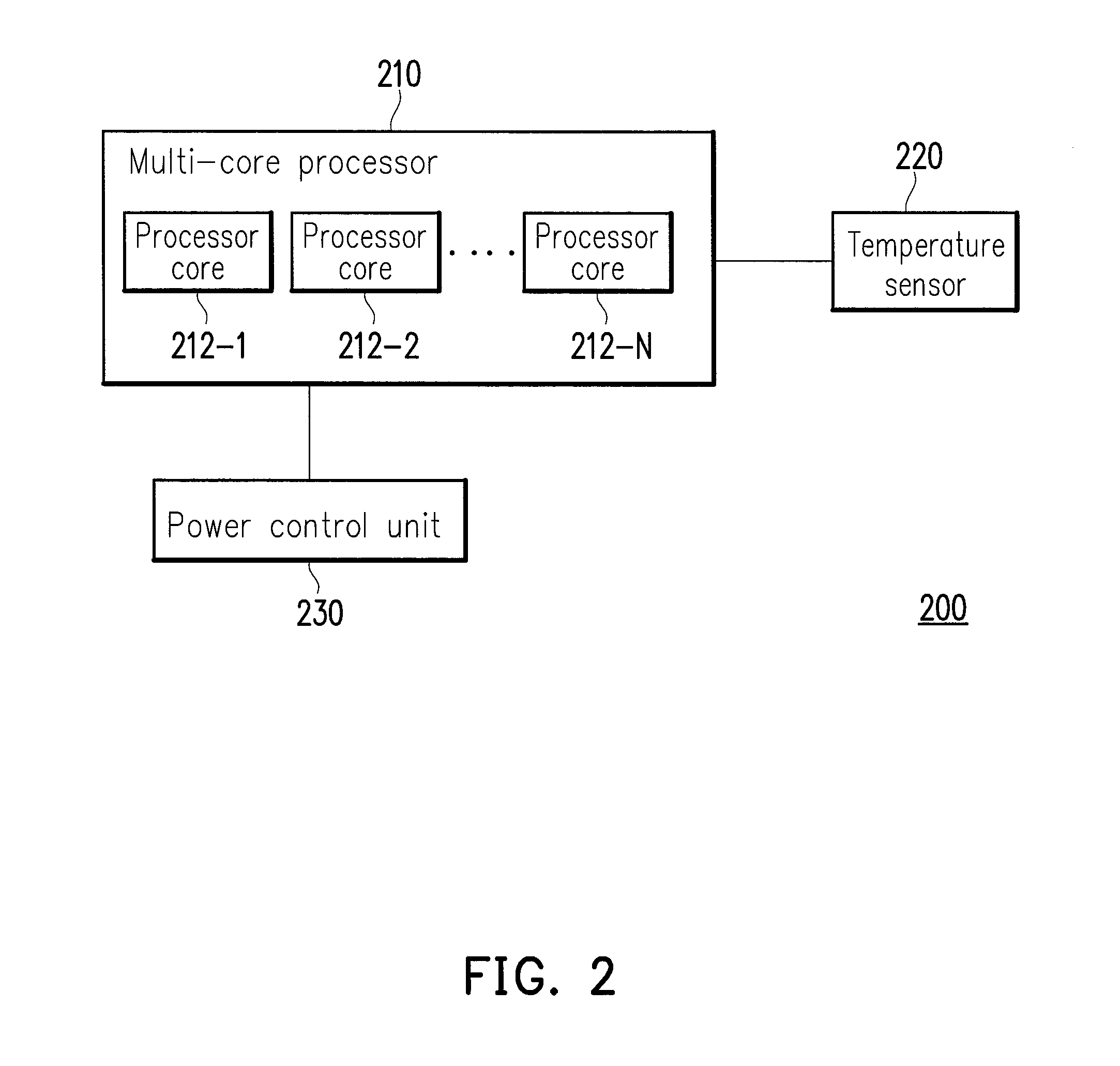

Electronic device with power management mechanism and power management method thereof

InactiveUS20140075223A1Reduce power consumptionIncrease temperatureDigital data processing detailsProgram controlElectric devicesUnderclocking

An electronic device with a power management mechanism and a power management method thereof are disclosed. The electronic device includes a multi-core processor and a temperature sensor. The multi-core processor has a plurality of processor cores. The temperature sensor is coupled to the multi-core processor. The temperature sensor detects the temperature of the multi-core processor and determines whether the electronic device enters an underclocking mode from a performance priority mode according to the detected temperature. When the temperature of the multi-core processor is greater than a first temperature threshold, the multi-core processor controls the electronic device to enter a first underclocking mode and dynamically adjusts an enabled core number. When the temperature of the multi-core processor is greater than a second temperature threshold, the multi-core processor controls the electronic device to enter a second underclocking mode. The first temperature threshold is smaller than the second temperature threshold.

Owner:HTC CORP

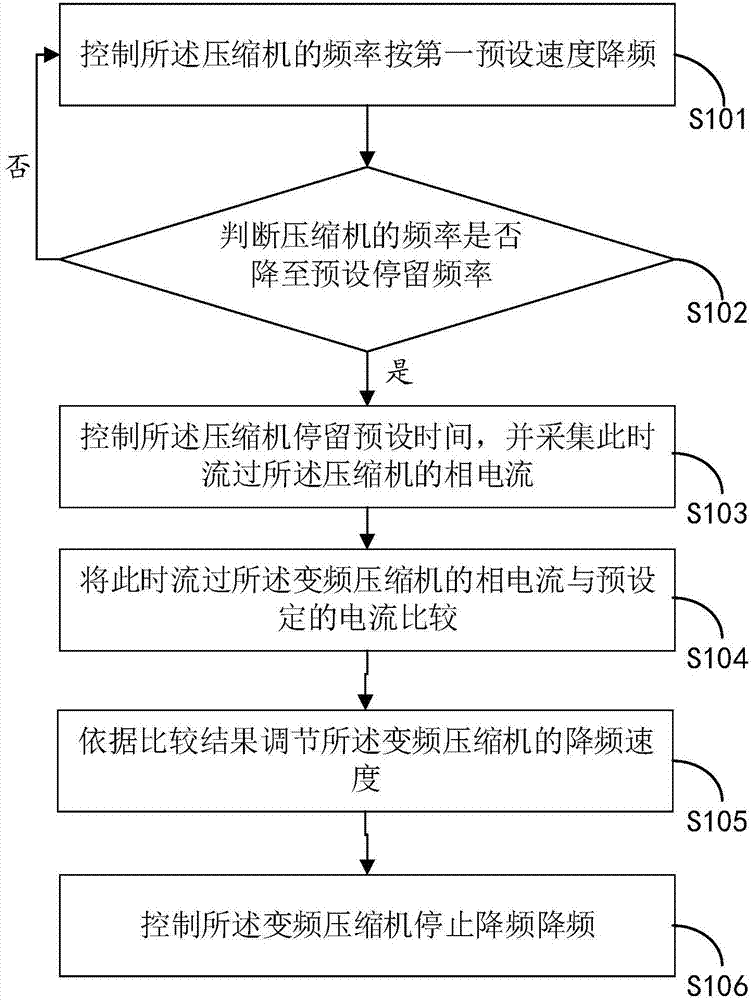

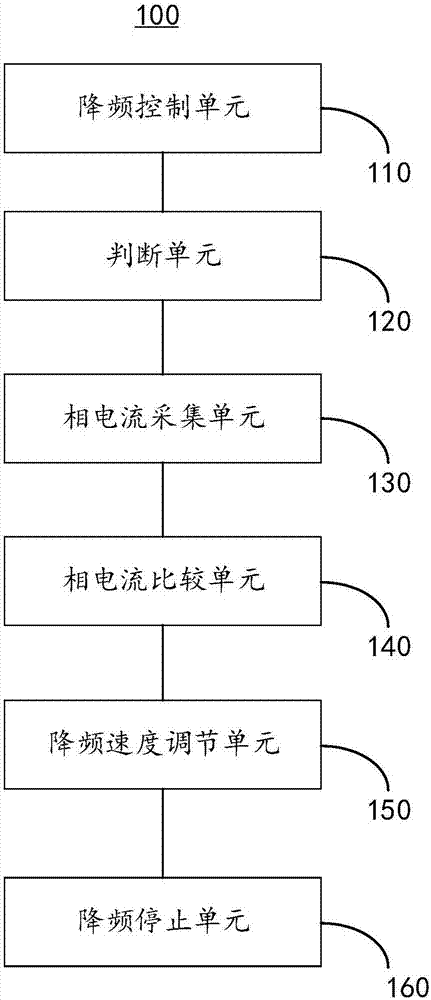

Frequency reduction control method and device for variable frequency compressor

ActiveCN107883553ARealize detectionNot easy to get out of stepMechanical apparatusSpace heating and ventilation safety systemsPhase currentsEngineering

The invention provides a frequency reduction control method and a device for a variable frequency compressor, and relates to the technical field of variable frequency compressors, in particular to thefrequency reduction control method and the device for the variable frequency compressor. The method comprises the following steps that the variable frequency compressor is controlled to perform frequency reduction at a first preset speed, and when the frequency of the variable frequency compressor is reduced to a preset staying frequency, the magnitude of the phase current and the preset currentis compared, and the frequency reduction speed of the variable frequency compressor is controlled according to the comparison result. A staying frequency is preset in the frequency reduction process of the variable frequency compressor, and when the frequency of the variable-frequency compressor is reduced to the staying frequency, the frequency of the variable frequency compressor can keep the frequency for a period of time so as to realize the detection of the phase current at the moment, and meanwhile, the result is compared according to the comparison result of the phase current and the preset current. The variable frequency compressor is controlled to carry out frequency reduction at a preset speed, so that in the frequency reduction process, the actual phase current of the variable frequency compressor is closer to the preset phase current of the system, and the situation of loss of synchronism doesn't easily occur is avoided.

Owner:NINGBO AUX ELECTRIC

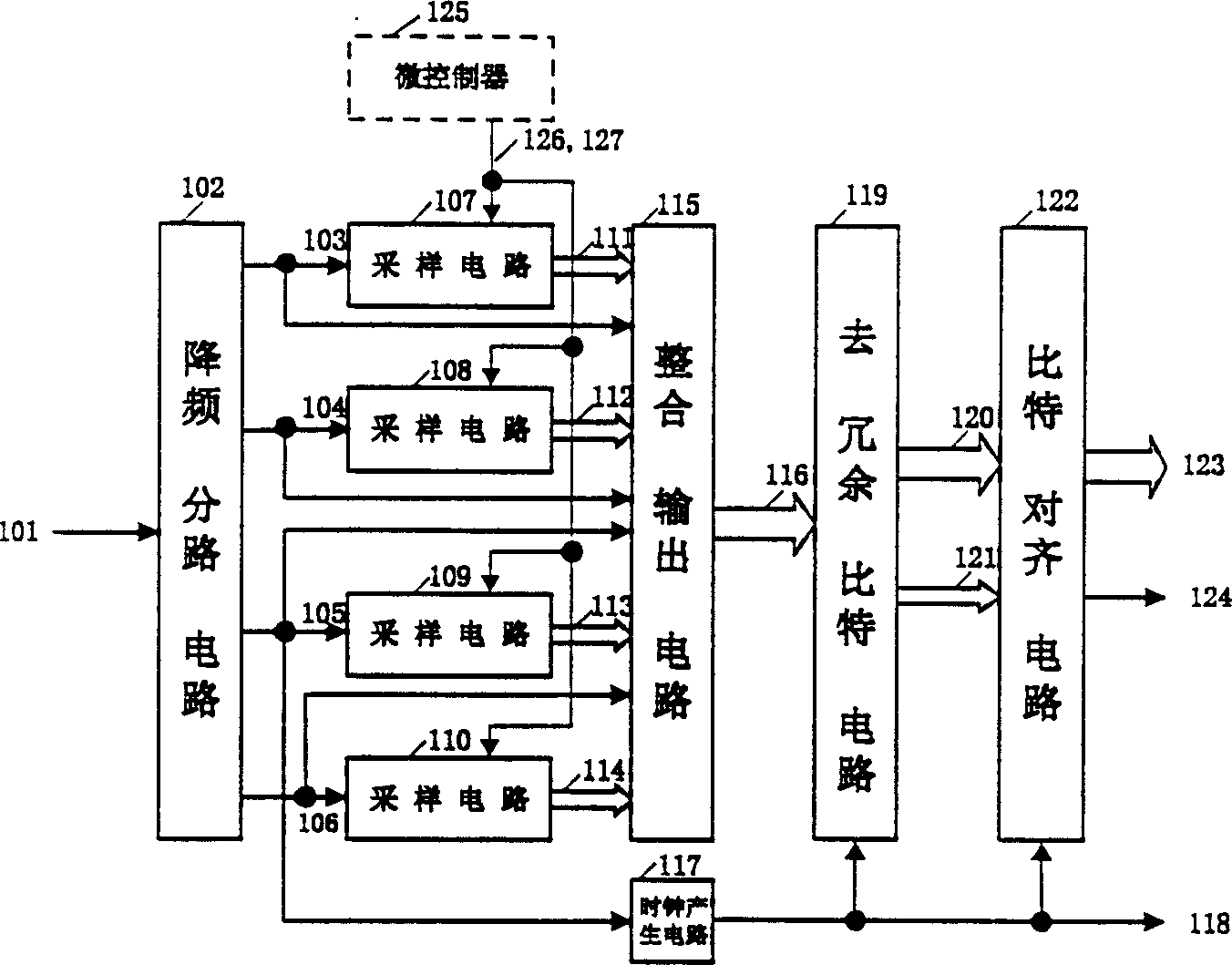

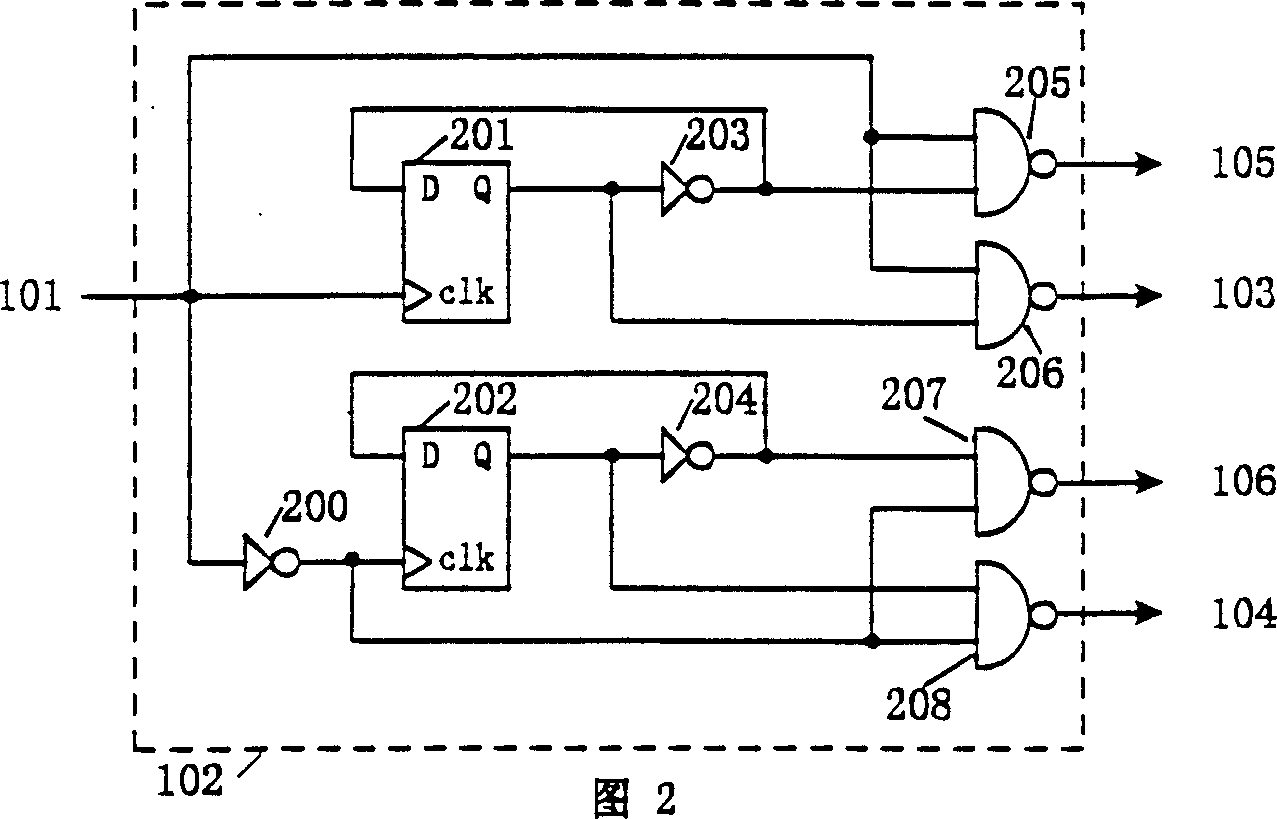

Method for high speed SATA interface data recovery and serial-parallel conversion and circuit module

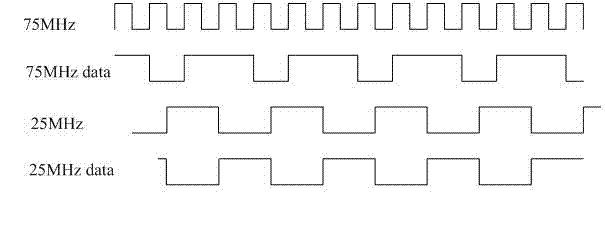

InactiveCN1622067AReduce power consumptionSimple design and manufactureGenerating/distributing signalsMicrocontrol arrangementsSerial lineComputer science

The high speed SATAn interface data restoring and serial-parallel conversion method includes the following steps: inputting high speed serial signal to obtain four ways of frequency-lowering shunt signal; sampling the four ways of frequency-reducing shunt signal separately; generating one clock signal from the serial line for subsequent sync circuit; outputting integrated sample signal in each clock period; eliminating excessive bits of the sample signal in each clock period and connecting effective bits to constitute bit sequence datan output; comparing the bit sequence datan and the sync word of the protocol for aligning bits and outputting effective protocol data. The circuit module based on the method includes frequency-reducing shunt circuit, successively connected four circuits of sample circuit, integrating output circuit, clock generator circuit and redundant bit eliminating circuit, as well as bit aligning circuit and micro controller.

Owner:BEIJING WEICHEN INFORMATION TECH

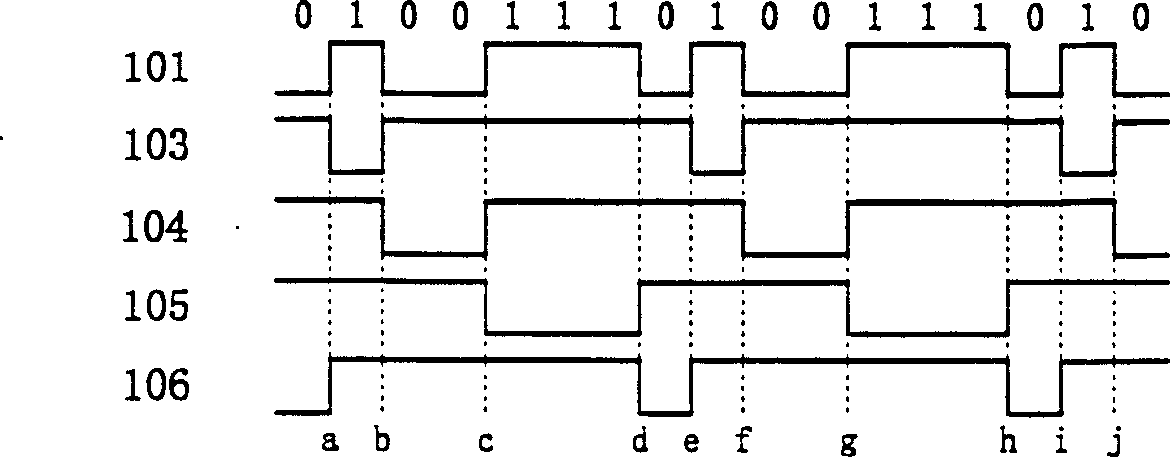

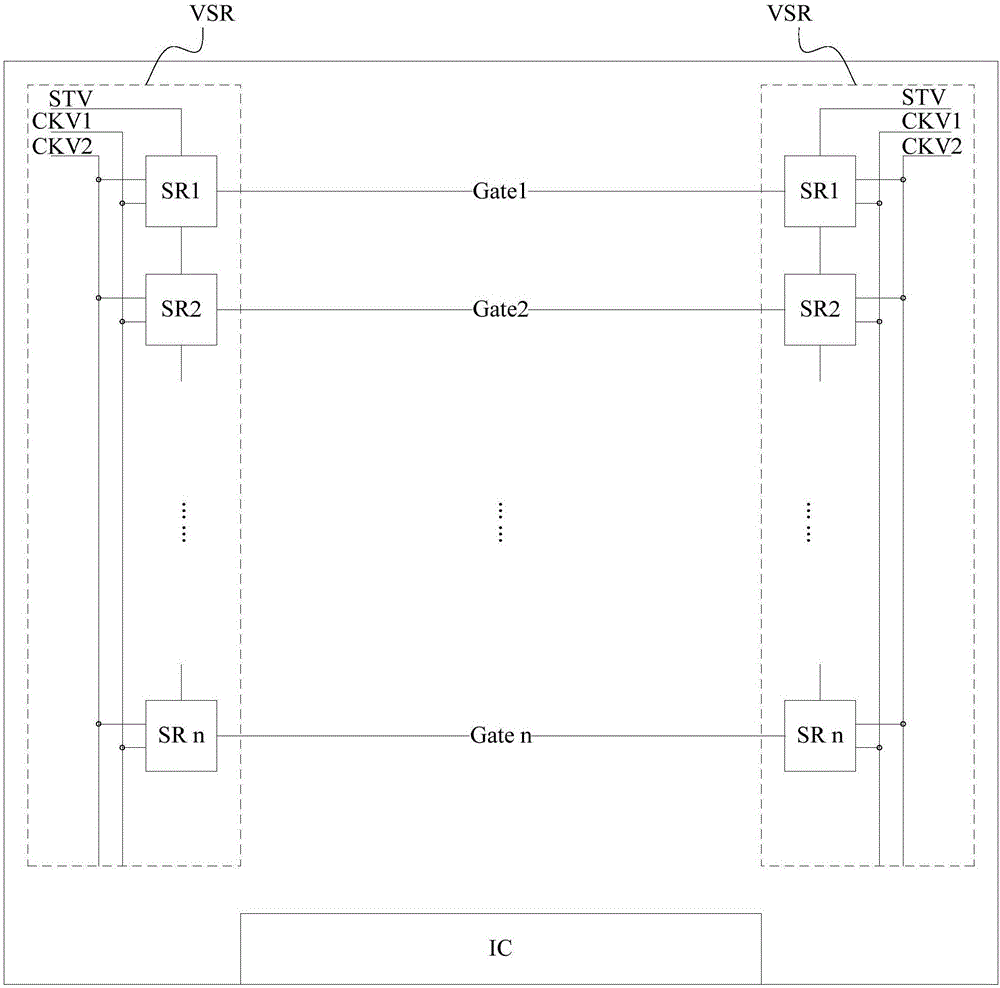

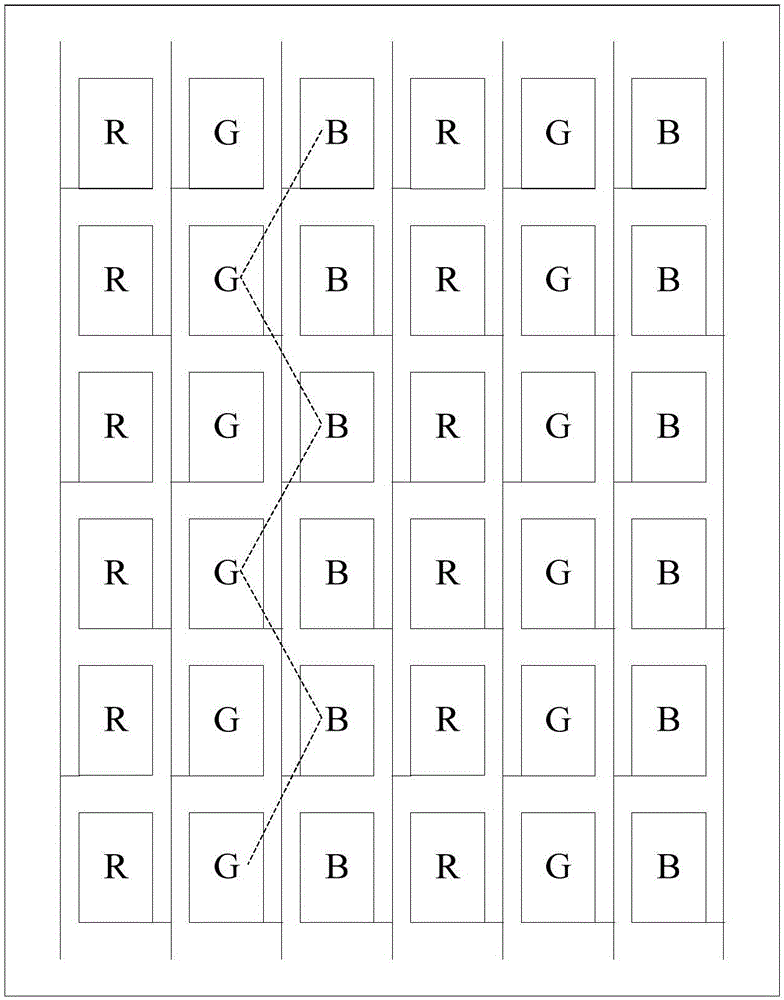

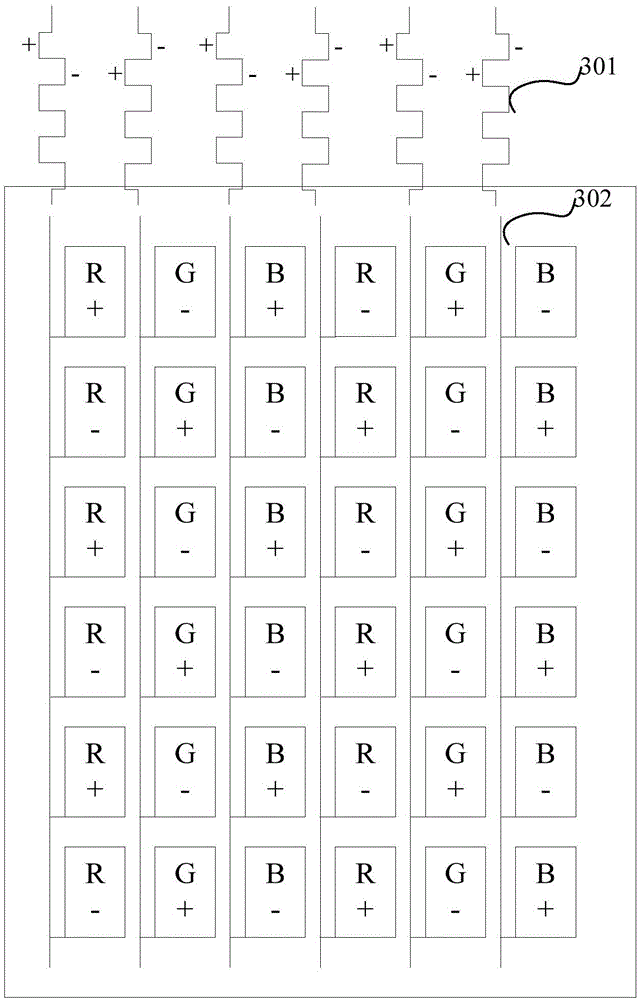

Display panel driving method and display panel

InactiveCN106652878AControl work statusNumber of realizationsStatic indicating devicesShift registerContinuous scanning

The invention discloses a display panel driving method and a display panel. The method comprises the following steps: grouping shifting registers in a grid driving circuit, setting different frame starting signal terminals and different clock control signal terminals for the groups of shifting registers so as to control the working states of the groups of shifting registers at different frame display times; at first display frequency, controlling all of the groups of shifting registers to work for one time according to the sequence of the groups of shifting registers within each frame of scanning time to display an image, and inputting column overturning display signals with lower power consumption to data lines at this time to realize a point overturning display effect; and at second display frequency subjected to frequency reduction compared with the first display frequency, scanning all grid lines for one time within multiple frames of continuous scanning times according to the frequency reduction fold and the number of the groups of shifting registers so as to display an image. The number of display signals located by the data lines within each frame of scanning time is reduced, the times of negative and positive polarity switch of the display signals are reduced, and the power consumption is reduced.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

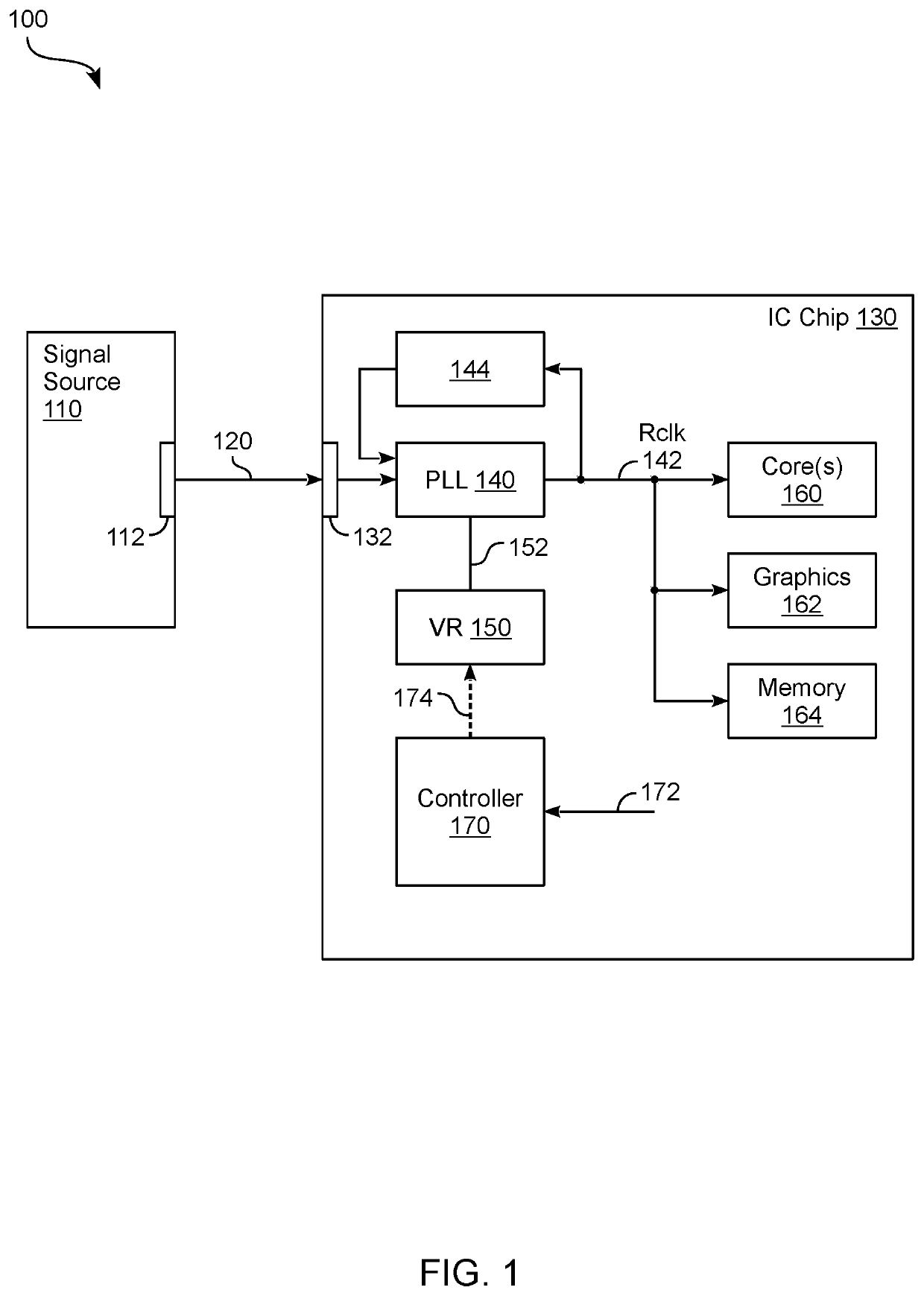

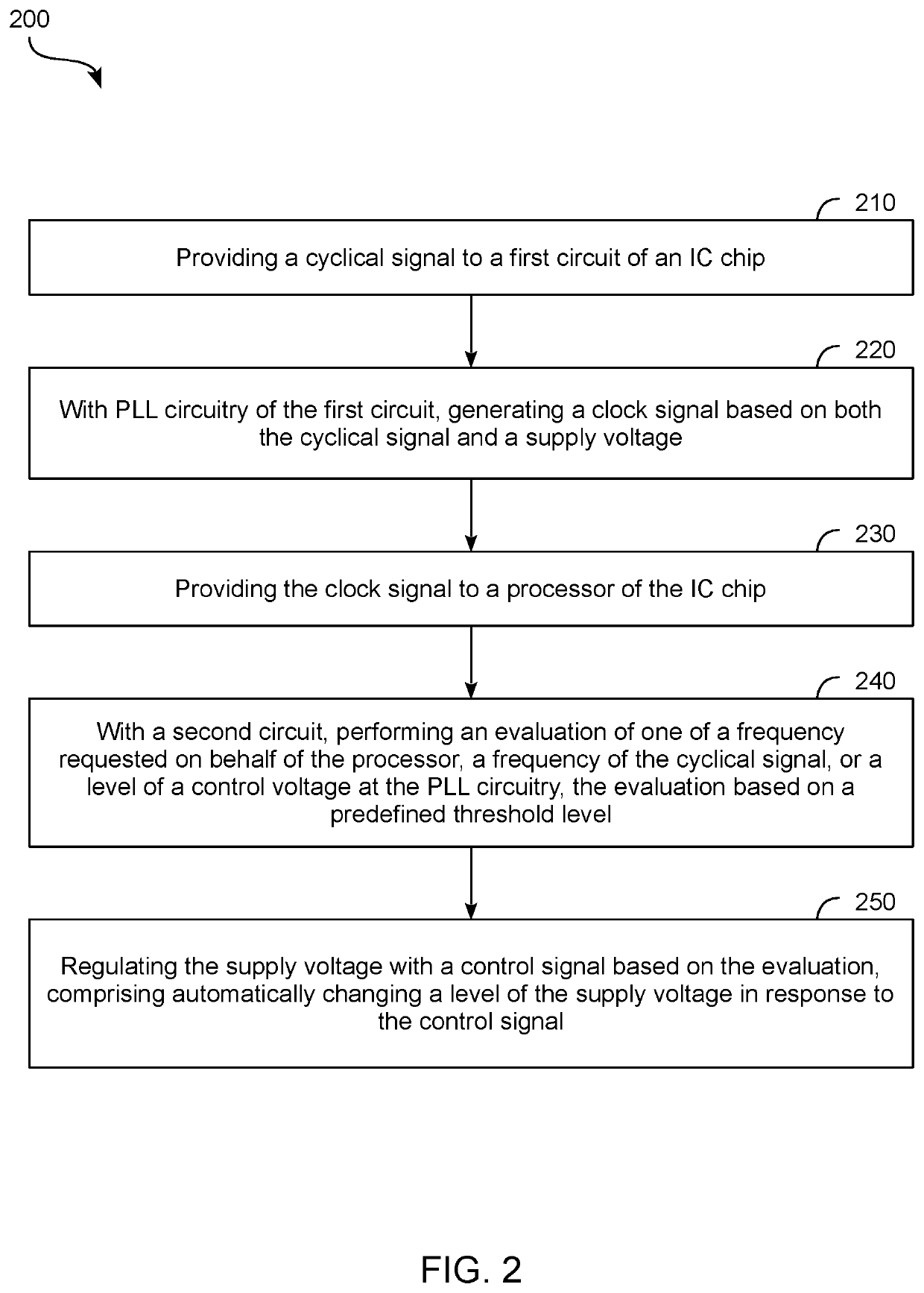

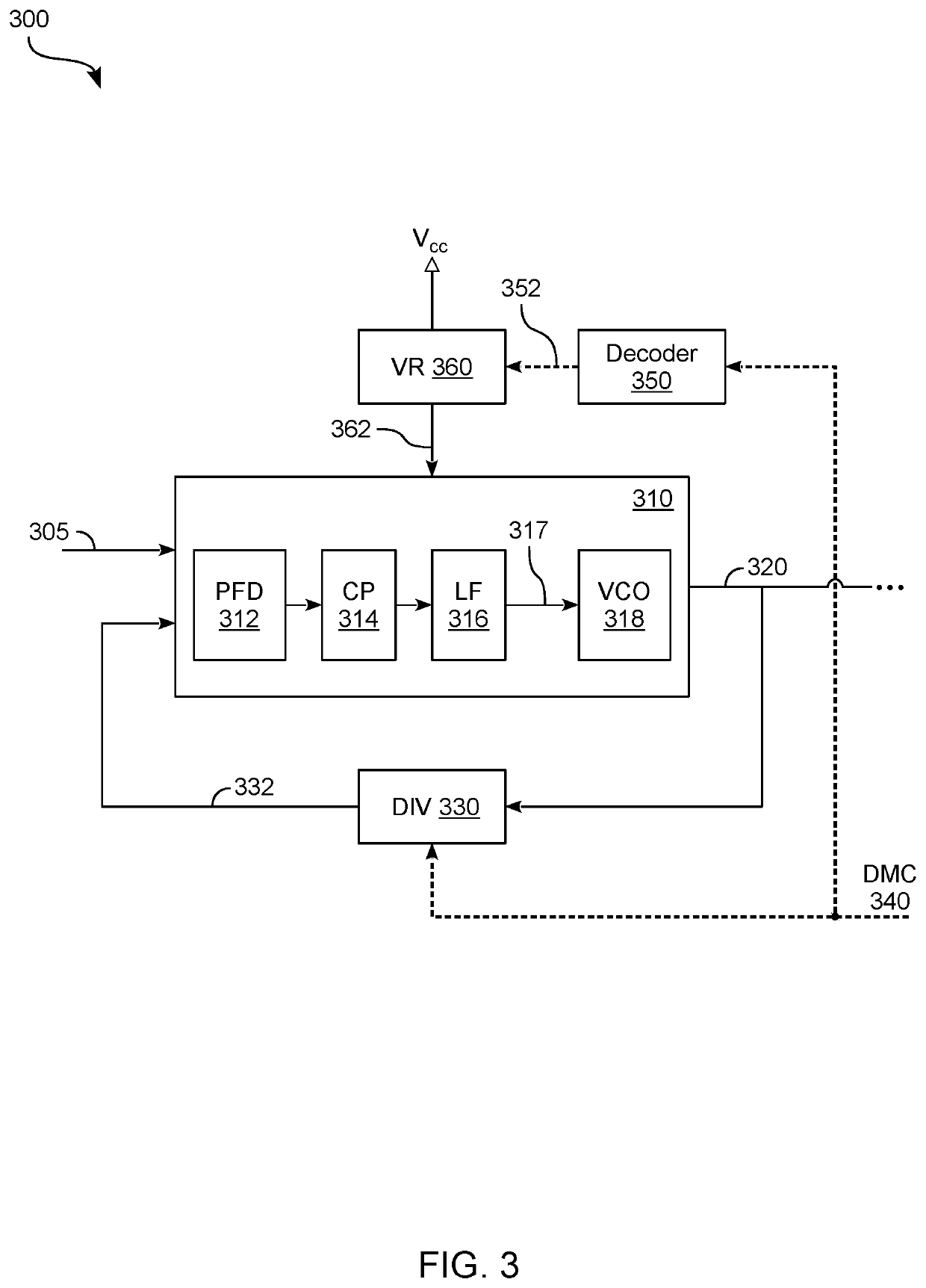

Device, method and system for on-chip generation of a reference clock signal

ActiveUS20200005728A1Pulse automatic controlVolume/mass flow measurementComputer architecturePhase locked loop circuit

Techniques and mechanisms for an integrated circuit (IC) chip to generate a clock signal for use by one or more resources of the IC chip. In an embodiment, a clock signal is generated with phase-locked loop (PLL) circuitry of an IC chip based on a cyclical signal which is provided to the IC chip by an external source. A supply voltage provided to the PLL circuitry is automatically updated based on one of a requested frequency for the clock signal, a frequency of the received cyclical signal, or a voltage of a control signal used by a voltage controlled oscillator of the PLL circuitry. In another embodiment, a series of incremental changes to a frequency of the clock signal is automatically performed according to a predefined overclocking scheme or underclocking scheme.

Owner:INTEL CORP

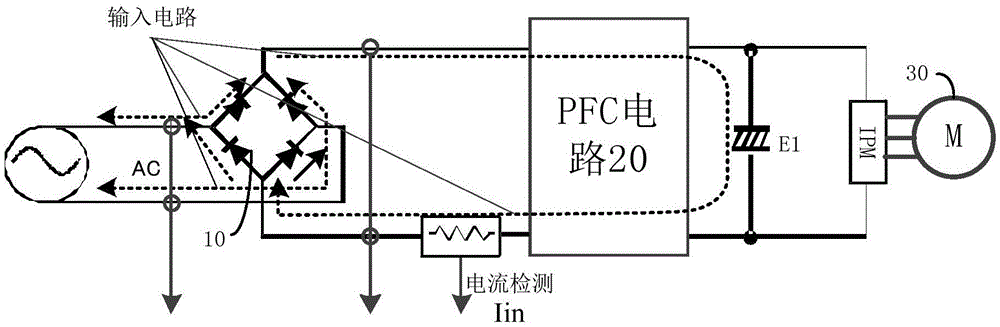

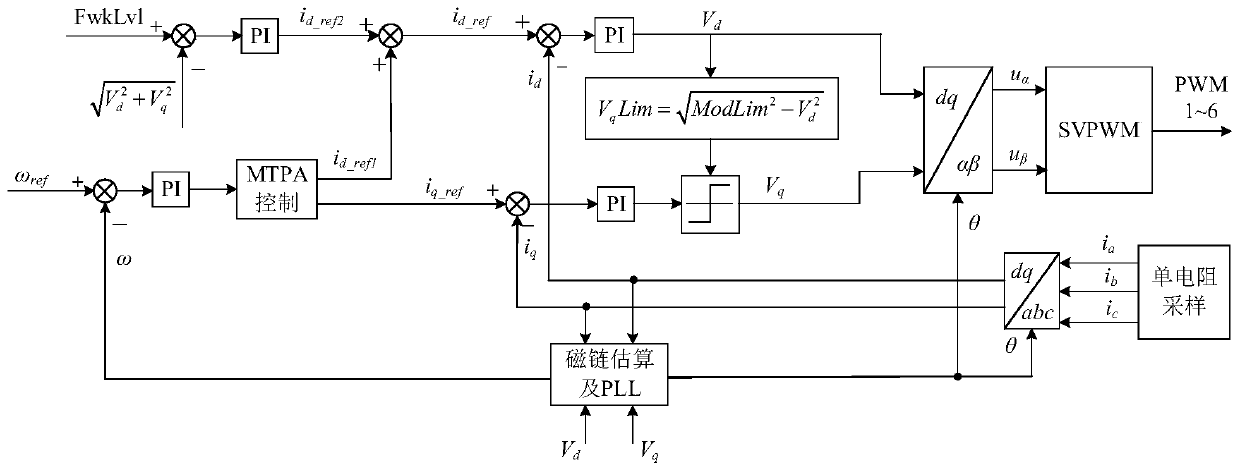

Air conditioner and compressor control method and device when supply voltage drops

ActiveCN104963846AGuaranteed uptimeReduce input currentSpace heating and ventilation safety systemsLighting and heating apparatusPower flowControl vector

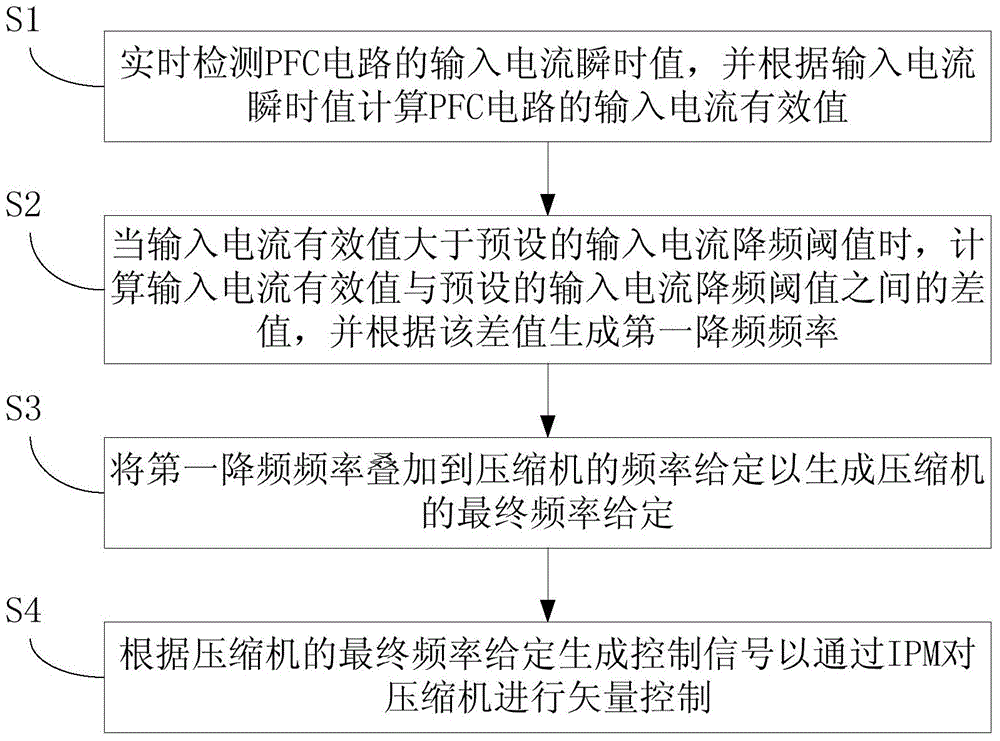

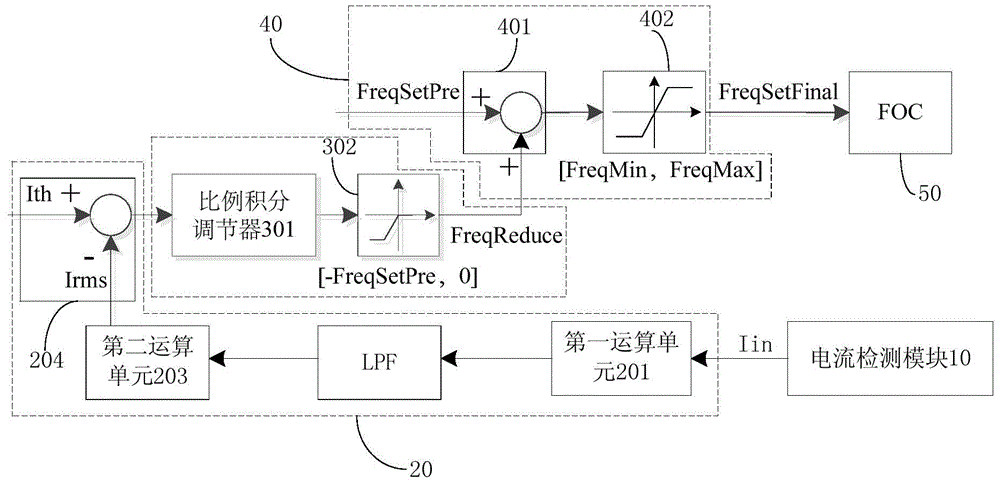

The invention discloses a compressor control method when supply voltage of an air conditioner drops; the method comprises the following steps: detecting an input current instantaneous value of a PFC circuit in real time, and calculating a PFC circuit input current effective value according to the input current instantaneous value; calculating a difference value between the input current effective value and a preset input current underclocking threshold if the input current effective value is bigger than the preset input current underclocking threshold, and generating a first underclocking frequency according to the difference value; adding the first underclocking frequency to a compressor given frequency so as to generate a compressor final given frequency; generating a control signal according to the compressor final given frequency, thus using an IPM to carry out vector control for the compressor. The control method can carry out underclocking control for the compressor if the input current of the PFC circuit is overlarge, thus reducing output power of the compressor, reducing the input current of the PFC circuit, and protecting the input circuit. The invention also discloses an air conditioner compressor control device, and the air conditioner.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD +1

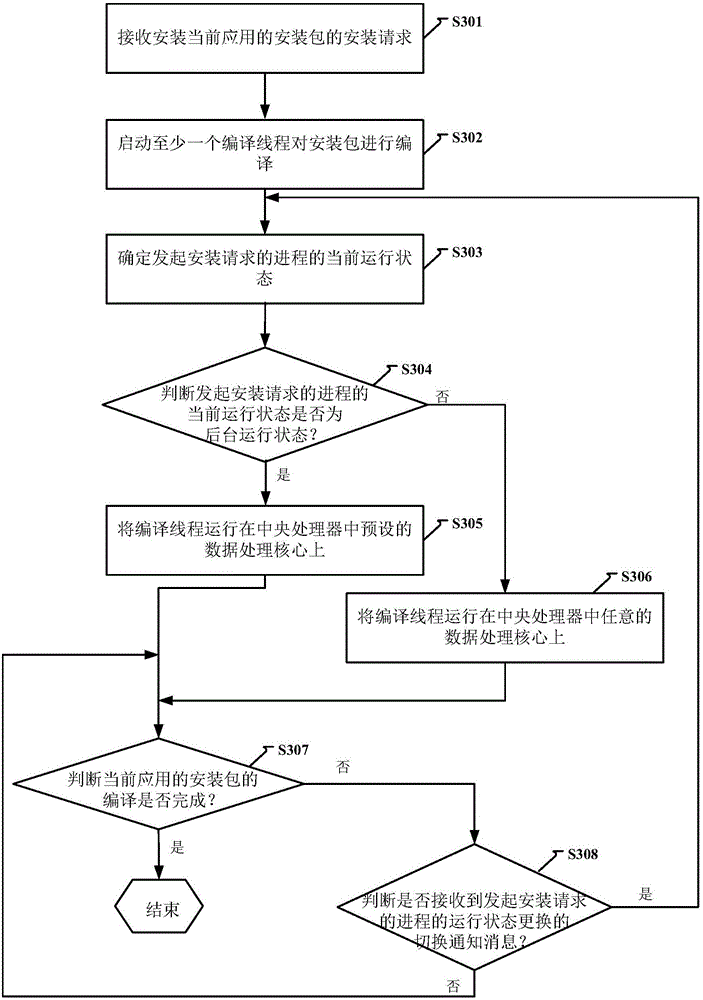

Application installation method and device

ActiveCN106020893ALess chance of throttlingReduce power consumptionProgram loading/initiatingSoftware deploymentEngineeringUnderclocking

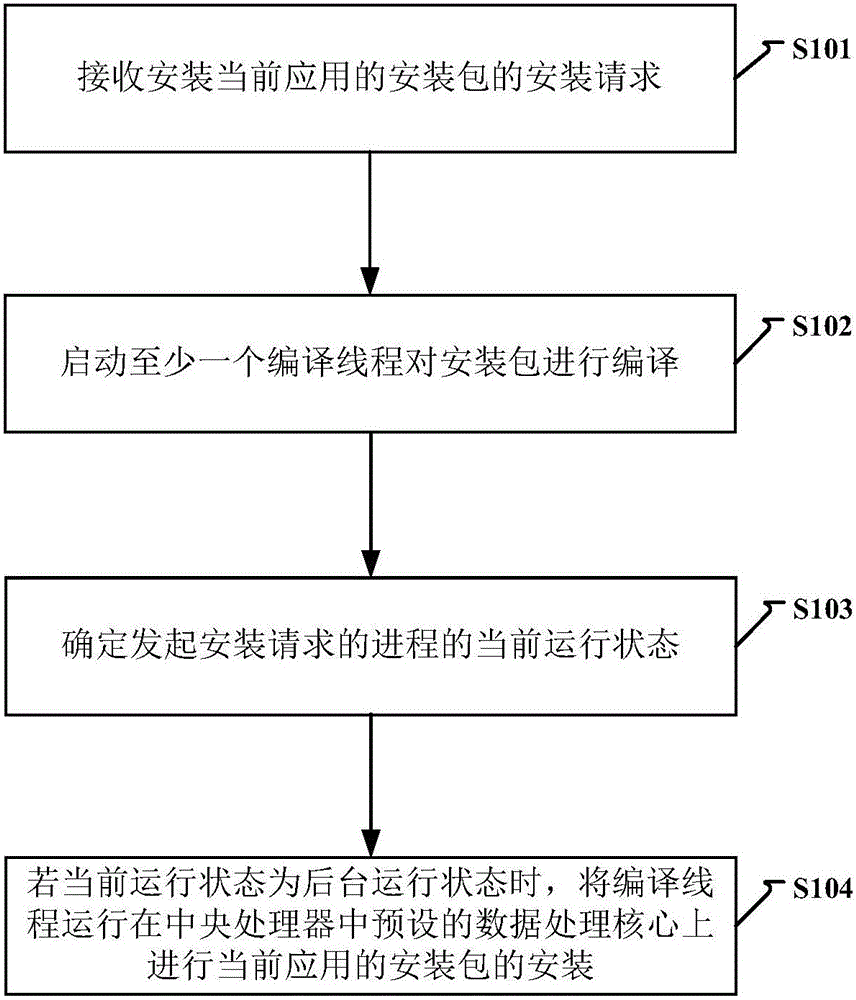

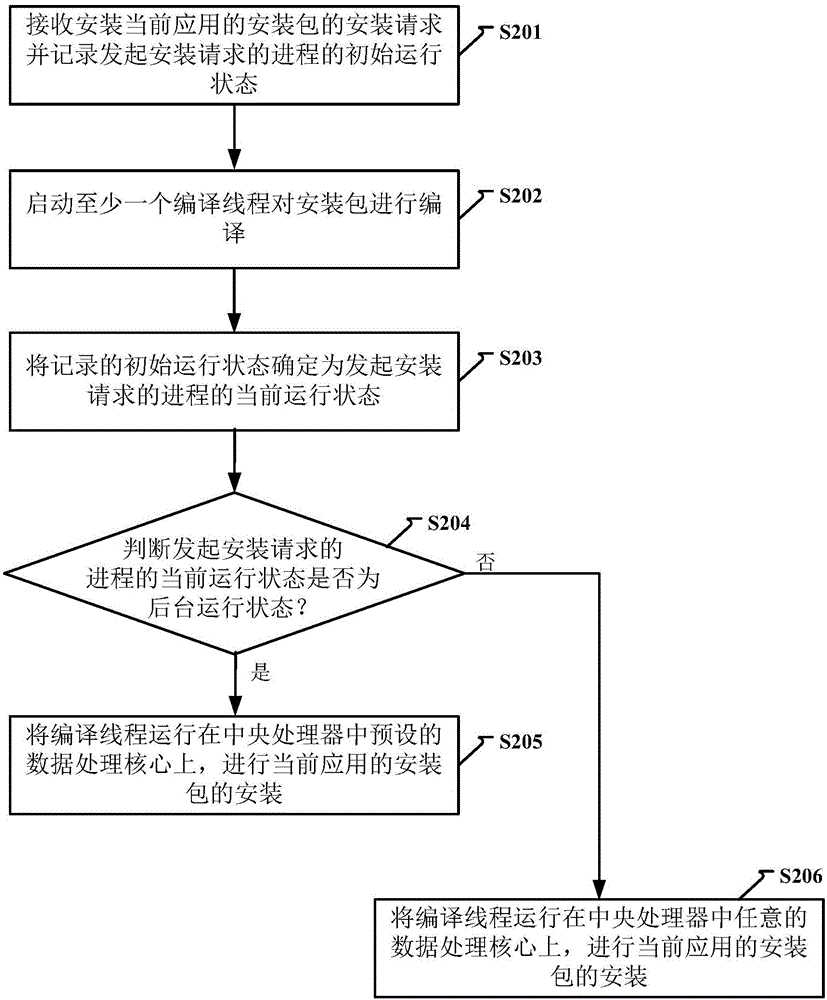

The invention relates to an application installation method and device. The method comprises the steps of receiving an installation request for installing an installation package of a current application; starting at least one compiling thread for compiling the installation package; determining the current operation status of the process initiating the installation package; if the current operation status is a background operation status, operating the compiling thread on a preset data processing core in a central processing unit, and installing the installation package of the current application. According to the technical scheme, when the process initiating the installation request is in the background operation status, a compiling thread for compiling the installation package of the application can be operated only on the data processing core preset in the central processing unit, in this way, resources of the central processing unit are reasonably distributed, and the probability that the compiling thread is operated on the data processing core which is high in power consumption and likely to emit heat is reduced, so that the probability of central processing underclocking caused by heating is reduced, and power consumption is further lowered.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

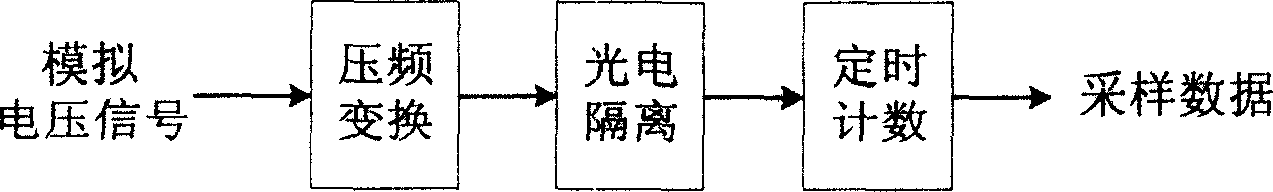

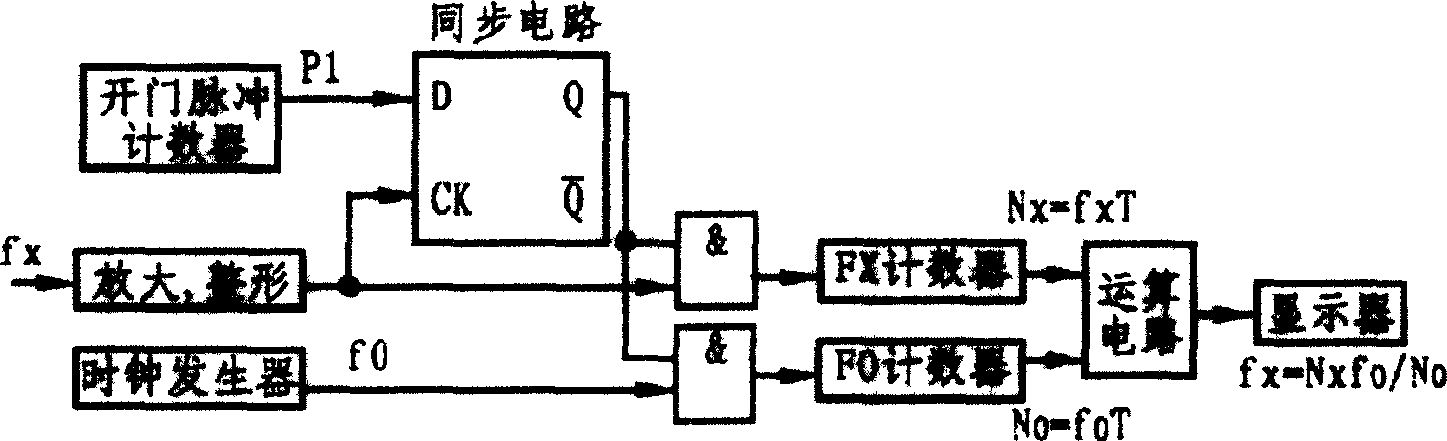

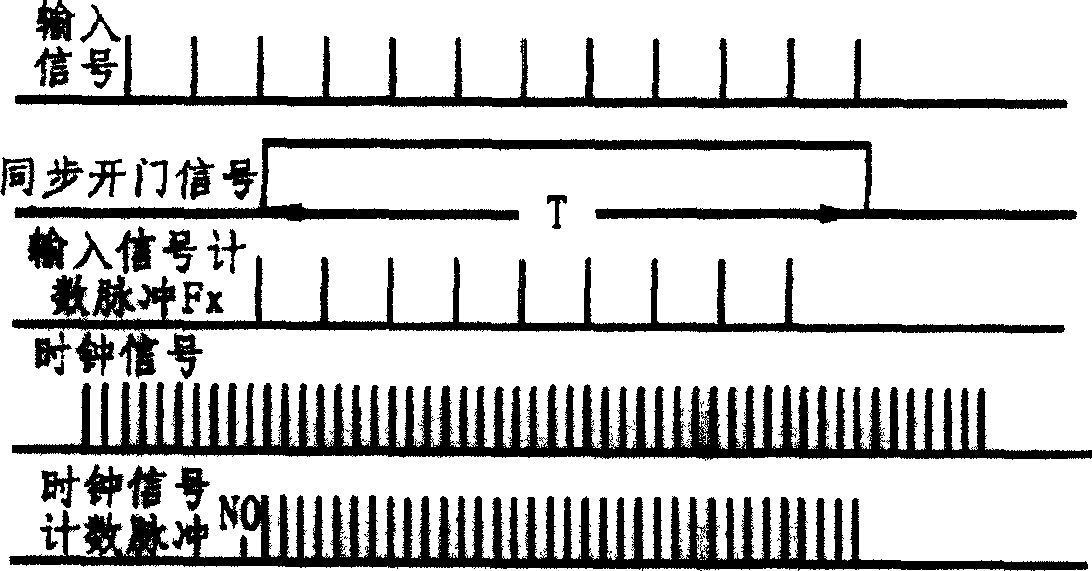

Digital analog converting method and system based on pressure-frequency conversion

InactiveCN1710622ANo distortionPhase shift does not affectElectric signal transmission systemsFrequency conversionWave form

Through voltage-frequency conversion, the method converts analog voltage to frequency of digital impulse signal linearly. Then, through opto-electronic isolation transmission, electronic jumping number of impulse signal is determined in continuous short time interval. Finally, through filtering and stepping-down frequency obtains A / D conversion of sampled data. The system is composed of voltage-frequency conversion circuit, opto-electronic isolation circuit, counting circuit, digital filtering and stepping-down frequency circuit, and data interface connected in series. Features are: isolated measurement of signal, raised precision of A / D conversion caused by first order oversampling characteristic utilized in counting process, and linear phase characteristic to ensure undistorted sampled wave form.

Owner:TSINGHUA UNIV

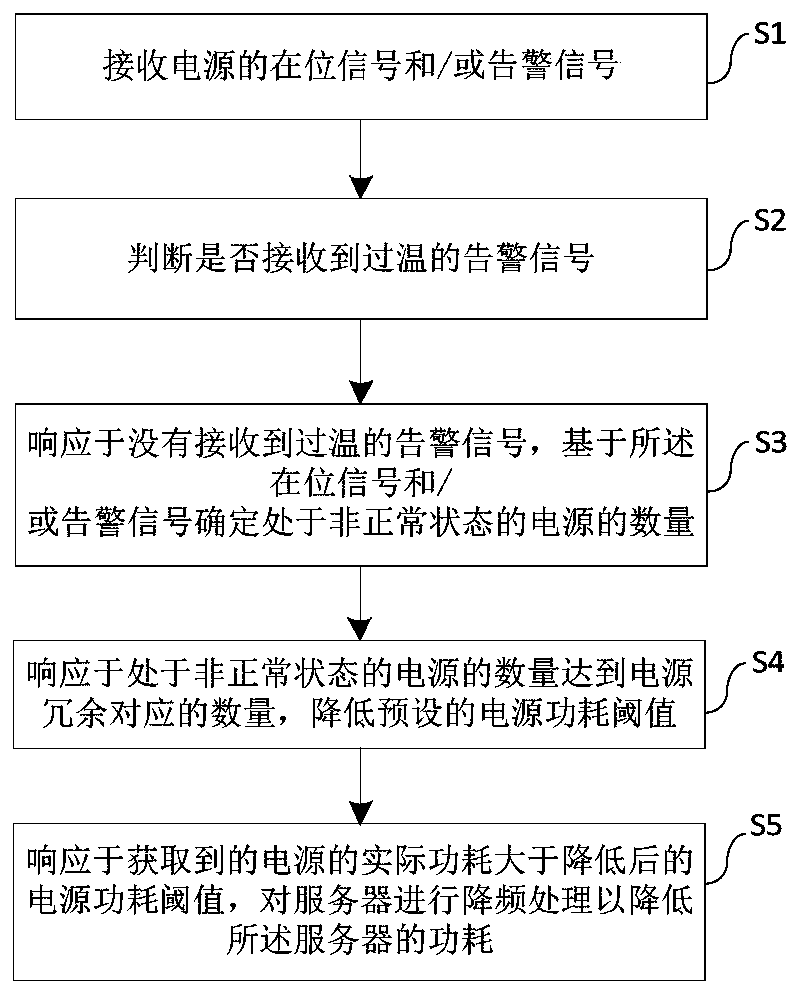

Server power consumption limiting method, system and device and medium

InactiveCN111352497AImprove performanceReduce usage impactDigital data processing detailsSignal responseUnderclocking

The invention discloses a server power consumption limiting method. The method comprises the following steps: receiving an in-place signal and / or an alarm signal of a power supply; judging whether anover-temperature alarm signal is received or not; determining the number of power supplies in an abnormal state based on the in-place signal and / or the alarm signal in response to the fact that the over-temperature alarm signal is not received; in response to the fact that the number of the power supplies in the abnormal state reaches the number corresponding to the power supply redundancy, reducing a preset power supply power consumption threshold value; in response to the fact that the obtained actual power consumption of the power supply is greater than the reduced power consumption threshold, performing frequency reduction processing on the server to reduce the power consumption of the server. The invention further discloses a system, computer equipment and a readable storage medium. According to the scheme provided by the invention, when the system power supply is abnormal but does not influence the power supply redundancy, or the power supply still can support partial power supply, the threshold value of the power supply power consumption limit is set more reasonably, so the performance of the server is as high as possible.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

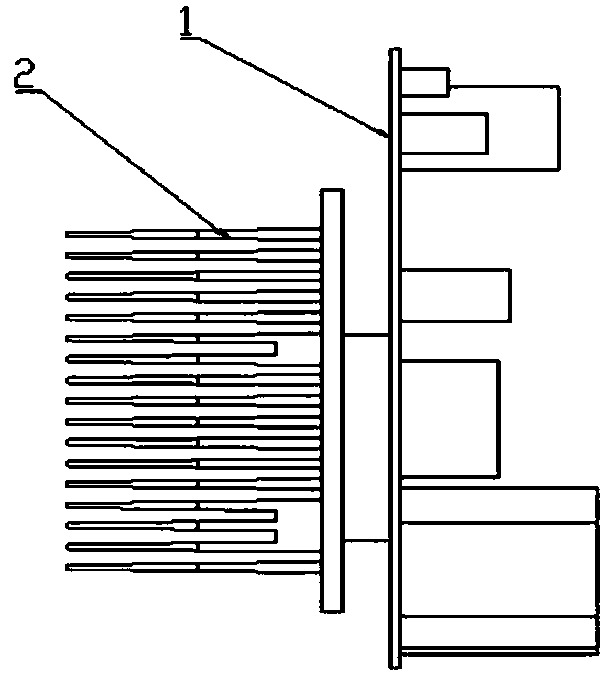

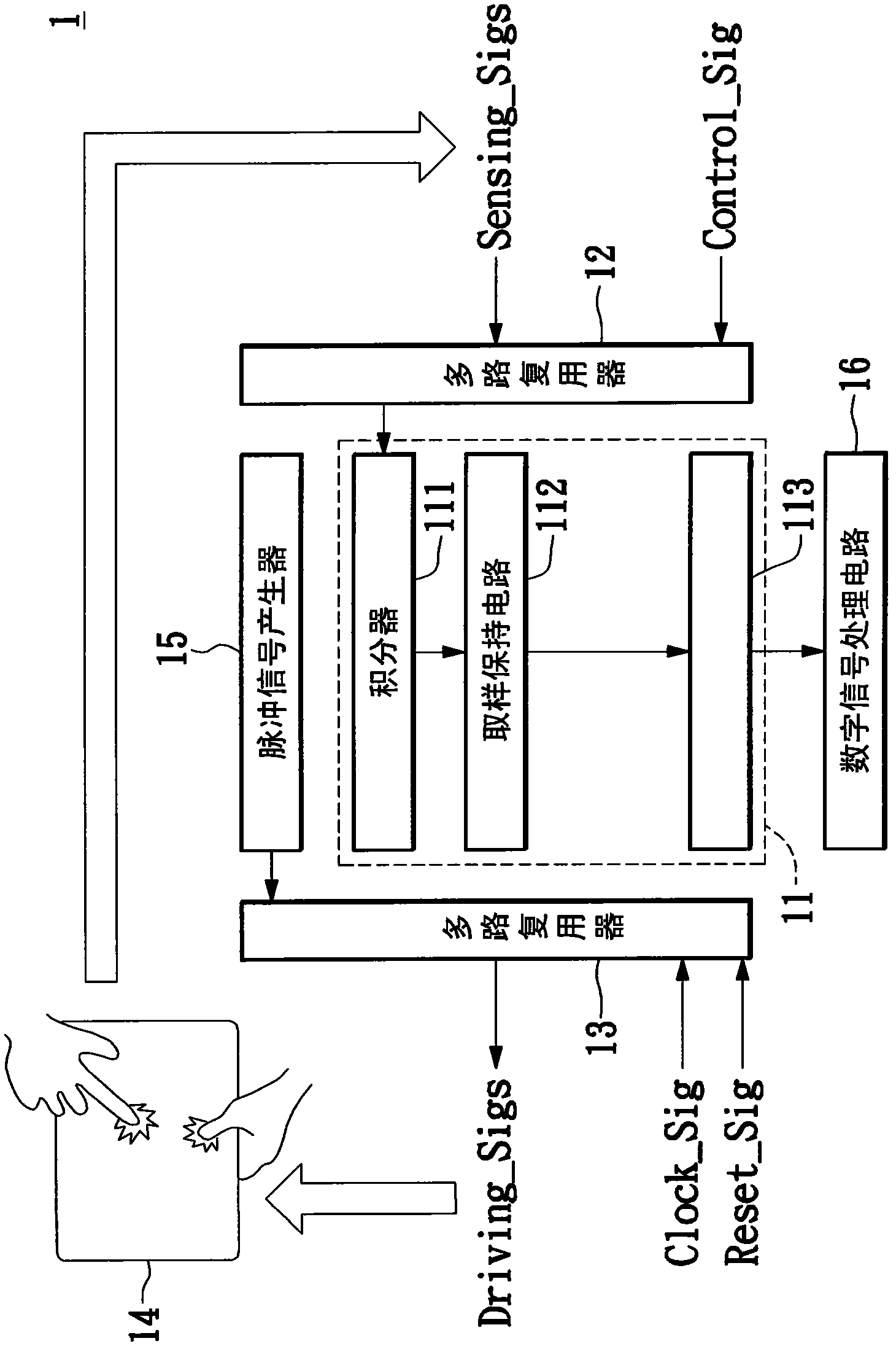

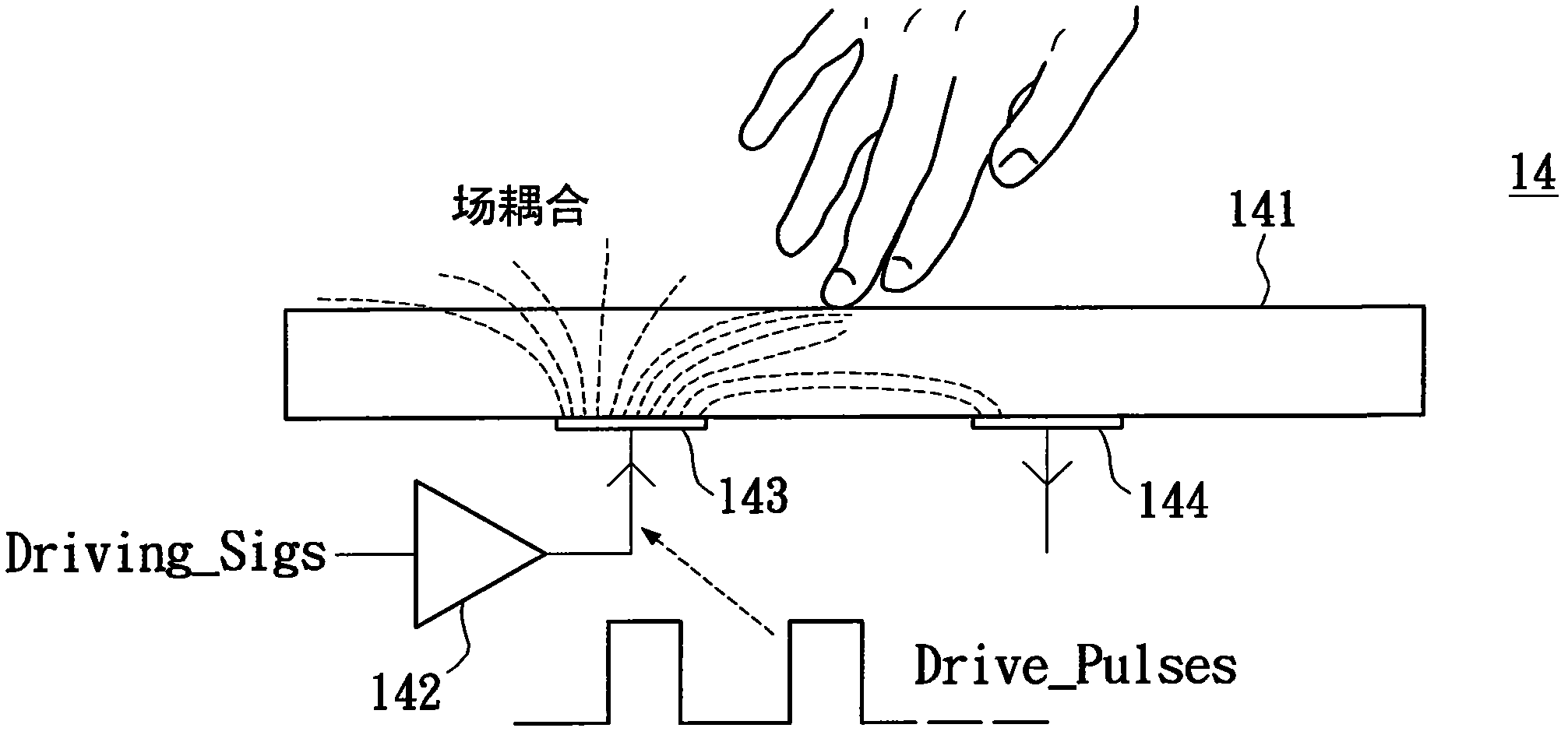

Sensing electrode array control circuit and control method and touch control sensing system thereof

ActiveCN102915138AImprove signal-to-noise ratioFast operationInput/output processes for data processingSignal-to-noise ratio (imaging)Electrode array

The invention discloses a sensing electrode array control circuit. The sensing electrode array control circuit comprises an underclocking circuit, an intensity / phase frequency converter and a phase frequency analysis unit, wherein the underclocking circuit is used for underclocking a sensing signal of each sensing line on a touch control panel to acquire a corresponding underclocking signal, the underclocking signal is a direct current signal, the intensity / phase frequency converter is used for generating a corresponding phase frequency signal according to the underlocking signal, at least one of frequency and a phase of each phase frequency signal is relevant to an electric level of the corresponding underclocking signal, and the phase frequency analysis unit is used for acquiring signal quantity of the corresponding sensing line according to each phase frequency signal. Therefore, by the sensing electrode array control circuit, the operation speed and the signal-to-noise ratio of a touch control sensing system can be increased and improved on the premise of unnecessarily increasing manufacturing cost. The invention also provides a sensing electrode array control method and the touch control sensing system.

Owner:TRENDON TOUCH TECHNOLOGY CORPORATION

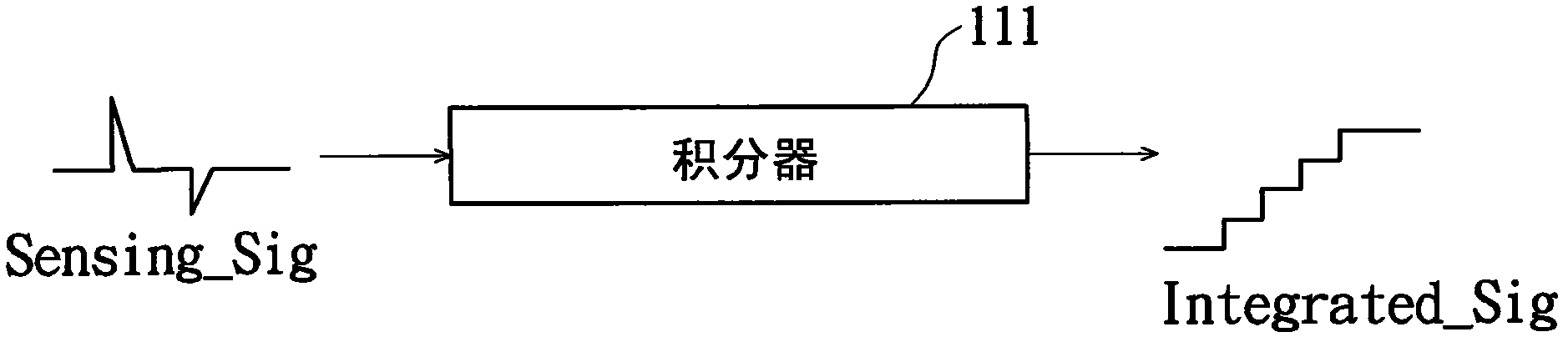

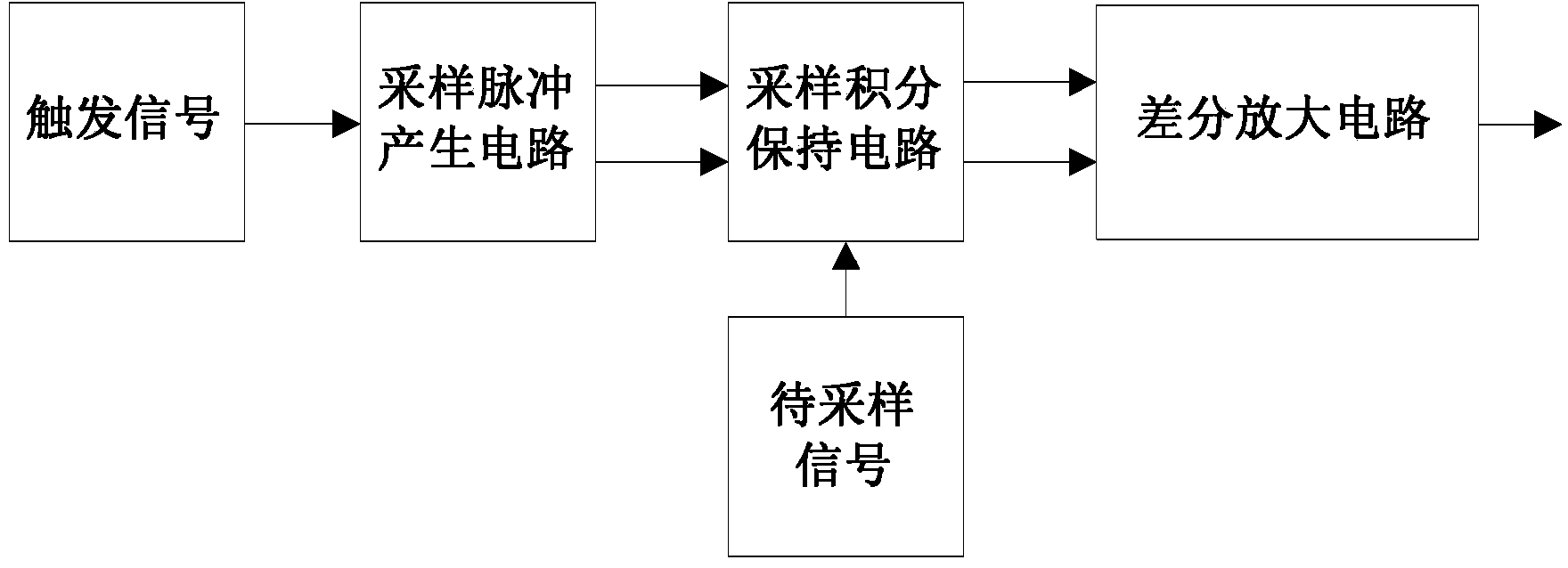

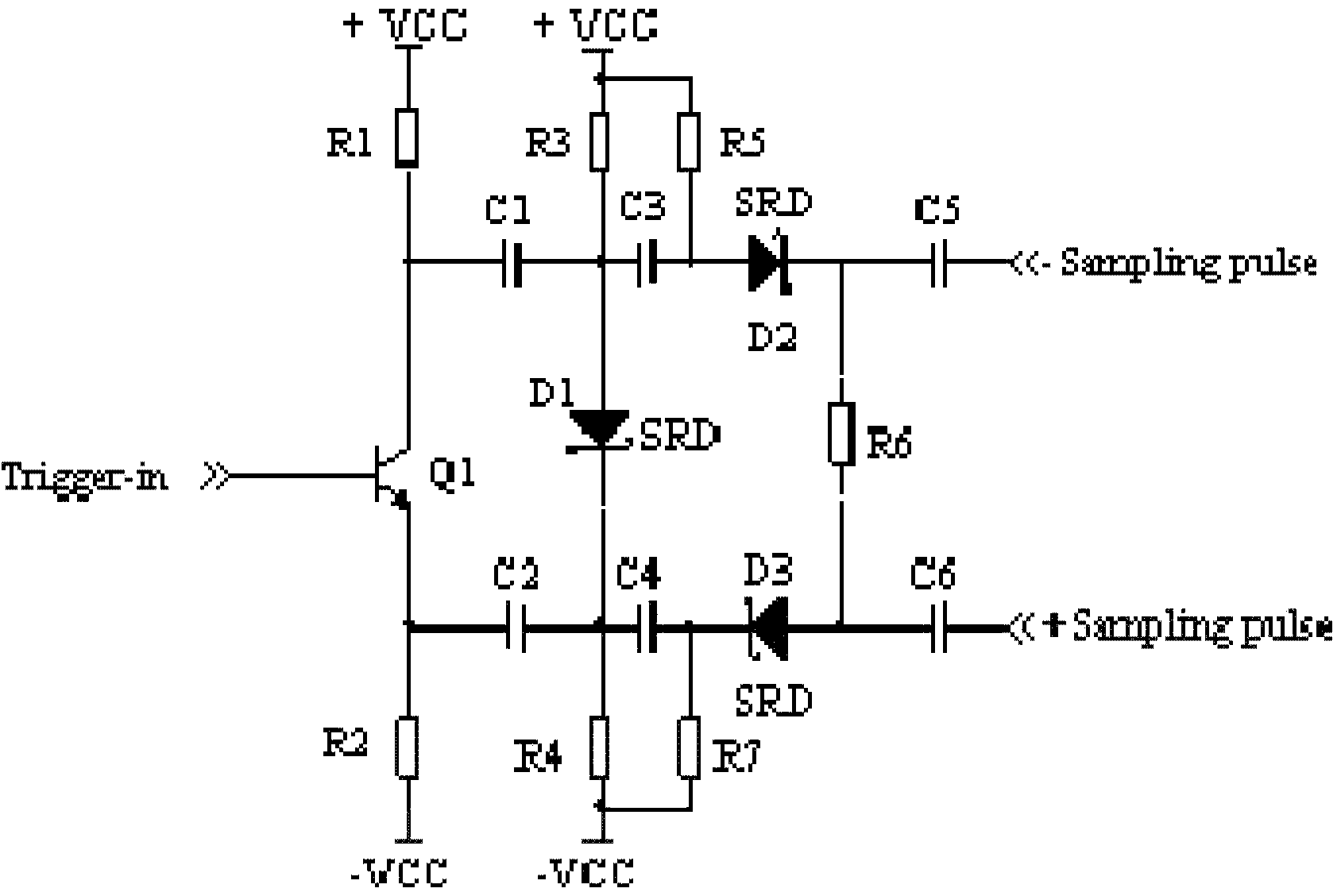

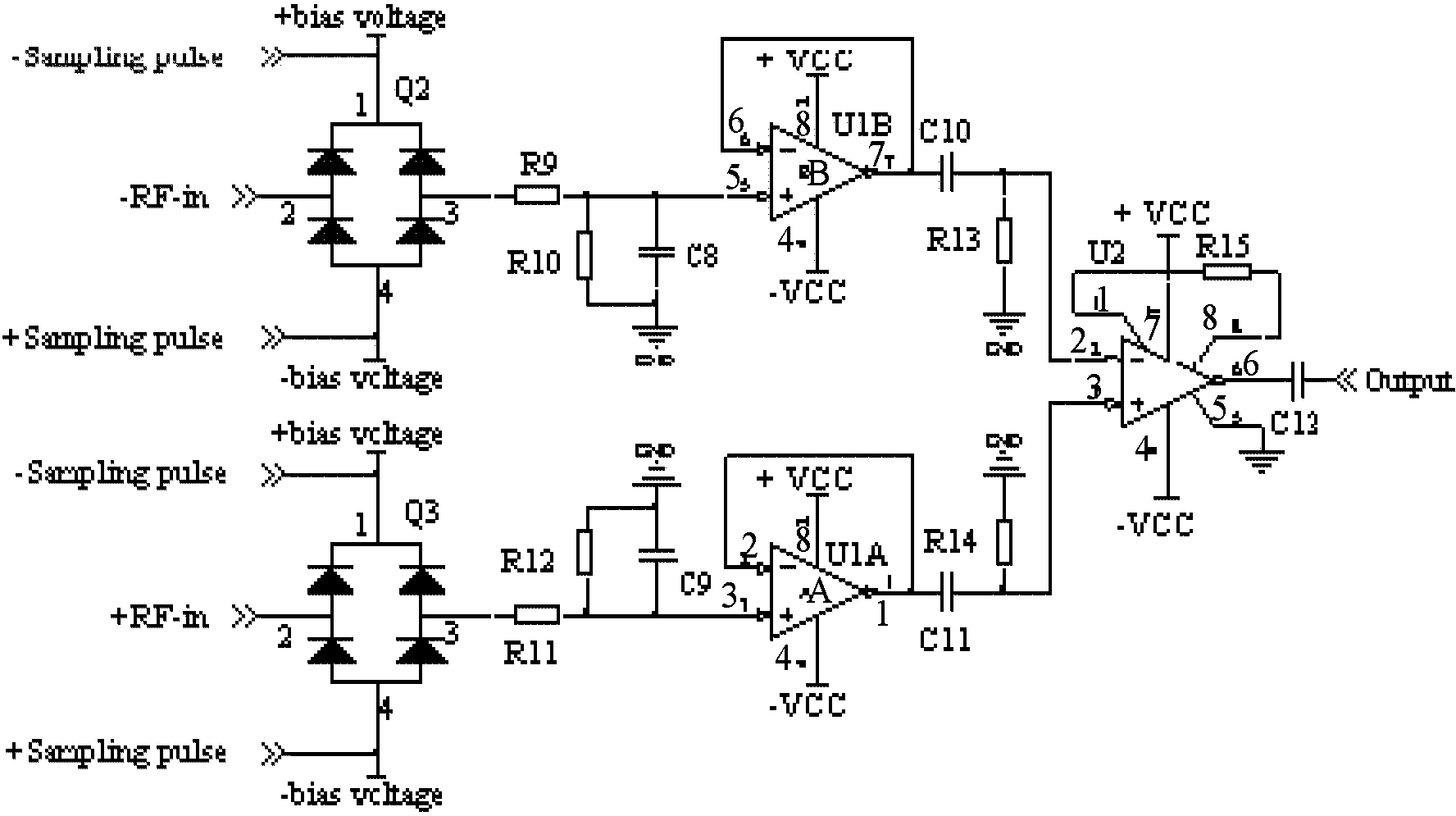

Balance feed sampling receiver

ActiveCN103926568AReduce performance requirementsImprove performanceWave based measurement systemsTime domainRadar systems

The invention provides a balance feed sampling receiver. The balance feed sampling receiver comprises a sampling pulse signal generating circuit, a sample integral retaining circuit and a differential amplification circuit, wherein the sampling pulse signal generating circuit is used for shaping a double-end drive pulse signal to generate a pair of balanced picosecond sampling pulse signals, the front end of the sample integral retaining circuit is electrically connected to the sampling pulse signal generating circuit and the input end of a pulse signal to be sampled, the sample integral retaining circuit is used for carrying out downsampling on the pulse signal to be sampled through the balanced picosecond sampling pulse signals and carrying out underclocking and reconstructing on the base band waveform of the pulse signal to be sampled, the front end of the differential amplification circuit is electrically connected to the sampling integral retaining circuit, and the differential amplification circuit is used for carrying out differential amplification processing on the base band waveform of the reconstructed pulse signal to be sampled and obtaining a low-frequency base band signal widened in the time domain. The balance feed sampling receiver can integrally reconstruct the pulse signal to be sampled, the sampling bandwidth is high and adjustable, and the application requirement of an ultra wide band radar system is met.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

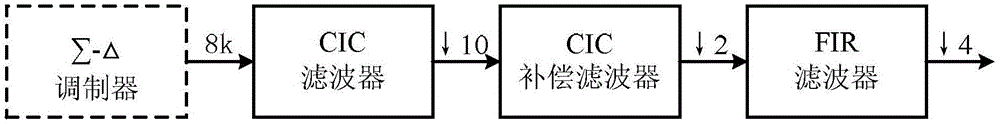

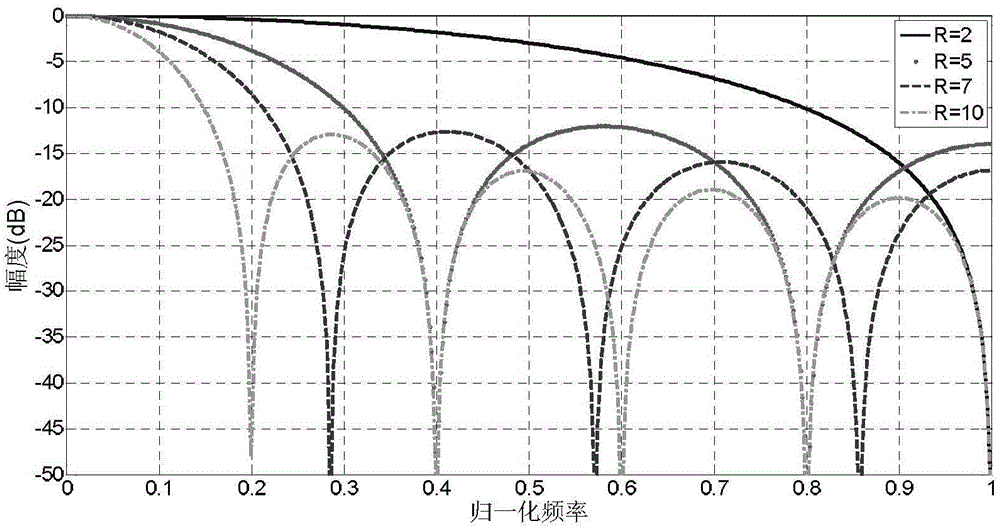

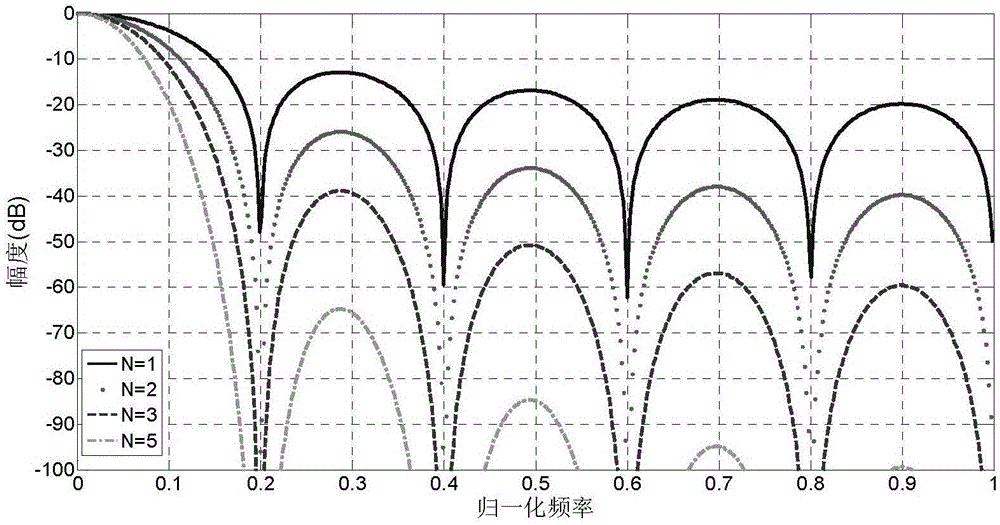

High-precision digital filter applicable to strapdown inertial navigation

InactiveCN105066990AHigh precisionHigh speed acquisitionNavigation by speed/acceleration measurementsMulti bandIntegrator

The invention discloses a high-precision acceleration DAC (digital-to-analogue conversion) digital filter applicable to strapdown inertial navigation and relates to the field of data acquisition. The filter comprises a sampling comb filter, an FIR double-extraction compensation filter and an FIR quadruple-extraction compensation filter, wherein the sampling comb filter adopts an efficient down-sampling filter structure put forward by Hogenauer and is used for realizing high-rate underclocking; the FIR double-extraction compensation filter is generated through a fir2 function in the matlab, the function can design a multi-band random response curve phase FIR filter, the filter is mainly used for compensating the pre-stage CIC (cascaded integrator comb) filter with attenuation on band margins and realizing double extraction; the FIR quadruple-extraction compensation filter calculates coefficients of the optimal filter with the Parks-McClellan algorithm, and the filter is low in pass band ripple, narrow in transition band, large in stop band attenuation and high in filter order. The high-precision digital filter meets the strapdown inertial navigation system data sampling requirement.

Owner:HARBIN ENG UNIV

Power consumption control method of electronic equipment and electronic equipment

PendingCN111522425AReduce power consumptionControl system power consumptionDigital data processing detailsUnderclockingReliability engineering

The invention provides a power consumption control method of electronic equipment, and the electronic equipment. The power consumption control method comprises the steps that the electronic equipmentcollects actual power consumption of at least one system-on-chip and actual power consumption of peripheral devices in a first time period, and then calculates the actual total power consumption of the electronic equipment in the first time period. Since the actual total power consumption in the first time period is equal to the sum of the actual power consumption of the system-on-chip and the actual power consumption of the peripheral devices in the first time period, when the electronic equipment determines that the actual total power consumption of the first time period is greater than or equal to a first power consumption threshold, the power consumption of all or part of the peripheral devices is reduced, so that the overall power consumption of the electronic equipment can be reducedunder the condition of not lowering the frequency of the processor, the system performance is ensured, and the power consumption control can be realized.

Owner:HUAWEI TECH CO LTD

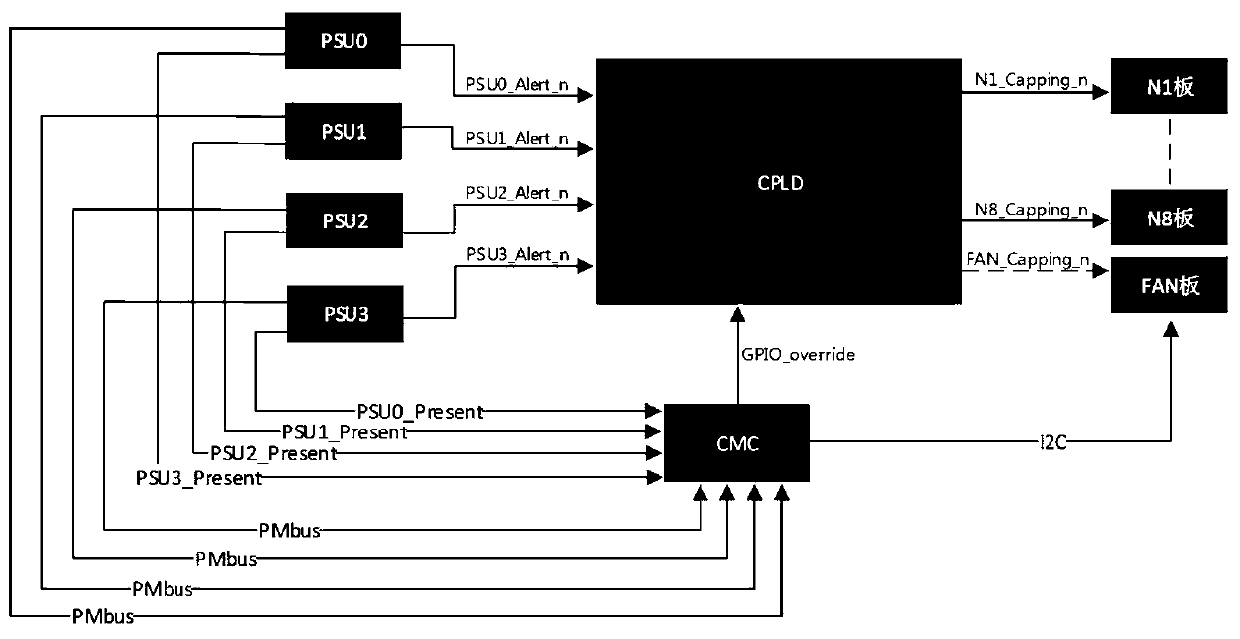

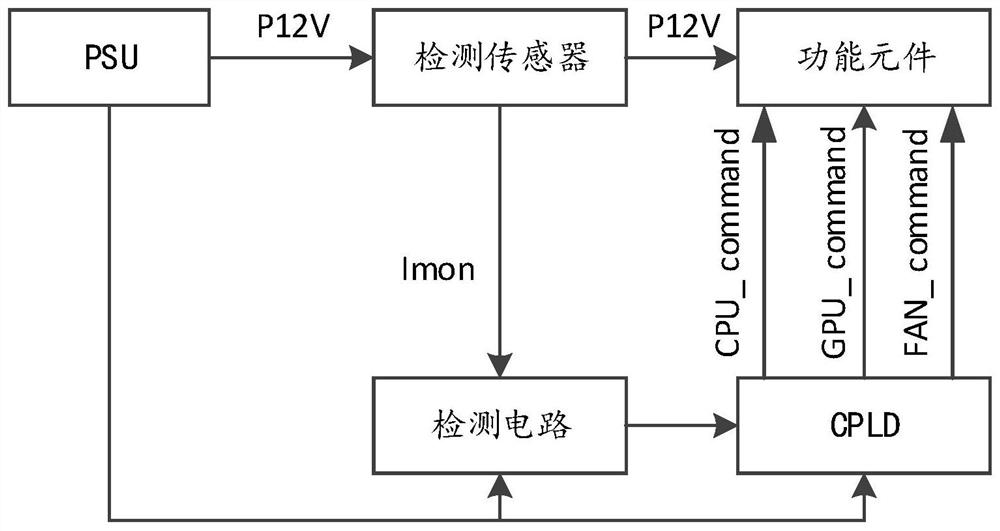

Electronic equipment and power consumption control method

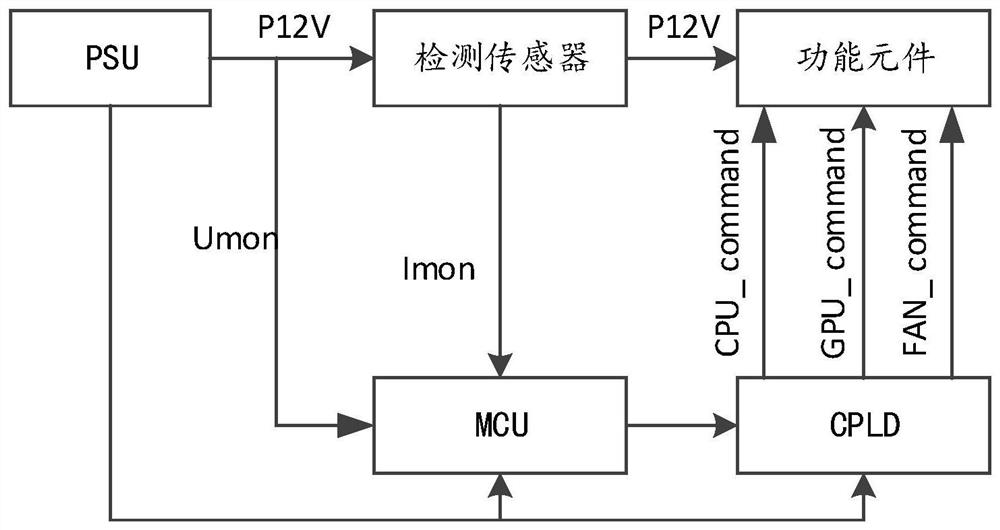

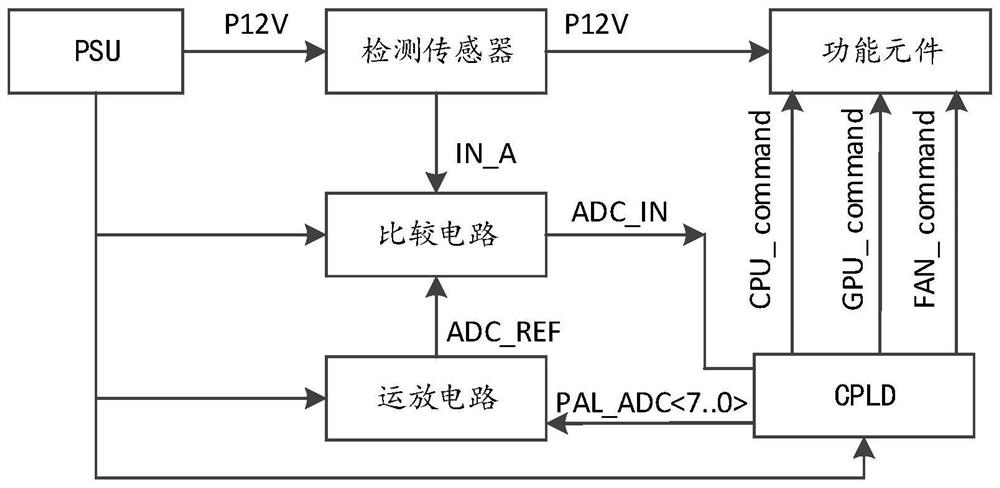

PendingCN113157076AGuaranteed processing speedLow costHardware monitoringPower supply for data processingComputer hardwareControl signal

The invention relates to electronic equipment and a power consumption control method, and belongs to the technical field of computers. The electronic device comprises a detection sensor, a monitoring circuit, a PSU and a CPLD. The detection sensor is used for detecting the output current of the PSU for supplying power to the electronic equipment; the monitoring circuit is connected with the detection sensor, and the monitoring circuit is used for generating a control signal according to the output current and a preset rule; and the CPLD is connected with the monitoring circuit, and the CPLD is used for carrying out frequency reduction processing on functional elements installed on the electronic equipment according to the control signal. The control signal is generated by detecting the output current of the PSU and combining the preset rule, the CPLD is used for carrying out frequency reduction processing on the functional element installed on the electronic equipment, and power adjustment is directly carried out through CPLD hardware instead of BMC software, so that the processing time required by power consumption adjustment can be shortened.

Owner:中科可控信息产业有限公司

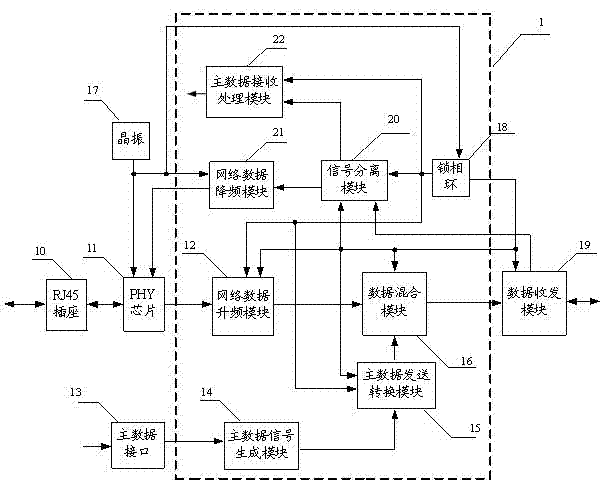

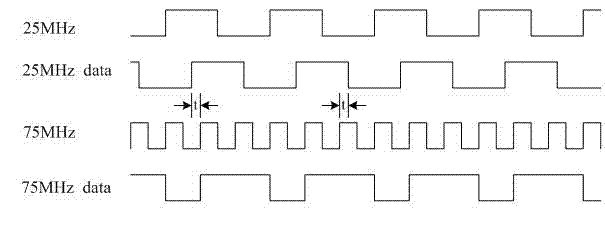

Video transmission device with surfing function and implementation method thereof

ActiveCN102740128AImprove performanceReduce spendingSelective content distributionVideo transmissionMedia Independent Interface

The invention discloses a video transmission device with a surfing function and an implementation method of the video transmission device, which can achieve the surfing function of remote display equipment. The video transmission device comprises an RJ45 socket, a PHY (Physical Layer) chip, a data processing module, a data receiving-transmitting module, a crystal oscillator, and a main data interface, wherein the crystal oscillator is connected with the PHY chip and the data processing module; and the main data interface is connected with the data processing module. According to the device and method, the data processing module converts a 100M RGMII (Reduced Gigabit Media Independent Interface) network signal and a video input signal into a high-frequency 2.5-bit network signal and a high-frequency 13.5-bit video signal respectively, and the high-frequency 2.5-bit network signal and the high-frequency 13.5-bit video signal are subjected to hybrid coding based on a certain format so as to form a continuous 16-bit even and odd field data frame; and the 16-bit even and odd field data frame is output through the data receiving-transmitting module; and meanwhile, the data processing module reversely processes the receiving data from the data receiving-transmitting module by decoding, separating and reducing the frequency, so as to complete duplex communication, therefore, the video display and web-surfing function can be achieved, and the performance of the video display control and monitoring system is improved.

Owner:深圳康佳控股集团有限公司

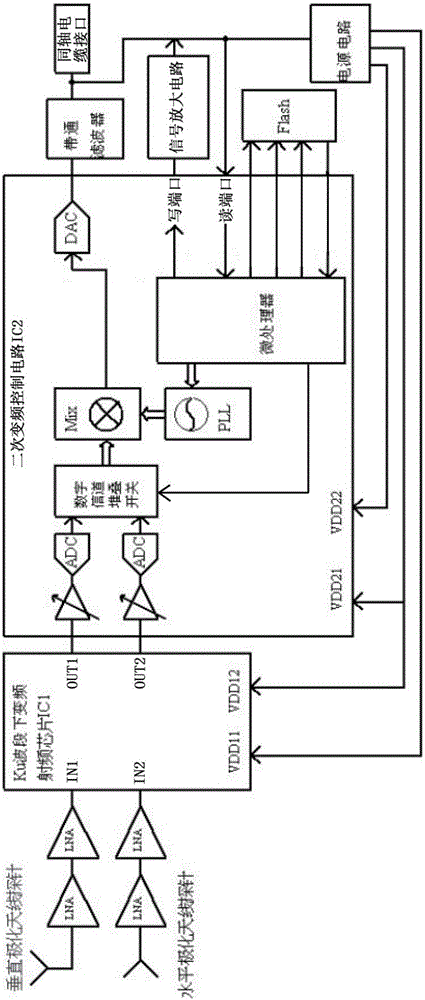

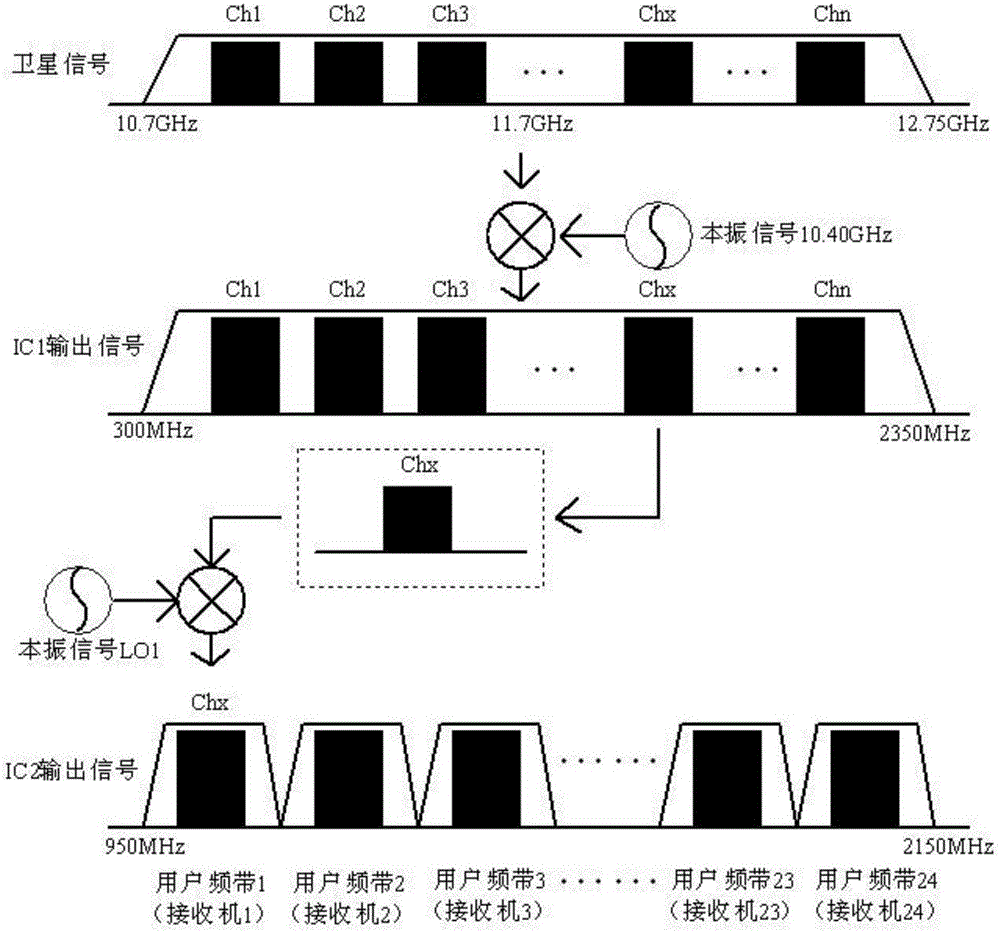

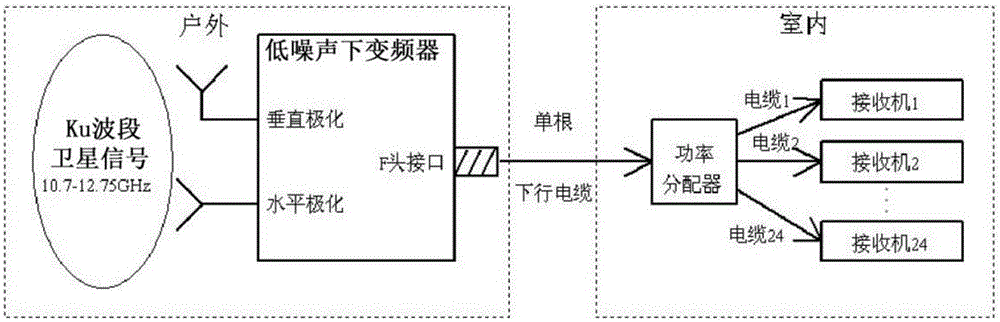

Low-noise down-converter applied to multi-path satellite receiver, and satellite receiving system

ActiveCN105703788AReduce laying costsReduce installation costsPolarisation/directional diversityMulti-frequency-changing modulation transferenceLow noiseFrequency changer

The invention discloses a low-noise down-converter applied to a multi-path satellite receiver, and a satellite receiving system. The low-noise down-converter is pre-provided with N user frequency bands. Meanwhile, the frequencies of satellite signals, that are 10.7 to 12.75 GHz, are reduced to be 300-2350 MHz, so that the satellite signals are converted into IF signals through the frequency-reducing process. After that, IF signals corresponding to specified television programs in the specified television program information are picked out of the above IF signals of 300-2350 MHz in frequency. Then, the IF signals corresponding to the specified television programs are mixed with controllable intrinsic signals to be converted into secondary frequency-conversion signals, wherein the frequency range of the secondary frequency-conversion signals is within one idle user band frequency range of N user frequency bands. The N user frequency bands are formed through uniformly dividing a total receiving frequency band of the satellite receiver, and the frequencies of the controllable intrinsic signals are calculated based on the center frequencies of specified television programs and the center frequency of the above idle user band frequency. Finally, the secondary frequency-conversion signals are outputted via a coaxial cable interface. According to the technical scheme of the invention, at most N paths of mutually independent television program signals can be outputted at the same time. Meanwhile, the cable laying cost and the user installation cost are saved. Moreover, the installation complexity of a system outdoor part is lowered.

Owner:EARDA TECH CO LTD

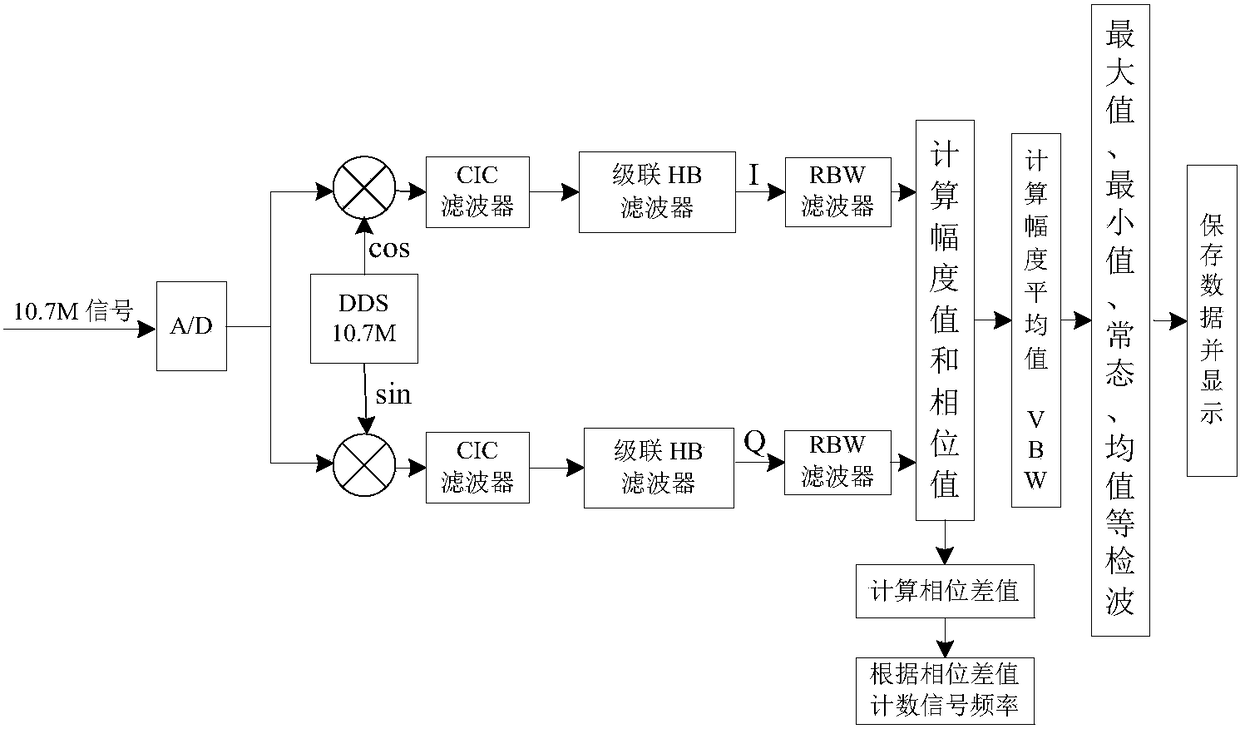

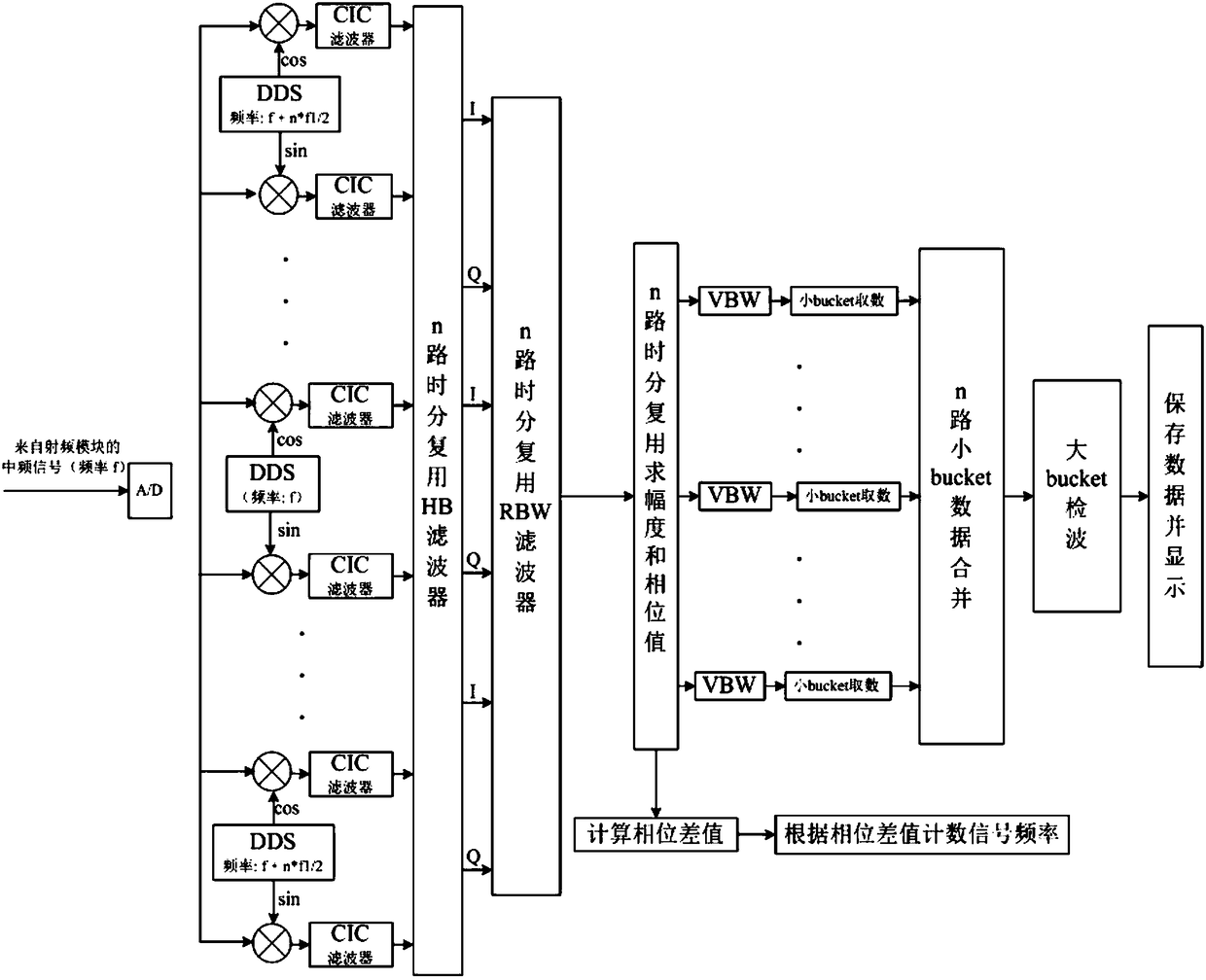

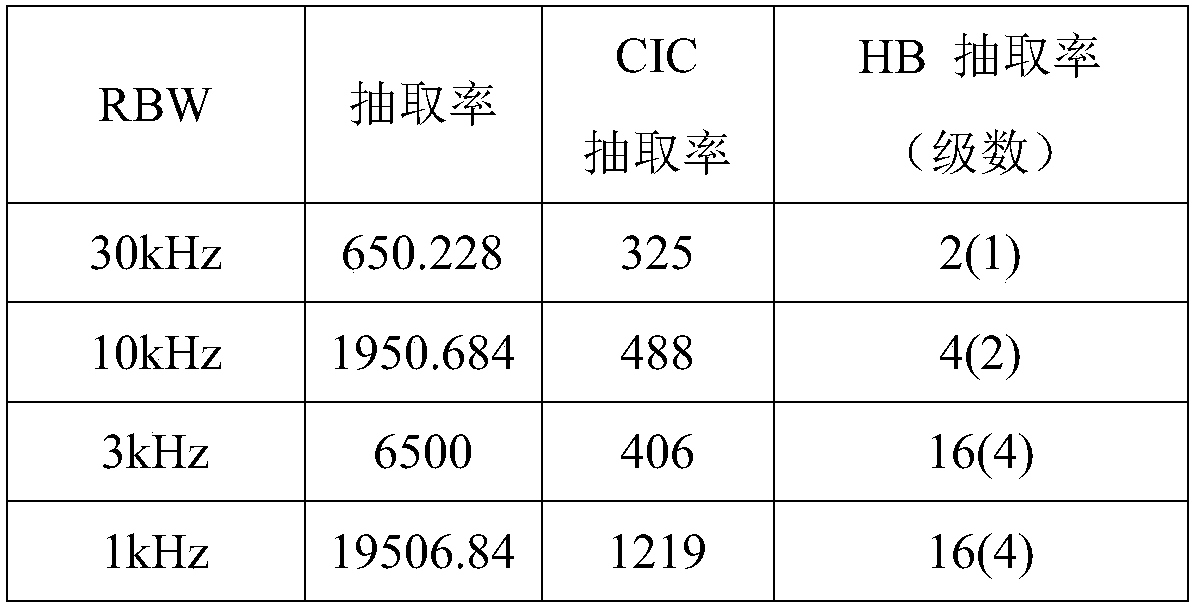

Frequency spectrum detector rapid frequency sweeping system and method

The invention discloses a frequency spectrum detector rapid frequency sweeping system and method; a simulation signal outputted by a radio frequency module is sampled by an AD and mixed with DDS, wherein the frequency f of the DDS in the middle path is same with the central frequency outputted by the radio frequency module; frequencies of other DDSs are respectively set as f+ / - (n-1)*f1 / 2, i.e., symmetrically arranged, wherein f1 refers to the sweeping width of each bucket; a CIC filter and a HB filter can finish data extraction and underclocking; a RBW filter can finish waveform formation; acordic module is directly invoked to solve an amplitude value and a phase value, a signal is smoothed by a VBW module, and the small bucket is fetched; a small bucket data merging module can merge thefetched data of n paths of small buckets into one path according to a frequency big-to-small principle; various demodulations can be realized under large bucket signal control, and the data is finally sent to a display module.

Owner:NANJING GUORUI ANTAIXIN TECH

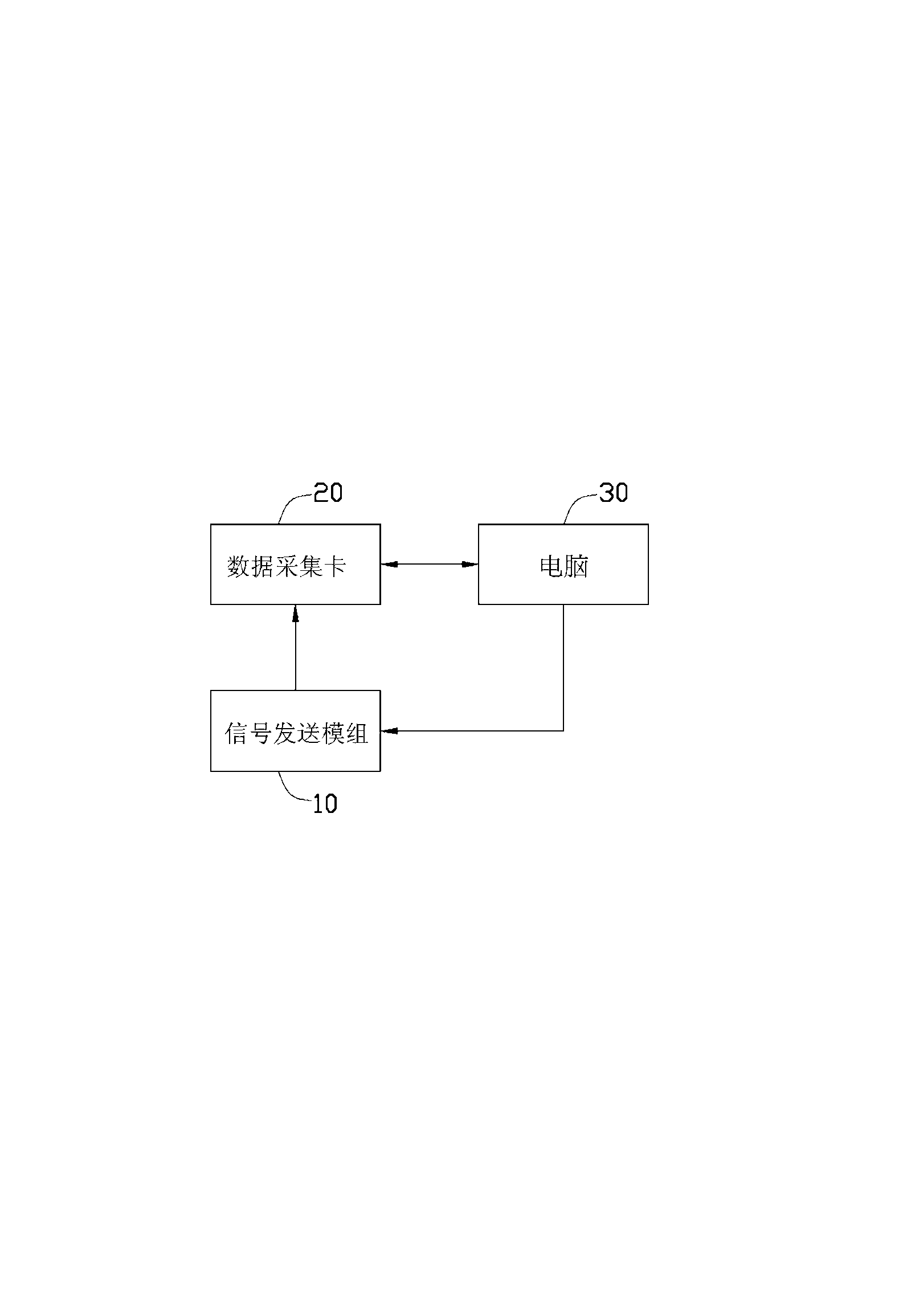

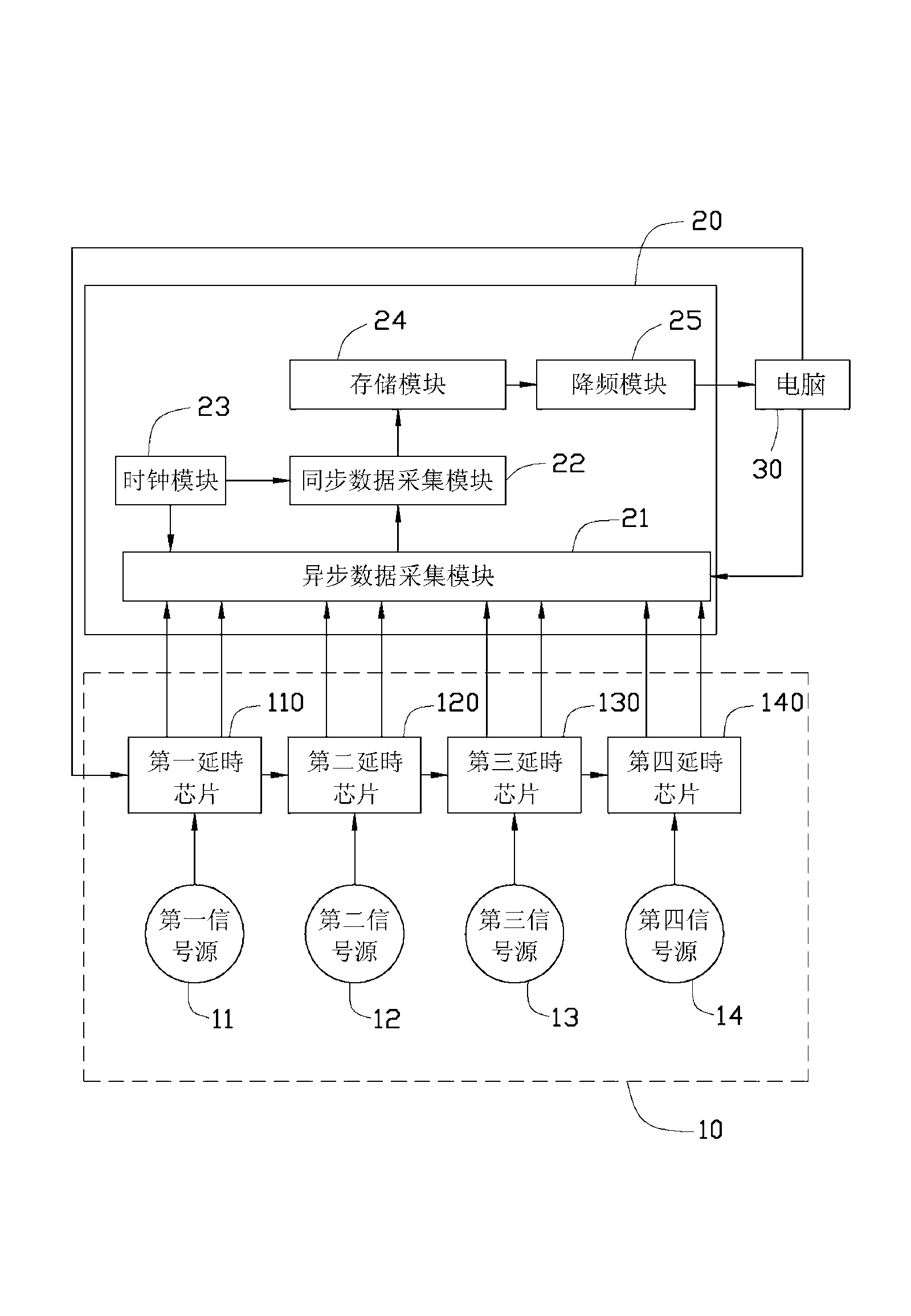

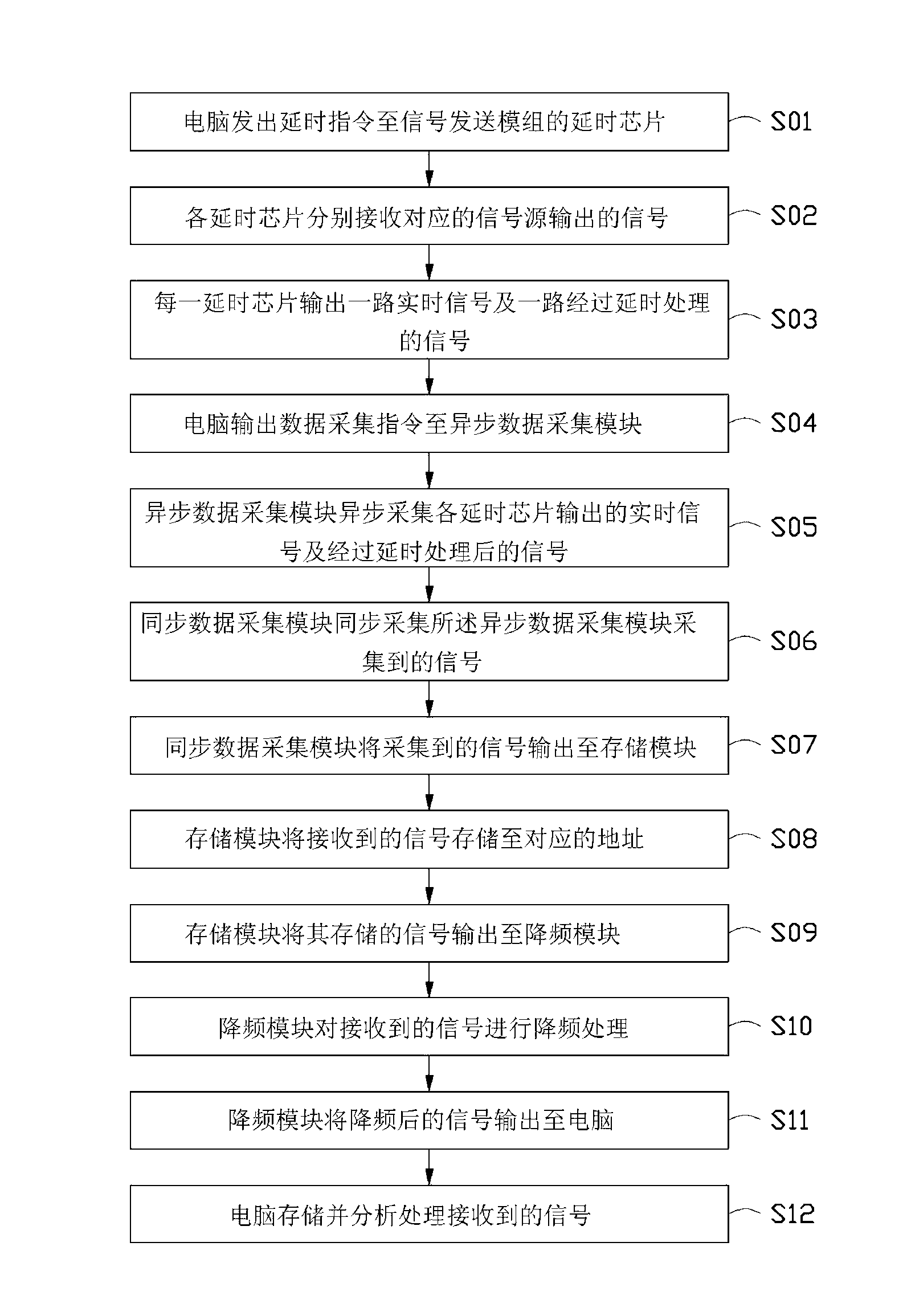

Signal collection system and method

InactiveCN103136147AImprove accuracyAvoid signal distortionElectric digital data processingComputer hardwareCollection system

A signal collection system comprises a signal sending module, a computer and a data collection card, wherein the data collection card is connected between the signal sending module and the computer, the signal sending module comprises at least one signal source and a delayed chip which is connected with the signal source, the delayed chip outputs a signal received from the signal source to the data collection card in real time and outputs the signal to the data collection card again after delayed process is carried out on the signal received from the signal source, the data collection card comprises an underclocking module, and the underclocking module carries out underclocking process on the signal collected by the data collection card and outputs the signal to the computer. The invention further discloses a signal collection method based on the signal collection system. The signal collection system and the method can collect data in a double mode, carry out the underclocking process on high-speed and high-frequency signals, and accordingly reduce the probability of data loss.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

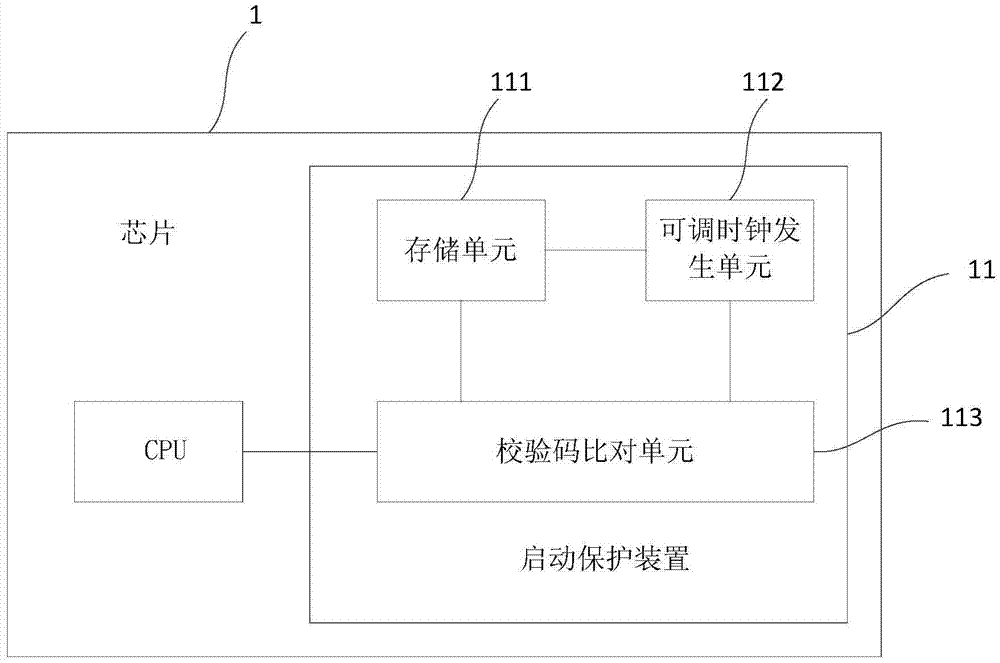

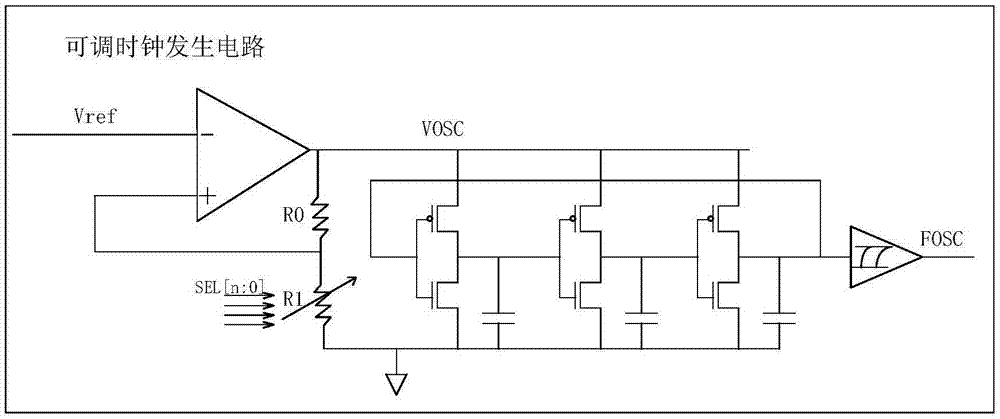

Chip, starting protection device and method of chip

ActiveCN106919857AGuaranteed stabilityGuaranteed work efficiencyInternal/peripheral component protectionElectricityEngineering

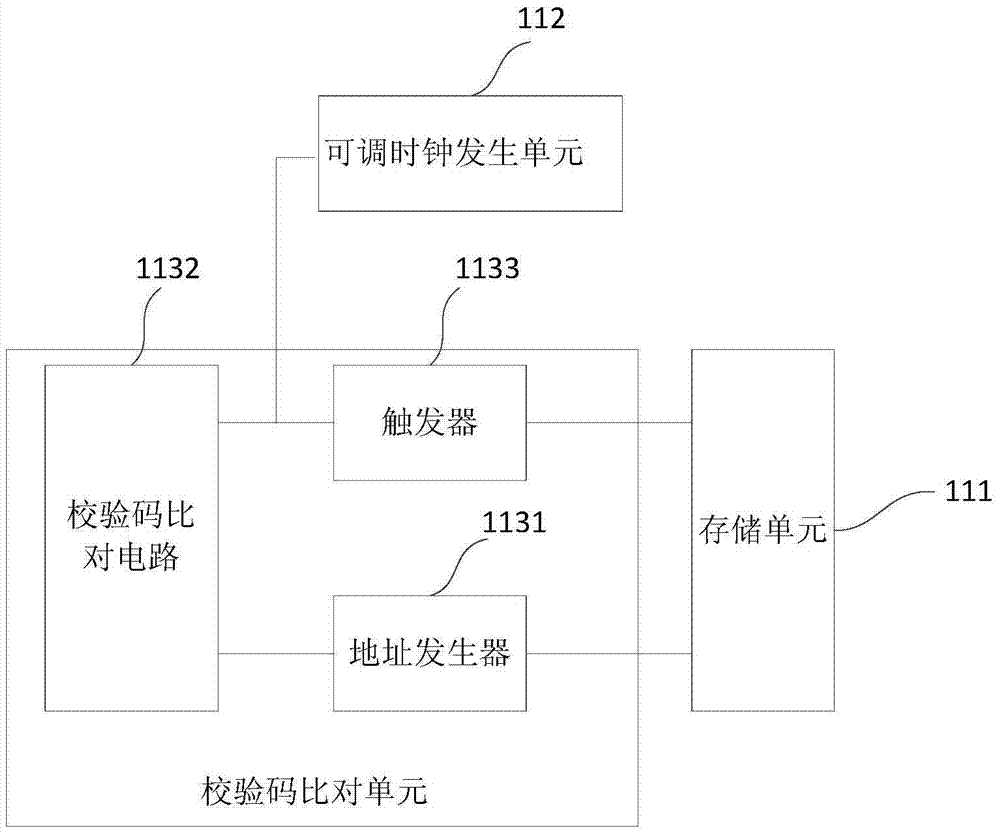

The invention provides a chip, a starting protection device and a starting protection method of the chip, wherein the protection device comprises a storage unit, an adjustable clock generation unit and a check code comparison unit; the storage unit is stored with a first check code; the adjustable clock generation unit is used for outputting a clock signal of a preset frequency after power on, and reducing the frequency of the output clock signal according to a received frequency reduction command; the check code comparison unit is connected with the adjustable clock generation unit and the storage unit, and is used for comparing the first check code stored in the storage unit with a preset second check code, if consistent, triggering each piece of working hardware in the chip to start according to the clock signal of the current frequency, and if inconsistent, sending the frequency reduction command to the adjustable clock generation unit. According to the chip, the starting protection device and the starting protection method of the chip, the chip automatically adapts a working method of an external environment under the conditions of guaranteeing maximum performances of a system and also guaranteeing high stability of the system.

Owner:SHANGHAI IND U TECH RES INST

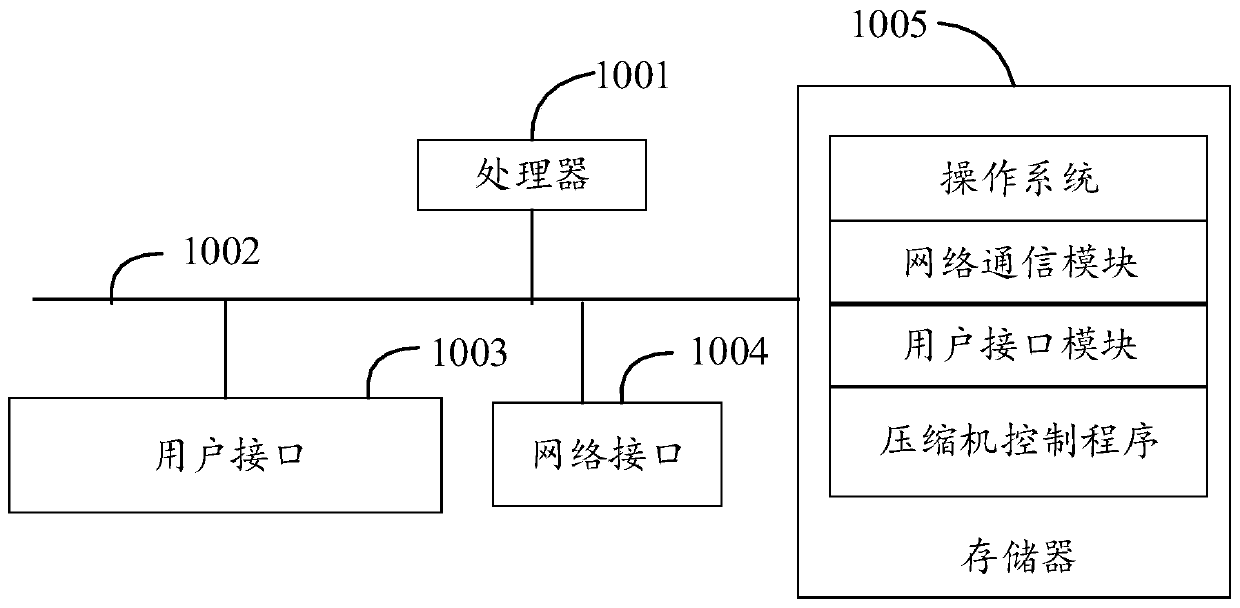

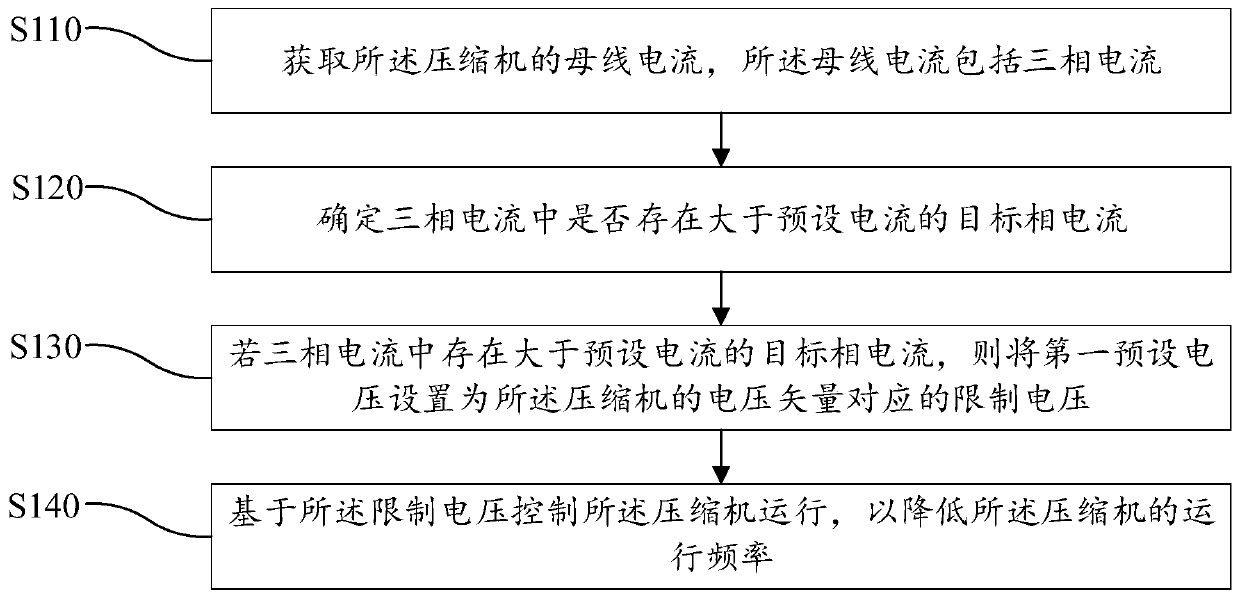

Compressor control method and device and computer readable storage medium

ActiveCN110410308AReduce operating frequencyRealize automatic frequency reductionPump testingPositive displacement pump componentsPhase currentsVoltage vector

The invention discloses a compressor control method. The method comprises the following steps that a bus current of the compressor is acquired, wherein the bus current comprises a three-phase current;whether a target phase current greater than a preset current exists in the three-phase current is determined, and if the target phase current greater than the preset current exists in the three-phasecurrent, a first preset voltage is set as a limit voltage corresponding to the voltage vector of the compressor; and the compressor is controlled to operate on the basis of the limit voltage so as toreduce the operation frequency of the compressor. The invention further discloses a compressor control device and a computer readable storage medium. According to the compressor control method, the automatic frequency reduction of the compressor can be realized before the compressor is subjected to an over-current, and the situation that the compressor is subjected to the over-current due to thefact that the frequency of the compressor is not timely reduced when the bus voltage is reduced.

Owner:GD MIDEA HEATING & VENTILATING EQUIP CO LTD +1