Integrated passive device and manufacture method thereof

A technology that integrates passive devices and manufacturing methods. It is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc. It can solve the problems that cannot meet the application requirements and the range of interconnection capacitance is small, so as to achieve easy adjustment and improve the electric capacity. Effect of capacity, area improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

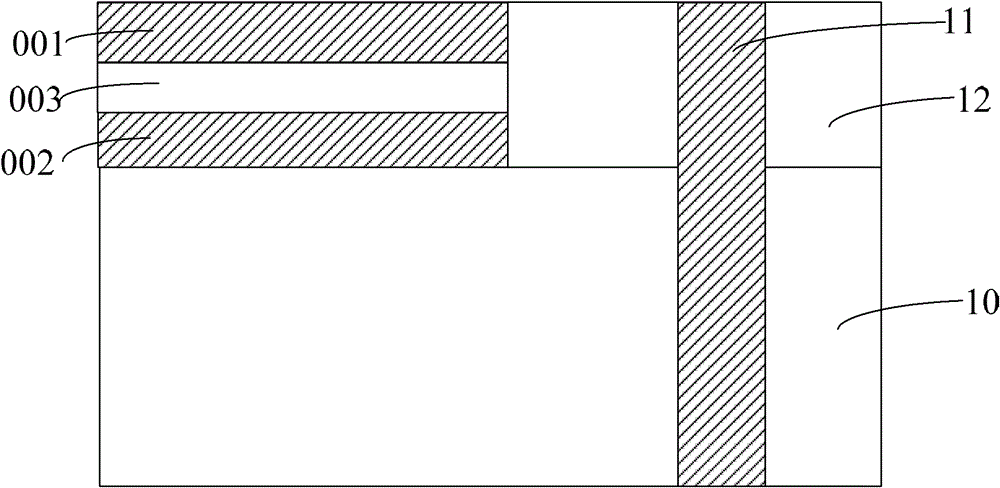

[0041] Since the existing interconnection capacitor is a parallel plate capacitor, the interconnection capacitor includes a metal layer-insulator layer-metal layer parallel to the surface of the semiconductor substrate, thereby forming an interconnection capacitor vertically conducted between chips.

[0042] Please combine figure 1 When the capacitance value of the capacitor to be formed is large, the facing area between the first electrode plate and the second electrode plate needs to be increased, but due to the limited area of the semiconductor substrate, the range of the capacitance value of the capacitor is limited. Moreover, since the thickness of the insulating layer is generally greater than 500 angstroms, the capacitance of the capacitor is relatively large.

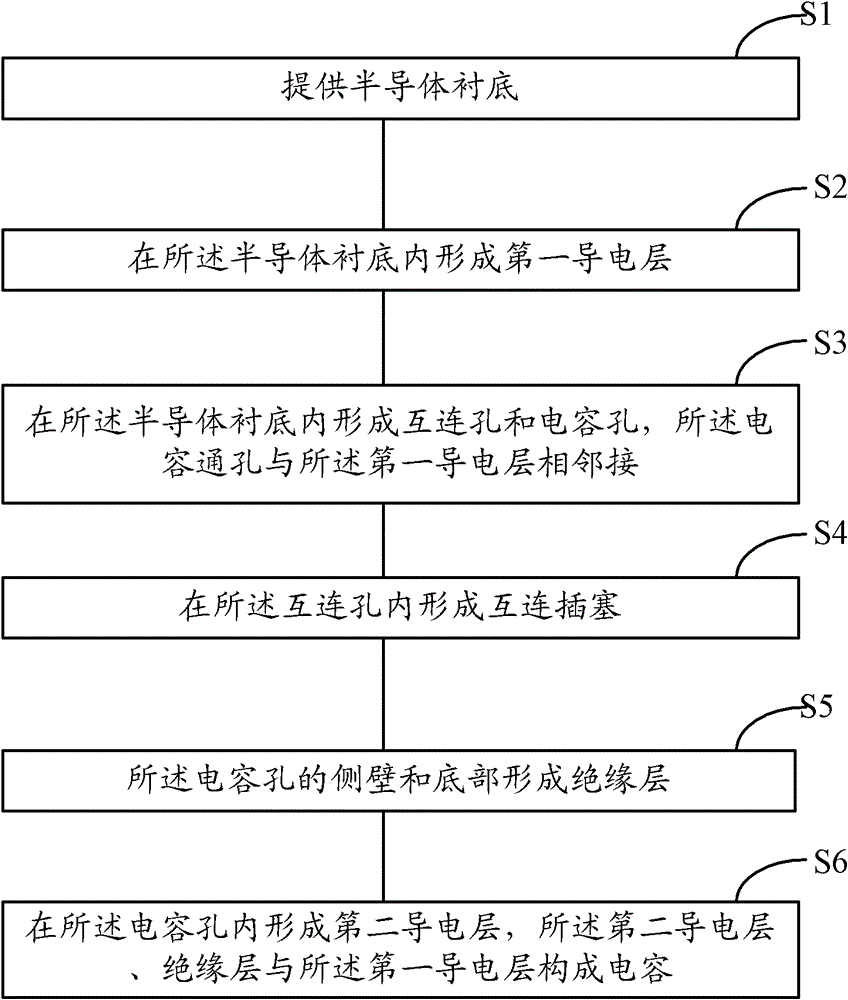

[0043] In order to solve the above problems, the embodiment of the present invention proposes a manufacturing method for integrated passive devices, please combine figure 2 Shown is a schematic flow chart of...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Depth | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More